多電平正交幅度調(diào)制MQAM(Multilevel QuadratureAmplitude Modulation)是一種振幅和相位相結(jié)合的高階調(diào)制方式,具有較高的頻帶利用率和較好的功率利用率。因?yàn)閱为?dú)使甩振幅和相位攜帶信息時(shí),不能最充分利用信號(hào)平面,這可由調(diào)制信號(hào)星座圖中信號(hào)矢量端點(diǎn)的分布直觀觀察到。多進(jìn)制振幅鍵控(MASK)調(diào)制時(shí),矢量端點(diǎn)在一條軸上分布;多進(jìn)制相位鍵控(MPSK)調(diào)制時(shí),矢量點(diǎn)在一個(gè)圓上分布。隨著進(jìn)制數(shù)M的增大,這些矢量端點(diǎn)之間的最小距離也隨之減少。因此,MQAM是一種高效的調(diào)制方式,被廣泛應(yīng)用于中、大容量數(shù)字微波通信系統(tǒng)、有線電視網(wǎng)絡(luò)高數(shù)據(jù)傳輸、衛(wèi)星通信等領(lǐng)域。本文首先介紹了MQAM調(diào)制解調(diào)的基本原理,然后以64QAM為例,介紹了一種全數(shù)字實(shí)現(xiàn)的調(diào)制系統(tǒng)結(jié)構(gòu)方案,并給出了解調(diào)器的具體FPGA實(shí)現(xiàn)方法及關(guān)鍵技術(shù)。

2 MQAM調(diào)制原理

MQAM(Multiple Quadrature Amplitude Modulation)多進(jìn)制正交幅度調(diào)制。多進(jìn)制正交幅度調(diào)制是在中、大容量數(shù)字微波通信系統(tǒng)中大量使用的一種載波控制方式。這種方式具有很高的頻譜利用率,在調(diào)制進(jìn)制數(shù)較高時(shí),信號(hào)矢量集的分布也較合理,同時(shí)實(shí)現(xiàn)起來也較方便。目前在SDH數(shù)字微波、LMDS等大容量數(shù)字微波通信系統(tǒng)中廣泛使用的64QAM、128QAM等均屬于這種調(diào)制方式。

所謂正交振幅調(diào)制,就是用兩個(gè)獨(dú)立的基帶波形對(duì)兩個(gè)相互正交的同頻載波進(jìn)行抑制載波的雙邊帶調(diào)制,利用這種已調(diào)信號(hào)在同一帶寬內(nèi)頻譜的正交性來實(shí)現(xiàn)兩路并行的數(shù)字信息傳輸。MQAM信號(hào)的一般表達(dá)式為:

式(1)由兩個(gè)相互正交的載波構(gòu)成,每個(gè)載波被一組離散的振幅{Am),{Bm)所調(diào)制,故稱這種調(diào)制方式為正交振幅調(diào)制。式中T為碼元寬度,m=1,2,…,L,L為Am和Bm的電平數(shù)。MQAM中Am和Bm振幅可以表示成:

式中:A是固定的振幅,dm,em由輸入數(shù)據(jù)確定,dm,em決定了已調(diào)MQAM信號(hào)在信號(hào)空間中的坐標(biāo)點(diǎn)。在調(diào)制過程中,載波的振幅與相位都發(fā)生了變化,因此,已調(diào)信號(hào)矢量星座圖中每一個(gè)坐標(biāo)點(diǎn)代表了一種編碼組合,同時(shí)也代表了正交信號(hào)矢量合成后的不同的相位及電平,第i個(gè)信號(hào)可用數(shù)學(xué)描述為:

因此每一個(gè)坐標(biāo)點(diǎn)也由Ai和φ i惟一確定。

3 64QAM調(diào)制器系統(tǒng)設(shè)計(jì)

圖1給出了全數(shù)字實(shí)現(xiàn)的64QAM調(diào)制器的電路原理結(jié)構(gòu)。除D/A變換外,每個(gè)功能模塊都用FPGA實(shí)現(xiàn)。擾碼、串并轉(zhuǎn)換和差分編碼采用原理圖的方法進(jìn)行設(shè)計(jì),電平轉(zhuǎn)換及星座圖映射采用查表法(LUT)進(jìn)行設(shè)計(jì)。本設(shè)計(jì)的難點(diǎn)為成形濾波器和基于DDS的正交調(diào)制器實(shí)現(xiàn),下面重點(diǎn)描述成形濾波器和基于DDS的正交調(diào)制器的實(shí)現(xiàn)方法。

一塊DDS芯片中主要包括頻率控制寄存器、高速相位累加器和正弦計(jì)算器三個(gè)部分(如Q2220)。頻率控制寄存器可以串行或并行的方式裝載并寄存用戶輸入的頻率控制碼;正弦計(jì)算器則對(duì)該相位值計(jì)算數(shù)字化正弦波幅度(芯片一般通過查表得到)。DDS芯片輸出的一般是數(shù)字化的正弦波,因此還需經(jīng)過高速D/A轉(zhuǎn)換器和低通濾波器才能得到一個(gè)可用的模擬頻率信號(hào)。

3.1 成形濾波器的設(shè)計(jì)

為了讓信號(hào)在帶限的信道中傳輸,提高頻譜利用率,通常在發(fā)送端把信號(hào)經(jīng)過成形濾波器進(jìn)行帶限,由此就會(huì)引入碼間干擾。為有效地減少碼間干擾,按照最佳接收理論,收發(fā)基帶濾波器應(yīng)共軛匹配,設(shè)計(jì)時(shí)收發(fā)基帶濾波器采用均方根升余弦滾降濾波器即能滿足要求。

在實(shí)際電路設(shè)計(jì)中采用具有線性相位的FIR濾波器來實(shí)現(xiàn)均方根升余弦滾降特性的成形濾波器。一個(gè)N階FIR濾波器的差分方程表達(dá)式為:

線性相位的FIR濾波器的系數(shù)是偶對(duì)稱或奇對(duì)稱的,利用系數(shù)的對(duì)稱性可減少乘法器的數(shù)量,本系統(tǒng)采用N為偶數(shù)且系數(shù)偶對(duì)稱的線性相位的FIR濾波器。濾波器系數(shù)是一個(gè)固定的值,根據(jù)均方根升余弦的沖擊響應(yīng)特性,利用Matlab軟件可直接生成FIR數(shù)字濾波器系數(shù)hk(k=0,1,…,N-1)。所以濾波器的乘法都是固定系數(shù)的乘法。

本設(shè)計(jì)采用分布式算法(DA)原理,利用FPGA查找表代替乘法器來實(shí)現(xiàn)FIR濾波器,其基本思想如下:

假設(shè)輸入信號(hào)數(shù)據(jù)位為B位,則濾波器在n時(shí)刻的第k個(gè)輸入為:

從式(5)可以看出,F(xiàn)IR濾波器中乘加單元的運(yùn)算是算法核心。如果建立一個(gè)查找表(Look Up Table,LUT),表中數(shù)據(jù)由所有固定系數(shù)(h0,h1,…,hN-1)的所有加的組合構(gòu)成(和用sumb表示,6∈『0,B-1』),那么,用N位輸入數(shù)據(jù)構(gòu)成的N位地址去尋址LUT,如果N位都為1,則LUT的輸出是N位系數(shù)的和,如果N位中有0,則其對(duì)應(yīng)的系數(shù)將從和中去掉。這樣乘加運(yùn)算就變成了查表操作。整數(shù)乘以2b可以通過左移6位實(shí)現(xiàn)。

對(duì)于本系統(tǒng),碼元速率為25.92 Mbaud,滾降系數(shù)選取為0.5,抽頭個(gè)數(shù)取N=16,抽頭系數(shù)精度取10 b,輸入數(shù)據(jù)為4 b,輸出精度取9 b。仿真結(jié)果如圖2所示。

從圖2可以看出:碼元速率為25.92 Mbaud的基帶信號(hào)經(jīng)成形濾波后,頻譜被限制在20 MHz范圍內(nèi)。

3.2 正交調(diào)制器的設(shè)計(jì)

本實(shí)驗(yàn)裝置主要由波形產(chǎn)生電路以及正交調(diào)制電路兩個(gè)模塊組成。硬件方面主要使用了單片機(jī)和FPGA兩種可編程的器件聯(lián)合實(shí)現(xiàn)的,單片機(jī)處理開關(guān)掃描和顯示電路,F(xiàn)PGA實(shí)現(xiàn)波形產(chǎn)生與輸出選擇,具有很大的靈活性和開放性。

本實(shí)驗(yàn)裝置的單片機(jī)選用的是Atmel公司的單片機(jī)AT89C55WD,單片機(jī)的數(shù)據(jù)地址復(fù)用口P0全部與FPGA相連,此外地址的高三位線也與FPGA相連,這主要是為了讓FPGA承擔(dān)為單片機(jī)地址譯碼選通外設(shè)的作用。單片機(jī)的WR、RD和ALE也與FPGA相連,這是為了保證單片機(jī)與FPGA的通信時(shí)的時(shí)序問題。單片機(jī)的IO口P1口的8個(gè)I/O口全部接到開關(guān)上,使用獨(dú)立式按鍵結(jié)構(gòu)中的查詢方式。按鍵輸入低電平有效,上拉電阻保證按鍵斷開時(shí),I/O口為高電平。

本實(shí)驗(yàn)裝置使用四只數(shù)碼管作為顯示,選用共陰電路。因單片機(jī)的I/O口有限,故使用串行移位寄存器74HC595串行連接以控制顯示器的顯示輸出。在單片機(jī)只需要用三個(gè)I/O口分別與74HC595的14(SER)腳,11(SRCLK)腳和12(RCLK)腳。鑒于篇幅限制,只畫了兩片74HC595和LED,實(shí)現(xiàn)電路中是四片(74HC595的工作時(shí)序以及工作狀態(tài)參見相關(guān)資料)。

經(jīng)成形濾波后的兩路基帶信號(hào)分別對(duì)DDS(DirectDigital Synthesizer)產(chǎn)生的兩路正交的載波進(jìn)行調(diào)制,然后進(jìn)行矢量相加形成調(diào)制信號(hào)輸出。

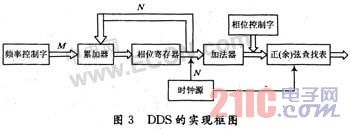

DDS的基本原理是利用采樣定理,利用查找表法產(chǎn)生波形。相位累加器是DDS系統(tǒng)的核心部分,每來一個(gè)時(shí)鐘脈沖,累加器將頻率控制字M與相位寄存器輸出的累加相位數(shù)據(jù)相加,把相加后的結(jié)果送至相位寄存器的數(shù)據(jù)輸入端;相位寄存器將累加器在上一個(gè)時(shí)鐘作用后所產(chǎn)生的新相位數(shù)據(jù)反饋到累加器的輸入端,以使累加器在下一個(gè)時(shí)鐘的作用下繼續(xù)與頻率控制數(shù)據(jù)相加。當(dāng)累加器累加滿量時(shí)就會(huì)產(chǎn)生一次溢出,完成一個(gè)周期性的動(dòng)作,這個(gè)周期就是DDS合成信號(hào)的一個(gè)頻率周期,累加器的溢出頻率就是DDS輸出的信號(hào)頻率。

用相位累加器輸出的數(shù)據(jù)作為波形存儲(chǔ)器(ROM)的相位取樣地址,這樣就可以把存儲(chǔ)在波形存儲(chǔ)器內(nèi)的波形抽樣值經(jīng)查找表查出,完成相位到幅值轉(zhuǎn)換。ROM設(shè)計(jì)的關(guān)鍵問題是進(jìn)行初始化,就是將正弦波的二進(jìn)制幅度碼按一定的格式輸入到存儲(chǔ)器初始化(。mif)文件,此文件可以C語言或者M(jìn)atlab語言程序生成。

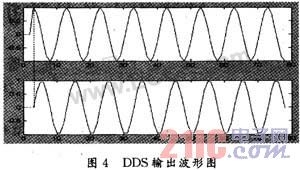

DDS系統(tǒng)輸出信號(hào)的頻率為f0=fclk×M/2N,頻率分辨率為△f=fclk/2N,當(dāng)M=2N-1時(shí),DDS最高的基波合成頻率為f0max=fclk/2。對(duì)于本系統(tǒng),時(shí)鐘頻率fclk=155.520 MHz,N取12。仿真結(jié)果如圖4所示。

4 系統(tǒng)設(shè)計(jì)與仿真

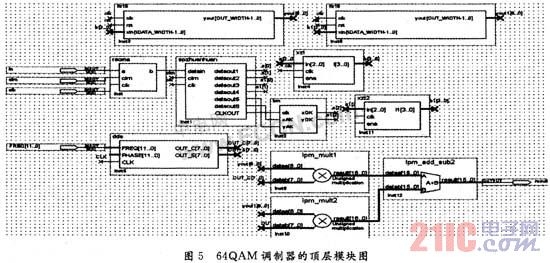

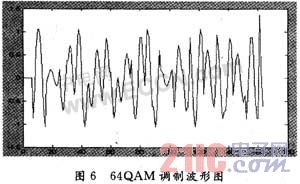

根據(jù)以上各模塊單元的設(shè)計(jì),構(gòu)成64QAM調(diào)制器的頂層文件如圖5所示。運(yùn)用QuartusⅡ及Matlab軟件實(shí)現(xiàn)64QAM調(diào)制器仿真,仿真結(jié)果如圖6所示。

仿真可以按不同原則分類:①按所用模型的類型分為物理仿真、計(jì)算機(jī)仿真、半實(shí)物仿真;②按所用計(jì)算機(jī)的類型(模擬計(jì)算機(jī)、數(shù)字計(jì)算機(jī)、混合計(jì)算機(jī))分為模擬仿真、數(shù)字仿真和混合仿真;③按仿真對(duì)象中的信號(hào)流分為連續(xù)系統(tǒng)仿真和離散系統(tǒng)仿真;④按仿真時(shí)間與實(shí)際時(shí)間的比例關(guān)系分為實(shí)時(shí)仿真、超實(shí)時(shí)仿真和亞實(shí)時(shí)仿真;⑤按對(duì)象的性質(zhì)分為宇宙飛船仿真、化工系統(tǒng)仿真、經(jīng)濟(jì)系統(tǒng)仿真等。

5 結(jié)語

本文介紹了用FPGA實(shí)現(xiàn)全數(shù)字高階QAM調(diào)制器的思想和方法,采用原理圖和Verilog語言,用可編程芯片StratixⅡ系列中的EP2S30F484C3實(shí)現(xiàn)了整個(gè)設(shè)計(jì),結(jié)果表明符合設(shè)計(jì)要求。為進(jìn)一步的研究和設(shè)計(jì)全數(shù)字高階QAM系統(tǒng)打下了良好的基礎(chǔ)。