近年來(lái),隨著現(xiàn)場(chǎng)可編程門陣列(FPGA)在雷達(dá)信號(hào)處理中的廣泛應(yīng)用以及FPGA芯片技術(shù)的發(fā)展,為大家提供了一種較好解決數(shù)字脈壓的途徑。其中,利用IP核設(shè)計(jì)FPGA數(shù)字系統(tǒng)成為一種趨勢(shì),這些知識(shí)產(chǎn)權(quán)核可以大大簡(jiǎn)化FPGA的設(shè)計(jì),加快設(shè)計(jì)速度,縮短研發(fā)周期,而且經(jīng)過(guò)不斷的優(yōu)化,IP核具有了更好的精度和更快的運(yùn)算速度,實(shí)際的工程應(yīng)用效果很好。

本文以此為出發(fā)點(diǎn),對(duì)線性調(diào)頻信號(hào)的脈沖壓縮進(jìn)行了研究,仿真,并提出了一種采用IP核設(shè)計(jì)脈沖壓縮的方法。

1 線性調(diào)頻信號(hào)的脈沖壓縮

1.1 脈沖壓縮的實(shí)現(xiàn)原理

脈沖壓縮可以采用“共軛濾波器對(duì)”的匹配濾波法和相關(guān)處理法。匹配濾波法對(duì)應(yīng)于頻域相乘,相關(guān)處理法對(duì)應(yīng)于時(shí)域卷積。依據(jù)傅里葉變換理論:時(shí)域卷積等效于頻域乘積。因此這兩種方法是等效的,只是一種方法在頻域?qū)崿F(xiàn),而另一種方法在時(shí)域?qū)崿F(xiàn)。考慮到運(yùn)算量,工程上一般采用頻域法,可以利用快速FFT算法提高計(jì)算速度,然后將雷達(dá)回波與匹配濾波系數(shù)的頻域響應(yīng)相乘,再經(jīng)過(guò)IFFT處理得到脈沖壓縮結(jié)果。匹配濾波系數(shù)只與發(fā)射信號(hào)有關(guān),預(yù)先可知,一般預(yù)先算好。

1.2 線性調(diào)頻信號(hào)的脈沖壓縮

一般在時(shí)寬帶寬積BT>30時(shí),可以近似認(rèn)為線性調(diào)頻信號(hào)具有矩形振幅頻譜,因此其匹配濾波器也應(yīng)該具有矩形帶通振幅特性。線性調(diào)頻信號(hào)的匹配濾波器的近似頻率特性可描述為:

可以看出,線性調(diào)頻的脈沖壓縮結(jié)果具有sine函數(shù)形狀。主瓣寬度為1/B,第一旁瓣電平約為-13.2 dB。如果是多目標(biāo)環(huán)境,較大的旁瓣會(huì)埋沒(méi)附近的小目標(biāo)信號(hào),為了抑制旁瓣,可以采用加權(quán)技術(shù)。其實(shí)質(zhì)就是對(duì)信號(hào)進(jìn)行失配處理以抑制旁瓣,其副作用是使輸出信號(hào)的主瓣降低并展寬。

1.3 理論仿真

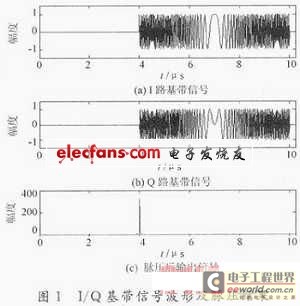

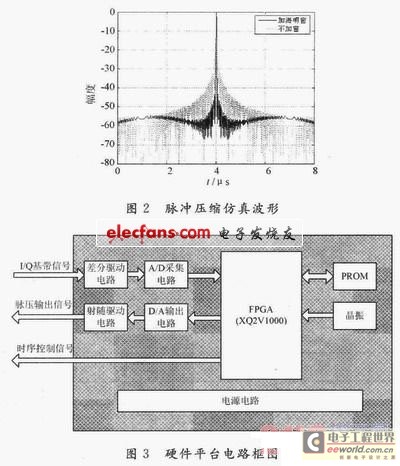

設(shè)匹配濾波器的輸入信號(hào)是線性調(diào)頻I/Q基帶信號(hào),帶寬為40 MHz,采樣頻率為100 MHz,脈沖寬度為6μs,信號(hào)幅度為1,通過(guò)Matlab對(duì)其進(jìn)行脈沖壓縮仿真。圖1中是輸入的I/Q基帶信號(hào)波形以及脈壓后的結(jié)果。從圖中可以看到脈壓后產(chǎn)生的窄脈沖,波形具有sine函數(shù)性質(zhì),除主瓣外,時(shí)間軸上還有延伸的一串副瓣;還可看出,經(jīng)過(guò)海明加權(quán)后,第一副瓣比主瓣下降約40 dB,但主瓣寬度也有相應(yīng)的展寬。如圖2所示。

2 脈沖壓縮系統(tǒng)設(shè)計(jì)

該系統(tǒng)的主要功能是對(duì)線性調(diào)頻I/Q基帶信號(hào)進(jìn)行高速采集,然后在FPGA中實(shí)現(xiàn)線性調(diào)頻信號(hào)的脈沖壓縮,之后通過(guò)D/A變換器輸出脈壓結(jié)果,監(jiān)測(cè)脈壓后的波形。

關(guān)鍵字:調(diào)頻信號(hào) IP核 脈沖壓縮

2.1 系統(tǒng)硬件平臺(tái)

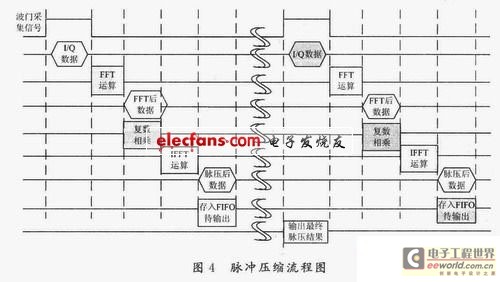

該系統(tǒng)硬件平臺(tái)主要包括:差分驅(qū)動(dòng)電路,A/D采集電路、FPGA電路、晶振等電路、電路結(jié)構(gòu)框圖如圖3所示。

FPGA采用的是Xilinx公司的芯片XQ2V1000,其配置芯片為Xilinx公司的PROM芯片XQ18V04,以主動(dòng)串行方式對(duì)FPGA進(jìn)行上電配置。差分驅(qū)動(dòng)電路選用ADI公司的AD8138,A/D、D/A電路分別為ADI公司的14位高速模/數(shù)轉(zhuǎn)換芯片ADS5500和14位高速數(shù)/模轉(zhuǎn)換芯片DAC5675A。硬件電路的設(shè)計(jì)注重細(xì)節(jié):I/Q兩通道傳輸線設(shè)計(jì)時(shí)保證線長(zhǎng)相等,使得I/Q時(shí)延帶來(lái)的相位誤差一致;采用DCI(DigitaUy Controlled Impe-dance)端接技術(shù),在FPGA的每個(gè)bank上外接兩個(gè)參考電阻來(lái)對(duì)該bank的每個(gè)I/O管腳實(shí)現(xiàn)端接,減少外接電阻的數(shù)量,實(shí)現(xiàn)阻抗匹配,提高系統(tǒng)的穩(wěn)定性;做好電源濾波,對(duì)元器件進(jìn)行合理布局,布線,對(duì)模擬信號(hào)和數(shù)字信號(hào)進(jìn)行有效隔離,減小信號(hào)間串?dāng)_。

2.2 軟件設(shè)計(jì)流程

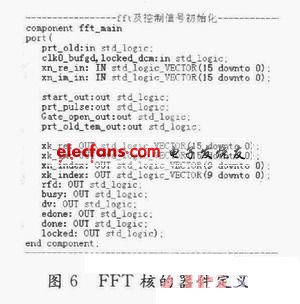

整個(gè)脈沖壓縮處理在時(shí)間上是順序的,是典型的數(shù)據(jù)流驅(qū)動(dòng)的系統(tǒng),即先進(jìn)行FFT,復(fù)乘然后是IFFT及FIFO輸出,脈沖壓縮的總時(shí)序關(guān)系見(jiàn)圖4。該系統(tǒng)實(shí)現(xiàn)1 024點(diǎn)的脈沖壓縮,算法上采用基于IP核的設(shè)計(jì)方法。主要用到了FFT核,乘法器核以及單口Block Memory核,這些IP核的應(yīng)用及脈沖壓縮的具體實(shí)現(xiàn)如下所述。

2.2.1 FFT運(yùn)算

對(duì)于長(zhǎng)度為N的時(shí)域序列X(n)的離散傅里葉變換為X(k):

FFT算法主要是利用旋轉(zhuǎn)因子exp(-j2πnk/N)的周期性和對(duì)稱性的特點(diǎn)進(jìn)行改進(jìn)的算法,可以有效地減小運(yùn)算量。Xilinx公司的FFT核利用Cooley-Tukey算法實(shí)現(xiàn)FFT/IFFT運(yùn)算,最高支持216點(diǎn)長(zhǎng)度的運(yùn)算,可以實(shí)現(xiàn)流水線型、基4、基2三種結(jié)構(gòu),蝶形運(yùn)算后可選擇對(duì)數(shù)據(jù)順序輸出還是倒序輸出,對(duì)IP核進(jìn)行不同的配置,可以實(shí)現(xiàn)資源和運(yùn)算速度的最優(yōu)化。在此選用基4蝶形運(yùn)算,對(duì)于1 024點(diǎn)數(shù)據(jù),需要5級(jí)蝶形運(yùn)算。

Xilinx公司的FFT核的參數(shù)通過(guò)GUI界面(見(jiàn)圖5)進(jìn)行設(shè)置,可設(shè)置的參數(shù)包括FFT點(diǎn)數(shù),運(yùn)算實(shí)施方法,輸入數(shù)據(jù)位數(shù)等,設(shè)置完畢后點(diǎn)擊Generate可即時(shí)生成代碼。

硬件描述語(yǔ)言采用VHDL,使用時(shí)程序中要對(duì)器件初始化并進(jìn)行定義,F(xiàn)FT核的器件定義語(yǔ)句見(jiàn)圖6。

2.2.2 匹配濾波系數(shù)產(chǎn)生

根據(jù)匹配濾波理論,對(duì)于一個(gè)確定的輸入信號(hào),匹配濾波系數(shù)就是這個(gè)輸入信號(hào)的頻譜的復(fù)共軛,系數(shù)可以通過(guò)Matlab預(yù)先計(jì)算出來(lái)并以二進(jìn)制的文件格式進(jìn)行存儲(chǔ)。此處計(jì)算時(shí)可以進(jìn)行加權(quán)處理,在系數(shù)中乘以窗函數(shù)即可。

通過(guò)Xilinx公司的單口Block Memory核,可以把Matlab產(chǎn)生的存儲(chǔ)文件加載進(jìn)去。當(dāng)程序運(yùn)行時(shí),根據(jù)使能控制信號(hào),把匹配濾波系數(shù)數(shù)據(jù)(1 024點(diǎn))依次讀取出來(lái),送入乘法器進(jìn)行后續(xù)運(yùn)算。BlockMemory核的參數(shù)設(shè)置通過(guò)GUI界面進(jìn)行,可即使生成代碼。

2.2.3 乘法運(yùn)算

乘法運(yùn)算部分完成FFT后數(shù)據(jù)與匹配濾波系數(shù)數(shù)據(jù)的復(fù)數(shù)乘法運(yùn)算。根據(jù)復(fù)數(shù)的乘法規(guī)則。

(A+aj)(B+bj)=(AB-ab)+(Ab+aB)j

兩個(gè)復(fù)數(shù)的乘法運(yùn)算實(shí)際上包括了4個(gè)實(shí)數(shù)的乘法運(yùn)算,因此,此部分的設(shè)計(jì)用到了4個(gè)乘法器核。Xilinx公司的乘法器核支持補(bǔ)碼運(yùn)算,可輸入A,B兩路數(shù)據(jù),每路的輸入數(shù)據(jù)長(zhǎng)度可達(dá)64 b。乘法器核的參數(shù)設(shè)置也是通過(guò)GUI界面進(jìn)行,可即使生成代碼。

2.2.4 IFFT運(yùn)算

IFFT運(yùn)算的處理單元和FFT的處理單元采用相同的結(jié)構(gòu)來(lái)實(shí)現(xiàn)。具體的實(shí)現(xiàn)方法是,在做IFFT運(yùn)算前,先交換輸入數(shù)據(jù)的實(shí)部和虛部,然后送入FFT處理單元按照FFT結(jié)構(gòu)進(jìn)行運(yùn)算,得到運(yùn)算結(jié)果后,再對(duì)其實(shí)部和虛部進(jìn)行交換,然后除以運(yùn)算點(diǎn)數(shù)1 024,就可以得到IFFT后脈沖壓縮的運(yùn)算結(jié)果。

關(guān)鍵字:調(diào)頻信號(hào) IP核 脈沖壓縮

2.3 工程軟件仿真

利用ModelSim仿真軟件首先對(duì)程序代碼進(jìn)行時(shí)序功能仿真,完成邏輯的綜合與實(shí)現(xiàn)之后再進(jìn)行布局布線后仿真,此時(shí)的仿真已基本接近真實(shí)情況。綜合后的仿真情況如圖7所示,仿真結(jié)果表明軟件運(yùn)行正常,可實(shí)現(xiàn)線性調(diào)頻信號(hào)的脈沖壓縮。

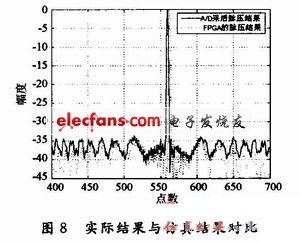

2.4 測(cè)試數(shù)據(jù)分析

完成程序編制及仿真之后,把軟件加載至FPGA中進(jìn)行全面測(cè)試。通過(guò)Chipscope軟件可以采集到A/D之后的I/Q線性調(diào)頻基帶信號(hào)數(shù)據(jù)以及經(jīng)過(guò)FPGA處理后的脈壓數(shù)據(jù),把A/D后采集到的數(shù)據(jù)放在Matlab中進(jìn)行理想的脈沖壓縮,與實(shí)際FPGA的脈壓結(jié)果進(jìn)行對(duì)比。從圖8中可以看出,兩種處理的結(jié)果是一致的,主副瓣比大約都在35 dB左右,主瓣寬度也基本相同。如圖8所示。

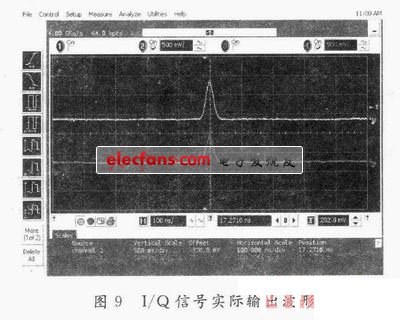

脈沖壓縮系統(tǒng)軟、硬件調(diào)試完畢之后,通過(guò)板上的D/A輸出可以直接監(jiān)測(cè)脈沖壓縮后的I/Q信號(hào)波形,如圖9所示。

3 結(jié)語(yǔ)

本文主要介紹了一種利用FPGA IP核設(shè)計(jì)線性調(diào)頻信號(hào)脈沖壓縮的方法,通過(guò)各種仿真與實(shí)際測(cè)試表明脈沖壓縮結(jié)果正確。這種基于IP核的模塊化設(shè)計(jì)方法非常靈活,參數(shù)的設(shè)置和修改方便,大大縮減了設(shè)計(jì)的開發(fā)周期。需要注意的是,雖然IP核的內(nèi)部結(jié)構(gòu)和實(shí)現(xiàn)功能已經(jīng)固定,但設(shè)計(jì)時(shí)也要結(jié)合算法原理和IP核的自身特點(diǎn)綜合考慮,對(duì)參數(shù)進(jìn)行合理設(shè)置,以便獲得硬件資源和運(yùn)算速度的最優(yōu)化。