基于Andes Core的ESL解決方案——AndESLive

晶心科技

摘要: 近年來,IC 設(shè)計(jì)正在向電子系統(tǒng)級(jí)(ESL,electronic system level)解決方案發(fā)展。多

家 EDA 公司以及 IP 供應(yīng)商都推出了各自的 ESL 開發(fā)工具。晶心科技(Andes technology)

是亞洲首家完全自主知識(shí)產(chǎn)權(quán) 32 位嵌入式處理器 IP 核(即 Andes core)的供應(yīng)商與系

統(tǒng)芯片開發(fā)平臺(tái)的設(shè)計(jì)公司。晶心科技為基于 Andes core 進(jìn)行 SoC 設(shè)計(jì)和開發(fā)的客戶提供了一套完整的 ESL 解決方案-AndESLive。本文將介紹 AndESLive 這套 ESL 開發(fā)工具是如何幫助客戶快速確定符合市場(chǎng)需求的最佳體系結(jié)構(gòu),并實(shí)現(xiàn)軟硬件并行工作以縮

減開發(fā)周期的目的。

Abstract:

Key words :

近年來,IC 設(shè)計(jì)正在向電子系統(tǒng)級(jí)(ESL,electronic system level)解決方案發(fā)展。多

家 EDA 公司以及 IP 供應(yīng)商都推出了各自的 ESL 開發(fā)工具。晶心科技(Andes technology)

是亞洲首家完全自主知識(shí)產(chǎn)權(quán) 32 位嵌入式處理器 IP 核(即 Andes core)的供應(yīng)商與系

統(tǒng)芯片開發(fā)平臺(tái)的設(shè)計(jì)公司。晶心科技為基于 Andes core 進(jìn)行 SoC 設(shè)計(jì)和開發(fā)的客戶提供了一套完整的 ESL 解決方案-AndESLive。本文將介紹 AndESLive 這套 ESL 開發(fā)工具是如何幫助客戶快速確定符合市場(chǎng)需求的最佳體系結(jié)構(gòu),并實(shí)現(xiàn)軟硬件并行工作以縮

減開發(fā)周期的目的。

1. 為什么采用 ESL 設(shè)計(jì)

隨著 SoC 設(shè)計(jì)的發(fā)展,芯片規(guī)模變得越來越大,IP 的使用進(jìn)一步增加,復(fù)雜度和性

能的需求不斷提高。另一方面,嵌入式軟件開發(fā)在整個(gè)設(shè)計(jì)中所占的比重也越來越大,

整個(gè)系統(tǒng)的性能越來越取決于軟硬件協(xié)同工作所表現(xiàn)出的綜合性能。因此,芯片在設(shè)計(jì)

階段就需要進(jìn)行深入的系統(tǒng)級(jí)仿真,以及在芯片的仿真模型上運(yùn)行大量軟件以覆蓋所需

的功能。傳統(tǒng)的設(shè)計(jì)流程無法滿足這些仿真的執(zhí)行性能,就需要采用一種新的工具來避

免由于早期設(shè)計(jì)的不確定性所帶來的影響。

ESL 設(shè)計(jì)和驗(yàn)證是一種在較高的抽象層次上對(duì)芯片進(jìn)行描述和分析的設(shè)計(jì)方法學(xué),

它能夠讓設(shè)計(jì)工程師快速地構(gòu)建原型平臺(tái),并以緊耦合的方式開發(fā)、優(yōu)化和驗(yàn)證復(fù)雜系

統(tǒng)架構(gòu),從而實(shí)現(xiàn)最優(yōu)化的系統(tǒng)性能。另外,采用 ESL 的方法還可以使軟件設(shè)計(jì)人員

提早進(jìn)入調(diào)式和驗(yàn)證,大幅縮短產(chǎn)品上市時(shí)間。因此,采用 ESL 的設(shè)計(jì)方法已經(jīng)成為

IC 設(shè)計(jì)的必然趨勢(shì)。

2. 晶心科技的 ESL 解決方案:AndESLive

AndESLive 是以 ESL 設(shè)計(jì)和驗(yàn)證理念為理論基礎(chǔ),專門針對(duì)基于 Andes core IP 進(jìn)

行 SoC 開發(fā)而設(shè)計(jì)的 ESL 開發(fā)工具。它集成在 AndeSight(晶心科技基于 Andes core 的集成開發(fā)環(huán)境)中,并通過 AndeSight 提供的 GUI 界面和工程師進(jìn)行交互。

AndESLive 為設(shè)計(jì)人員提供了一個(gè)虛擬評(píng)估平臺(tái)(VEP,Virtual Evaluation Platform),它是一個(gè)描述真實(shí)系統(tǒng)行為的系統(tǒng)級(jí)仿真模型。VEP 的核心由兩個(gè)部分組成,前端叫做Virtual SoC Builder,它可以幫助設(shè)計(jì)人員快速構(gòu)建系統(tǒng)原型平臺(tái);后端是一個(gè)系統(tǒng)級(jí)的模擬器。工程師可以在原型平臺(tái)上,對(duì)系統(tǒng)(包括硬件和軟件)性能進(jìn)行評(píng)估和驗(yàn)證,從而實(shí)現(xiàn)系統(tǒng)設(shè)計(jì)的最優(yōu)化。

3. Virtual SoC Builder

AndESLive 中的 Virtual SoC Builder 為設(shè)計(jì)人員提供快速搭建目標(biāo)系統(tǒng)原型的功能。

在 AndESLive 中,已經(jīng)預(yù)定義了 Andes 各個(gè)系列 CPU 的 IP,以及各種周邊設(shè)備控制器

的 IP,包括高速設(shè)備(Memory、DMA、LCD、Ethernet 等)、低速設(shè)備(Uart、GPIO、SSP 等)和 BUS(AHB、APB)。另外,工程師還可以添加用戶自定義的 IP 模塊來實(shí)現(xiàn)一些特殊的功能需求。

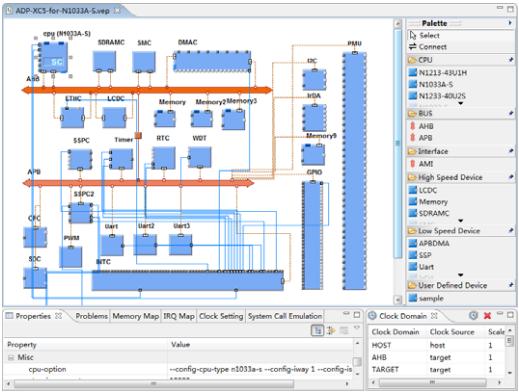

圖 1 為 Virtual SoC Builder 在 AndESLive 中的基本 UI 界面。界面上方的區(qū)域是設(shè)計(jì)

人員構(gòu)建虛擬 SoC 系統(tǒng)模型的編輯區(qū),工程師根據(jù)需要通過選擇右側(cè) IP 庫(kù)中的 IP 模型,并將它們之間的端口(主從端口和讀寫端口)進(jìn)行連接,就可以很快的架設(shè)起初步的

SoC 原型。工程師可以通過 Virtual SoC Builder 界面下方的 Properties 視窗對(duì)單個(gè) IP 模塊的屬性進(jìn)行配置,例如修改 CPU 的 I/D Cache、MMU、I/D Local memory 等參數(shù)。還可以通過其他一些視窗對(duì)整個(gè) SoC 系統(tǒng)進(jìn)行設(shè)定,例如配置內(nèi)存映射、配置中斷和設(shè)置時(shí)鐘等。

圖 1 Virtual SoC Builder 操作界面

4. AndESLive 中的模擬器

4.1 基于 SID 的模擬器

AndESLive 采用 SID 作為 VEP 的后端模擬器來實(shí)現(xiàn)系統(tǒng)級(jí)仿真的功能。SID 是一個(gè)

用于構(gòu)建計(jì)算機(jī)系統(tǒng)仿真的框架,是一個(gè)松耦合模擬組件的集合。VEP 中的各種 IP 模

塊都是 SID 的組件,SID 通過標(biāo)準(zhǔn)的 API(定義管腳、總線、屬性和關(guān)系)掛載組件,

并通過 SID 配置文件實(shí)現(xiàn)組件間的連接和交互,從而達(dá)到模擬物理硬件行為的目的。

AndESLive 中的模擬器具有很高的仿真效能,其執(zhí)行是基于機(jī)器周期或是機(jī)器指令

的。工程師不僅可以在 VEP 上實(shí)現(xiàn)應(yīng)用程序的快速執(zhí)行,還可以進(jìn)行可視化的程序調(diào)

試和分析(profiling)。另外,模擬器提供了多種模擬 I/O 設(shè)備,例如 LCD、Uart、GPIO、

RTC 等,這使得工程師在 VEP 上運(yùn)行應(yīng)用程序時(shí)可以進(jìn)行模擬的輸入或者得到與真實(shí)

硬件平臺(tái)一樣的輸出結(jié)果。

4.2 VEP 中的 IP 模型

事物處理級(jí)模型(TLM)用于建模可執(zhí)行平臺(tái),通常只描述系統(tǒng)各個(gè)功能單元之間的

抽象操作,一般來說即指各個(gè)功能單元之間交換的整個(gè)數(shù)據(jù)結(jié)構(gòu)(或?qū)ο螅┥献x取/寫

入或發(fā)送/接收操作。

AndESLive 的 VEP 功能就是基于事務(wù)級(jí)建模方法,采用事物處理級(jí)模型。VEP 中

虛擬 IP 模型的實(shí)現(xiàn)由兩部分組成,內(nèi)部是標(biāo)準(zhǔn)的 SID 組件,外部是符合 VEP 建模標(biāo)準(zhǔn)

的組件描述符,如圖 2 所示。組件描述符定義了 IP 功能模塊在 AndESLive 中需要展現(xiàn)

的特性,例如總線、管腳以及事件、時(shí)序等各種屬性,通過這層包裝 SID 組件便可以加

入到 VEP 中。對(duì)于 AndESLive 中已經(jīng)預(yù)定義好的 IP 模塊,工程師只要通過修改這些 IP

模塊的描述符,改變模塊的參數(shù)和屬性,便可以使之具備所需要的新的特性。

圖 2 VEP 模型結(jié)構(gòu)圖

如果需要添加新的 VEP 模塊,工程師需要進(jìn)行 VEP 模型的建模。建模有兩種方式,如果 SID 組件是由 C/C++語言來描述,那組件外部需要一層 XML 語言實(shí)現(xiàn)的描述符來進(jìn)行包裝;如果工程師希望用 SystemC 實(shí)現(xiàn)模塊,則需要實(shí)現(xiàn)一個(gè) SID-SystemC 橋文件,用 來 完 成 SID 與 SystemC 接 口 之 間 的 通 信 功 能 。 對(duì) 于 編 寫 組 件 描 述 符 文 件 或 者SID-SystemC 橋文件,晶心科技會(huì)提供完整的培訓(xùn)和技術(shù)資源,幫助客戶快速實(shí)現(xiàn)建模工作。

5.使用 AndESLive 進(jìn)行設(shè)計(jì)和開發(fā)

5.1 探索最優(yōu)化的系統(tǒng)架構(gòu)

隨著 SoC 芯片規(guī)模擴(kuò)大、工藝的提升, IP 的使用將進(jìn)一步增加,芯片可能包含多

個(gè)可編程部件(CPU 或 DSP)。為 了 SoC 設(shè)計(jì)的成功,在設(shè)計(jì)的初期探索和驗(yàn)證符合市場(chǎng)需求的最優(yōu)化系統(tǒng)架構(gòu)變得越來越重要。

AndESLive 為設(shè)計(jì)者提供了創(chuàng)建基于 TLM 的虛擬原型平臺(tái)功能。工程師可以通過

Virtual SoC Builder 快速組裝基于 Andes core 的虛擬原型;通過模擬器仿真驗(yàn)證系統(tǒng)結(jié)

構(gòu)方案功能的完整性;通過分析功能(profiling)不斷調(diào)正原型平臺(tái)中各個(gè)模塊的特性,在

性能、功耗和芯片制造成本之間尋求最佳平衡點(diǎn)。

圖三為使用 AndESLive 實(shí)現(xiàn)系統(tǒng)性能最優(yōu)化設(shè)計(jì)的示意圖。設(shè)計(jì)者首先在 Virtual

SoC Builder 中建立目標(biāo) SoC 原型(圖右側(cè)上方白色框所示),然后在 VEP 的模擬器上

運(yùn)行測(cè)試程序驗(yàn)證系統(tǒng)性能。如果測(cè)試結(jié)果未滿足規(guī)格要求,工程師可以借助模擬器產(chǎn)

生的分析報(bào)告(圖右側(cè)下方白色框所示)快速定位系統(tǒng)瓶頸,并對(duì) CPU 速度、Cache

大小、總線利用率、Memory 大小等多方面進(jìn)行調(diào)整后再測(cè)試,直到結(jié)果符合設(shè)計(jì)規(guī)格

的要求。此時(shí),設(shè)計(jì)者便獲得了最佳的系統(tǒng)架構(gòu)方案。

AndESLive 的 VEP 功能就是基于事務(wù)級(jí)建模方法,采用事物處理級(jí)模型。VEP 中

虛擬 IP 模型的實(shí)現(xiàn)由兩部分組成,內(nèi)部是標(biāo)準(zhǔn)的 SID 組件,外部是符合 VEP 建模標(biāo)準(zhǔn)

的組件描述符,如圖 2 所示。組件描述符定義了 IP 功能模塊在 AndESLive 中需要展現(xiàn)

的特性,例如總線、管腳以及事件、時(shí)序等各種屬性,通過這層包裝 SID 組件便可以加

入到 VEP 中。對(duì)于 AndESLive 中已經(jīng)預(yù)定義好的 IP 模塊,工程師只要通過修改這些 IP

模塊的描述符,改變模塊的參數(shù)和屬性,便可以使之具備所需要的新的特性。

圖 2 VEP 模型結(jié)構(gòu)圖如果需要添加新的 VEP 模塊,工程師需要進(jìn)行 VEP 模型的建模。建模有兩種方式,

圖 3 用 AndESLive 探索最優(yōu)化的系統(tǒng)架構(gòu)

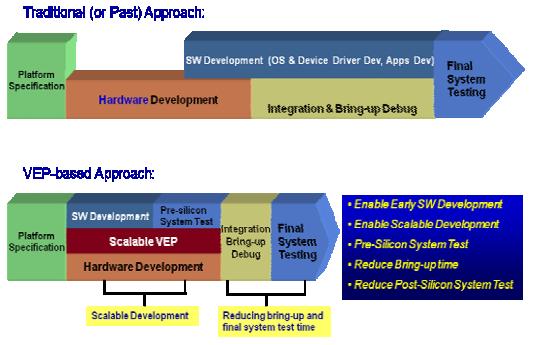

5.2 大幅度縮短開發(fā)周期

在 SoC 設(shè)計(jì)中,系統(tǒng)性能不僅取決于芯片硬件,還取決于運(yùn)行在芯片上的嵌入式軟

件。采用傳統(tǒng)設(shè)計(jì)流程,設(shè)計(jì)者無法準(zhǔn)確估算軟件性能,因此就無法確定整個(gè)系統(tǒng)的最

終規(guī)格,只能憑借工程師的經(jīng)驗(yàn)設(shè)計(jì)。此外,軟件的設(shè)計(jì)、開發(fā)也只能在芯片的硬件原

型已經(jīng)提供后才能執(zhí)行,這使得軟/硬件整合時(shí)間被推遲,于是整個(gè)系統(tǒng)開發(fā)周期就變

長(zhǎng)了。

圖 4 傳統(tǒng)設(shè)計(jì)流程與基于 VEP 的設(shè)計(jì)流程

采用基于 AndESLive VEP 的開發(fā)流程與傳統(tǒng)開發(fā)流程相比(圖 4 所示),軟/硬件開發(fā)可以同時(shí)進(jìn)行,因此系統(tǒng)的設(shè)計(jì)、開發(fā)和驗(yàn)證過程更加快速,這不僅使得產(chǎn)品可以更早的

進(jìn)入市場(chǎng),而且各種開發(fā)資源也得到了更大的使用效率,從而進(jìn)一步降低了成本。

6. 結(jié)語

晶心科技(Andes)是一家致力于32位嵌入式處理器IP的授權(quán)公司,面對(duì)不同應(yīng)用層級(jí)的32位處理器市場(chǎng),推出了Andes core:N9(50-200MHz)、N10(50-240MHz)、N12(50-660MHz)三個(gè)系列的低功耗高性價(jià)比的32位處理器軟、硬核IP。AndESLive是晶心科技為基于Andes core進(jìn)行SoC開發(fā)而設(shè)計(jì)的ESL開發(fā)工具。AndESLive幫助客戶找到最優(yōu)化的系統(tǒng)架構(gòu)方案,使產(chǎn)品更有效的滿足市場(chǎng)需求;基于VEP的設(shè)計(jì)流程,大幅縮

減了芯片開發(fā)周期,使產(chǎn)品在市場(chǎng)中具備更強(qiáng)的競(jìng)爭(zhēng)力。

AndESLive 提供了事物處理級(jí)的虛擬原型平臺(tái),即 VEP。有了和實(shí)際硬件一致的模

型,軟件工程師就可以和硬件設(shè)計(jì)人員并行工作,進(jìn)行代碼編寫并在虛擬原型上進(jìn)行測(cè)

試。VEP 中的 TLM 模型比同等的 RTL 模型運(yùn)行速度快 100 至 1000 倍,這個(gè)速度足以

運(yùn)行相當(dāng)大的應(yīng)用程序,例如像 Linux 這樣的操作系統(tǒng)。另外,軟件開發(fā)人員的提早介

入,使軟/硬件的集成和驗(yàn)證變得更加容易。這樣,在芯片硬件開發(fā)完成后,大部分或

者全部軟件都已經(jīng)準(zhǔn)備好并經(jīng)過驗(yàn)證,從而縮短了最后的硬件和軟件集成的時(shí)間。

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。