摘要:針對Xilinx FPGA在航天應用中的可行性,,文章分析了Xilinx FPGA的結(jié)構(gòu)以及空間輻射效應對FPGA的影響,,結(jié)合實際工程實踐給出了提高其可靠性的一有用辦法和注意事項,如冗余設計,、同步設計,、自檢等。表明配置信息的周期刷新和三模冗余設計是減輕單粒子效應的有效方法,。

關(guān)鍵詞:可編程邏輯門陣列,;總劑量效應;單粒子翻轉(zhuǎn),;單粒子閂鎖,;單粒子功能中斷;單粒子燒毀:單粒子瞬

0 引言

空間輻射環(huán)境中的帶電粒子會導致航天器電子系統(tǒng)的半導體器件發(fā)生單粒子效應,,嚴重影響航天器的可靠性和壽命,,其中高能質(zhì)子和重離子是導致單粒子效應的主要因素。必須對航天器用電子元器件的單粒子效應進行評估,,采取一定的抗輻射加固措施,,提高其可靠性。因此,,空間輻射的單粒子效應研究具有重要意義,。

基于SRAM的FPGA在航天領(lǐng)域受到極大關(guān)注。Xilinx公司的FPGA相繼在MARS2003 Lander(JPL)XQR4062XL:Controlling Pyrotechnics,、MARS2003 Rover(JPL)XQVR1000:Motor Control,、GRACE(NASA、XQR4036XL:Sensor等任務中成功應用之后,,國外航天界對Xilinx FPGA的應用興趣大增,。我國相關(guān)領(lǐng)域?qū)ilinxFPGA的航天應用正處在研究階段,,對其中亟待解決的可靠性設計問題研究相對較少,本文根據(jù)作者在某衛(wèi)星載荷設備信號處理器中的實踐對Xilinx FPGA(以下簡稱FPGA)的可靠性設計技術(shù)進行了研究,。

1 Xilinx FPGA介紹

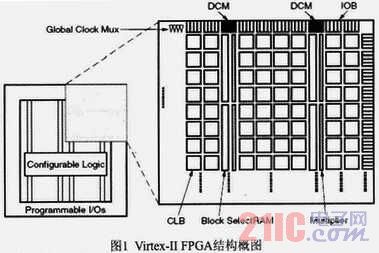

Xilinx SRAM型FPGA主要由以下幾部份組成,,圖1所示為Virtex II FPGA的結(jié)構(gòu)圖。

(1)配置存儲器(Configure Memory):FPGA可以看作配置存儲器和受其控制的可配置邏輯資源兩層的疊加,。配置存儲器是FPGA內(nèi)部的一個大容量存儲器,,控制著可配置邏輯資源,如布線資源,、可編程邏輯資源,、數(shù)字時鐘等邏輯功能。配置存儲器的失效將造成FPGA功能的持久失效(直至重新配置成功),。

(2)布線資源(Routing Resource):布線資源是FPGA內(nèi)部邏輯功能單元互聯(lián)的通道,,它將用戶設計的各個邏輯功能模塊連在一起。

(3)可編程I/O(Programmable I/O):FPGA的輸入輸出接口,,通常情況下I/O腳可以設置成輸入,、輸出、高阻態(tài),、雙向I/O,。

(4)可編程邏輯單元(CLB:Configurable LogicBlock):可編程邏輯功能單元是FPGA的細胞,通過它可以完成各式各樣的邏輯功能,。

(5)塊存儲器(Block Select-RAM)和乘法器(Multiplier)等:FPGA內(nèi)部集成的硬件存儲器和乘法器,,用以實現(xiàn)快速的數(shù)字運算。

(6)數(shù)字時鐘管理模塊(DCM:Digital ClockManager):FPGA內(nèi)部的時鐘管理單元,。通過它可以對輸入時鐘進行倍頻,、分頻處理,同時還可以減小時鐘的抖動,,提高時鐘的驅(qū)動能力,。

目前FPGA的工藝水平從Virtex系列的220mm發(fā)展到Virtex II的150mm,一直到現(xiàn)在Virtex 4系列高密度FPGA的90nm,,雖然抗總劑量效應能力在不斷增強,,但是隨著器件的核電壓的降低、門數(shù)的劇增,,單粒子效應會越來越明顯,。因此FPGA上述組成部分,如配置存儲器,、CLB和塊存儲器的抗輻射可靠性設計越來越重要,。

2 輻射效應及其影響

空間電子設備由于其所處的軌道不同,受到的輻射影響也不相同,但是,,總的來講對Xilinx FPGA影響比較大的輻射效應主要有:總劑量效應(TID:Total IonizingDose),、單粒子翻轉(zhuǎn)(SEU:Single Event Upset)、單粒子閂鎖(SEL:Single Event Latch-up),、單粒子功能中斷(SEFI:Single Event Functional Interrupt),、單粒子燒毀(SEB:Single Event Burnout)、單粒子瞬態(tài)脈沖(SET:Single Event Tran-sient),、位移損傷(Displacement Damage)等,。上述輻射效應產(chǎn)生的機理不盡相同,引起FPGA的失效形式也不同,。

FPGA的配置存儲器,、DCM、CLB,、塊存儲器對單粒子翻轉(zhuǎn)比較敏感,,可通過TMR(三倍冗余法)、Scrubbing等來解決,。

單粒子閉鎖會導致FPGA電流增大,,局部溫度升高,有時甚至可以高達200℃上,,如果FPGA長時間處于高溫狀態(tài)將導致器件的永久損壞,。只有降低電源電壓才能退出閂鎖狀態(tài),,因此在檢測到單粒子閂鎖之后最好的辦法是斷開器件的電源,。

FPGA中單粒子功能中斷的敏感部分為配置存儲器、上電復位電路(POR:power on reset),、

Select-MAP接口和JATAG接口,,分別可通過Monitor the DONE pin、Read and Write to FAR,、Read-back and compare to known CRC和toggling PROG等措施解決,,對所有SEFI,Xilinx提供IP監(jiān)視和改正,。

單粒子瞬態(tài)脈沖能引起FPGA內(nèi)部邏輯電路的短時錯誤,,可通過TMR、Scrubbing等來解決,。單粒子瞬態(tài)脈沖對于小于0.25 μm工藝的FPGA影響較大,。

上述輻射效應對FPGA造成的影響有的是永久性的,如總劑量效應,、單粒子燒毀,、位移損傷;有的是能夠恢復的,如單粒子翻轉(zhuǎn),、單粒子功能中斷,、單粒子瞬態(tài)脈沖。接下來根據(jù)對上述輻射影響的分析,,研究提高FPGA抗輻射效應的可靠性設計方法,。

3 FPGA抗輻射效應可靠性設計

FPGA抗輻射效應可靠性設計可以從以下幾方面進行考慮:FPGA整體設計加固考慮;散布內(nèi)部間接檢測輻射效應的自檢模塊,;引入外部高可靠性的電子器件在空間中不可避免地會受到輻射效應監(jiān)測模塊等措施,。

3.1 整體加固設計

在電子設備的外面一般采用一定厚度的材料對輻射進行屏蔽,屏蔽可以減少設備所受的輻射效應,。不同的材料對不同的粒子有著不同的屏蔽性能,,經(jīng)常采用的材料有鋁、鉭和脂類化合物等,。整體屏蔽的辦法在航天電子設備中使用較多,,也比較成熟。

結(jié)合我們實際,,考慮整星及電控機箱的整體屏蔽效果,,在軌高500km及四年工作壽命條件下,選器件耐輻射能力10~20krad(Si)以上,。

3.2 冗余設計

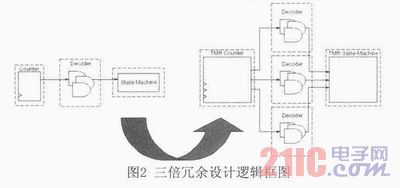

冗余設計方法是被公認為比較可靠的應對輻射效應的方法,。常用的冗余設計有三倍冗余法(TMR:Triple Module Redundancy)和部分三倍冗余法(PTMR:PartialTriple Module Redundancy)。圖2所示為Xilinx推薦的三倍冗余設計邏輯,,這種邏輯充分的考慮了SEU,、SET產(chǎn)生的

影響。雖然TMR帶來了可靠性的提高,,但是也會使模塊的速度降低(有的甚至低到原來的80%),、占用資源和功率增加(約為3.2倍)。

TMR:Throughput Logic

簡單復制(Three copies of the original design-Logic and I/O)

TMR Tradeoffs(TMR折中方案)

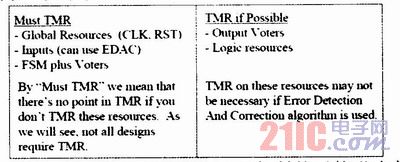

設計時可以根據(jù)實際情況對關(guān)鍵部分使用部分三倍冗余法,。全部邏輯和敏感端口三模冗余有時需要權(quán)衡做出折衷,,如下表。

FPGA的可編程I/O也容易受到輻射粒子的影響產(chǎn)生SEU和SEL(目前只發(fā)現(xiàn)三態(tài)腳在發(fā)生錯誤時可以變成輸出腳,,還沒有發(fā)現(xiàn)I/O發(fā)生方向轉(zhuǎn)換(即輸入變成輸出或者輸出變成輸入),。輸入輸出腳的三倍冗余設計是一種非常有效的方法,尤其是對因為配置存儲器發(fā)生單粒子效應的情況下,,但是這種方法需要占用三倍的I/O資源,,所以設計的時候需要慎重考慮。

我們在FPGA內(nèi)分多個區(qū)域,,分別采用TMR設計,,減小出錯概率。

3.3 防止關(guān)鍵電路SET引起的抖動

SET在時鐘電路或者其他數(shù)據(jù)、控制線上容易產(chǎn)生短脈沖抖動,,這種抖動有可能會造成電路的誤觸發(fā)或者數(shù)據(jù)鎖存的錯誤,。為了減少這種短脈沖抖動的影響,在設計時可采用如下方法:

(1)內(nèi)部復位電路盡可能使用同步復位,;

(2)控制線盡可能配合使能信號線使用,;

(3)組合邏輯數(shù)據(jù)在鎖存時盡可能配合使能信號。

也就是說,,盡量在觸發(fā)邏輯中配合另一個使能條件,,這樣就可以屏蔽由SET產(chǎn)生的大部分抖動。

3.4 系統(tǒng)監(jiān)控與重配置(Configuration Scrubbing)

在某些設計壽命不是很長的衛(wèi)星中,,COTS器件的應用已經(jīng)成為可能,,在類似的信號處理或者星務管理平臺中,采用一種金字塔形體系結(jié)構(gòu)可以大大提高平臺的可靠性,,有效地抵抗各種輻射效應引起的可恢復故障,。

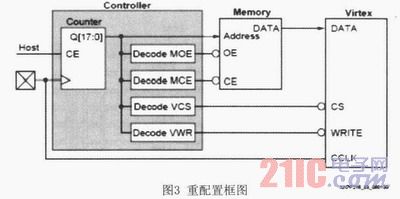

Actel高可靠性的反熔絲FPGA負責從非易失大容量存儲器中讀取Xilinx FPGA的配置數(shù)據(jù)對其進行配置,然后在運行期間,,對最容易受輻射效應影響的配置存儲器按列進行讀操作,,然后與標準數(shù)據(jù)進行比對,對出現(xiàn)錯誤的列進行局部重配置,。

另外,,也可以通過對回讀數(shù)據(jù)進行CRC校驗來檢驗配置存儲器是否出現(xiàn)錯誤。

對配置存儲器的回讀校驗和重配置(或局部重配置)是一種有效的抵抗輻射效應的方法,。

Scrubbing通過部分重置刷新配置存儲器,,通過連續(xù)重置修復SEU,Scrub速度至少十倍于最壞的SEU速度,??梢酝ㄟ^兩條途徑來實現(xiàn)Scru-bbing,第一條途徑是回讀,、比較、修復(closed-loop scrubbing)),,第二條途徑是連續(xù)重置(open-loop scrubbing) 并不是所有的資源都可以被scrubbed的,,比如SRL16s、LUT RAM,、BRAM,、BRAM data就不能被scrubbed,可以使用BRAM多模冗余或EDAC算法,。

也并不是所有的資源都需要被scrubbed,,大部分routing bits不需要scrubbed。

4 結(jié)論

文章結(jié)合實際工程實踐給出了解決常見的FPGA輻射失效問題的一些方法;對FPGA在電源輸入端使用限流電阻,,信號處理板采用雙機冷備份,,對于單粒子翻轉(zhuǎn)和鎖定均具有相應對策,如發(fā)生單粒子翻轉(zhuǎn)或鎖定只對單機的部分功能有影響,,都可以通過切機或重新加電消除影響,。本文給出的有關(guān)大規(guī)模可配置電子器件的設計方法可以為航天電子設備的設計提供參考,。