0 引言

Compact PCI(簡稱CPCI)總線是“PCI總線工業(yè)計(jì)算機(jī)制造商組織”推出的一種工業(yè)計(jì)算機(jī)總線標(biāo)準(zhǔn),近年來應(yīng)用發(fā)展最為迅速。它由PC機(jī)上的通用總線PCI發(fā)展而來,既有PCI總線的高帶寬、高性能、即插即用、價(jià)格低廉等諸多優(yōu)點(diǎn),又有無源背板總線VME總線的可靠性。CPCI總線在33MHz時(shí)鐘、32位數(shù)據(jù)寬度的條件下可達(dá)到峰值132MB/s的帶寬,在66MHz時(shí)鐘、64位數(shù)據(jù)寬度的條件下可達(dá)到峰值528MB/s的帶寬。

PowerPC是1993年IBM、Apple和Motorola公司(其半導(dǎo)體部門現(xiàn)在分拆為Freescale公司)聯(lián)盟共同設(shè)計(jì)的。PowerPC技術(shù)以RISC(精簡指令集計(jì)算機(jī))為基礎(chǔ),該技術(shù)由IBM的POWER(性能優(yōu)化的增強(qiáng)RISC)體系結(jié)構(gòu)而來。PowerPC中的PC代表Performance Computing,PowerPC即超強(qiáng)的高性能計(jì)算處理器。因PowerPC芯片具有高性能和低功耗的特點(diǎn),主要應(yīng)用于嵌入式系統(tǒng)。

1 系統(tǒng)結(jié)構(gòu)

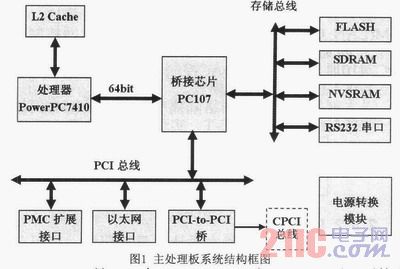

主處理板的系統(tǒng)結(jié)構(gòu)框圖見圖1。主要由四部分組成:電源轉(zhuǎn)換功能模塊、PowerPC功能模塊、外圍接口(RS232串口、以太網(wǎng)口及PMC擴(kuò)展接口)功能模塊、CPCI總線(PCI-to-PCI橋)功能模塊。

2 硬件設(shè)計(jì)

2.1 電源轉(zhuǎn)換功能模塊

電源設(shè)計(jì)在整個(gè)硬件設(shè)計(jì)中非常重要,好的電源設(shè)計(jì)才能保證主處理板正常穩(wěn)定的工作。硬件上設(shè)計(jì)有4種電源:主供電電源5V(由外部提供),PowerPC7410內(nèi)核電壓1.8V,橋接芯片PC107內(nèi)核電壓2.5V,各芯片I/O電壓3.3V。

采用LINEAR公司的DC/DC開關(guān)電源模塊實(shí)現(xiàn)主供電電源5V到1.8V、2.5V和3.3V的電壓轉(zhuǎn)換,每路最大輸出電流10A。該DC/DC電源模塊代表了一種面向負(fù)載點(diǎn)電源的新型架構(gòu),它顯著地簡化了電源設(shè)計(jì)工作。它具有很多優(yōu)秀的特點(diǎn):高功率、高效率、尺寸小、重量輕、散熱性能好等,除此之外,它還具有的一項(xiàng)獨(dú)特性能是其無時(shí)鐘延遲電流模式,從而令其能夠?qū)ω?fù)載電流的快速變化迅速做出響應(yīng)。

2.2 PowerPC功能模塊

2.2.1 處理器

處理器采用飛思卡爾公司的PowerPC處理器MPC7410。主處理器通過橋接器MPC107訪問板內(nèi)資源。

MPC7410是G4系列的高性能處理器,G4在G3的基礎(chǔ)上在性能上有很大提高,主要表現(xiàn)在支持對稱多處理器(SMP)結(jié)構(gòu)和引入了一流的Alti-Vec技術(shù)來處理矢量運(yùn)算。AltiVec技術(shù)是一個(gè)128位的SIMD矢量處理引擎,為第四代PowerPC提供了卓越的處理性能,使其數(shù)據(jù)處理能力有了數(shù)量級的提升。

MPC7410內(nèi)部主頻最高為500MHz,每個(gè)時(shí)鐘周期最多可以執(zhí)行8條指令,其中包括4條矢量運(yùn)算(AltiVec)指令和2條整型指令。通過加入AltiVec技術(shù),處理能力達(dá)到了4G FLOPS。而1.8V的低電壓操作大大降低了芯片的功耗,容易散熱,從而大大提高了系統(tǒng)的穩(wěn)定性。

MPC7410提供了兩種總線模式:60X總線模式和MPX總線模式,不同的總線定義的信號也有所不同。總線的選擇,可通過MPC7410的EMODE信號來選擇,當(dāng)EMODE信號在HRESET信號變?yōu)楦唠娖綍r(shí)也為高電平,則選擇了60X總線。反之,當(dāng)EMODE信號在HRESET信號變?yōu)楦唠娖綍r(shí)為低電平,則選擇了MPX總線。由于60X總線具有優(yōu)秀的連接性能和高數(shù)據(jù)傳輸速率,在本設(shè)計(jì)中采用60X總線作為MPC7410和芯片組的連接。

此外,還可通過對MPC7410的PLL信號設(shè)置產(chǎn)生不同的內(nèi)核頻率,本設(shè)計(jì)中處理器的外部頻率為100MHz,采用5倍的頻率系數(shù),即處理器主頻為500MHz。

2.2.2 L2 Cache

MPC7410處理器支持L2 Cache,內(nèi)部集成了L2Cache接口控制器,提供L2 Cache接口的總線時(shí)序控制電路,通過處理器內(nèi)部L2 Cache控制器可以訪問Cache存儲器。主處理板上實(shí)現(xiàn)了總?cè)萘繛?MByte的L2 Cache,數(shù)據(jù)寬度為72位,其中8位為校驗(yàn)位,64位為數(shù)據(jù)位。

2.2.3 橋接器

橋接器PC107是為PowerPC專門設(shè)計(jì)的橋芯片/存儲器控制器,主要實(shí)現(xiàn)PowerPC到PCI的橋接功能,同時(shí)管理memory,可以運(yùn)行在高達(dá)133MHz的處理器總線頻率。PC107提供其他嵌入式應(yīng)用必需的功能:處理器總線接口、PCI總線接口、存儲器控制器、智能輸入/輸出信息控制器、I2C控制器、嵌入式可編程中斷控制器(EPIC)、雙通道集成DMA控制器、時(shí)鐘控制部分等。根據(jù)在電路中所起的作用不同,PC107的工作方式可分為host mode和agent mode兩種。在host mode模式中,由PC107管理存儲器和PCI總線部分,PowerPC為整個(gè)系統(tǒng)的主CPU。在agent mode模式中,PC107用于和PCI主橋通信,PowerPC作為一個(gè)PCI設(shè)備,受PCI主橋的管理。本設(shè)計(jì)中PC107的工作方式為host mode。

2.2.4 存儲器

主處理板上設(shè)計(jì)有SDRAM存儲器、系統(tǒng)FLASH存儲器、64位用戶FLASH存儲器和NVSRAM存儲器。其容量配置見表1。

2.2.4.1 SDRAM

在本設(shè)計(jì)中,SDRAM用于存放操作系統(tǒng)臨時(shí)數(shù)據(jù)以及應(yīng)用程序的數(shù)據(jù)和代碼,為程序的運(yùn)行和保存臨時(shí)文件提供空間。SDRAM的管理由me-mory控制器來實(shí)現(xiàn)。橋接器PC107提供了高速SDRAM控制器,數(shù)據(jù)寬度配置為64位。PC107的SDRAM接口特點(diǎn):SDRAM器件必須與SDRAM的JEDEC規(guī)范兼容,32位和64位數(shù)據(jù)可選寬度,支持頁面式訪問,支持8個(gè)物理bank,最大支持1GB的存儲大小。本設(shè)計(jì)中SDRAM的總?cè)萘繛?12MB,總線時(shí)鐘設(shè)計(jì)為100MHz。

由于SDRAM時(shí)鐘總線的頻率較高,為了提高模塊的抗干擾能力和電磁兼容性,在PCB布局布線,包括走線長度、布線路徑、阻抗匹配、線長線寬及間距等方面提出嚴(yán)格要求,并且在PCB制作前期通過仿真對信號完整性進(jìn)行分析,確保電路的可行性。

2.2.4.2 FLASH

本設(shè)計(jì)中FLASH分為系統(tǒng)FLASH和應(yīng)用FLASH。系統(tǒng)FLASH地址分配在存儲空間的高端,用于系統(tǒng)的啟動,系統(tǒng)FLASH上駐留BootRom引導(dǎo)程序、上電BIT測試程序、FLASH在板編程程序及操作系統(tǒng)。容量為4MB,8位數(shù)據(jù)寬度。應(yīng)用FLASH用于儲存應(yīng)用程序,總?cè)萘繛?56MB,64位數(shù)據(jù)寬度。

2. 2. 4.3 NVSRAM

NVRAM是非易失存儲器,用于存放系統(tǒng)重要信息,32kB存儲容量,8位數(shù)據(jù)寬度。

2.2.5 復(fù)位

主處理板硬件復(fù)位包括兩種:a.上電復(fù)位:外部電源5V電壓低于4.65V時(shí),該主處理板處于復(fù)位狀態(tài),外部電源5V電壓高于4.65V后,產(chǎn)生大于200ms復(fù)位,復(fù)位整個(gè)硬件,同時(shí)驅(qū)動CPCI總線復(fù)位信號;b.手動復(fù)位輸入:由外部手動復(fù)位引起,復(fù)位整個(gè)硬件,同時(shí)驅(qū)動CPCI總線復(fù)位信號。

2.2.6 看門狗

主處理板具有看門狗功能,當(dāng)看門狗功能失效后,產(chǎn)生看門狗中斷,上電默認(rèn)為禁止。在FPGA內(nèi)部設(shè)置看門狗使能寄存器,可以通過軟件使能或禁止看門狗,看門狗定時(shí)器報(bào)警后產(chǎn)生中斷。看門狗定時(shí)周期由硬件設(shè)置。

2.2.7 FPGA

FPGA主要負(fù)責(zé)系統(tǒng)的復(fù)位、中斷管理和相關(guān)接口的時(shí)序和邏輯控制。本設(shè)計(jì)采用Xilinx的Virtex系列芯片,該系列FPGA片內(nèi)含有豐富的寄存器/鎖存器、同步、異步置位/復(fù)位信號、鎖相環(huán)等。這款FPGA有30萬門,260個(gè)IO管腳,滿足設(shè)計(jì)要求。使用FPGA的另一個(gè)顯著優(yōu)點(diǎn)是可以不斷地完善程序,進(jìn)行實(shí)時(shí)在線編程。

2.2.8 定時(shí)器

PC107內(nèi)部提供4路32位定時(shí)器,定時(shí)時(shí)鐘為PC107的輸入時(shí)鐘的1/8,精度±50ppm:時(shí)鐘中斷輸入到處理器。其中定時(shí)器1作為操作系統(tǒng)定時(shí)時(shí)鐘,其它3路定時(shí)器作為應(yīng)用程序操作時(shí)鐘,可通過軟件對其進(jìn)行設(shè)置,最小定時(shí)周期為1ms。

2.3 外圍接口功能模塊

2.3.1 以太網(wǎng)接口

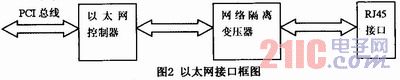

主處理板提供10MB/100MB自適應(yīng)的快速以太網(wǎng)接口,該以太網(wǎng)接口的設(shè)計(jì)基于橋接器PC107控制的PCI總線,基本框圖如圖2所示。主要由以太網(wǎng)控制器、網(wǎng)絡(luò)隔離變壓器和RJ45三部分組成。其中以太網(wǎng)控制器采用Intel公司的高集成度、高性能、低功耗10/100Mbps快速以太網(wǎng)控制芯片,專用于局域網(wǎng)到桌面的解決方案,如作為服務(wù)器、個(gè)人計(jì)算機(jī)和移動平臺的入網(wǎng)接口,符合LOM(LAN On Motherboard)設(shè)計(jì)規(guī)范。以太網(wǎng)控制器通過片上的命令和狀態(tài)寄存器經(jīng)由PCI總線和處理器MPC7410通信,包含了MAC控制器和物理層接口,可工作在半雙工模式和全雙工模式。

以太網(wǎng)控制器通過網(wǎng)絡(luò)隔離變壓器驅(qū)動RJ45網(wǎng)線接口,用來支持10/100BASE-T,實(shí)現(xiàn)與外界通信。

2.3.2 RS232串口

RS232串口的使用使本設(shè)計(jì)更具通用性,可以和具有相同類型串口的設(shè)備進(jìn)行通信。主處理板提供兩路RS232串行接口,用于與開發(fā)平臺的通訊,串口部分通過EXAR公司的UART通訊控制器來實(shí)現(xiàn),它帶有16字節(jié)的FIFO和半雙工控制,最大傳輸速率1.5Mbps。

2.3.3 PMC擴(kuò)展接口

主處理板支持2個(gè)64bit/66MHz的PMC擴(kuò)展接口,該接口滿足PCI2.2規(guī)范,可根據(jù)不同的系統(tǒng)需求進(jìn)行擴(kuò)展,如千兆網(wǎng)卡、數(shù)據(jù)采集卡、顯卡、電子盤等,使系統(tǒng)應(yīng)用更加靈活。

2.4 CPCI總線功能模塊

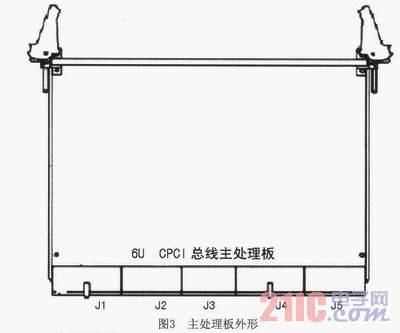

主處理板基于CPCI總線,CPCI總線的電氣特性與PCI總線相同。目前CPCI已經(jīng)取代VME以及STD工業(yè)標(biāo)準(zhǔn),成為工業(yè)界的新一代標(biāo)準(zhǔn)。主處理板遵從Eurocard工業(yè)標(biāo)準(zhǔn),定義了6U(233.35mm×160mm)板尺寸,CPCI板連接器共有5個(gè)插座,J1~J5。規(guī)范定義了J1和J2的信號線

管腳,J3~J5為自定義插座,如圖3所示。

本設(shè)計(jì)中用PLX公司的PCI-to-PCI橋芯片實(shí)現(xiàn)CPCI總線接口。該芯片提供標(biāo)準(zhǔn)的33MHz~66MHz的PCI總線接口,支持32位/64位PCI設(shè)計(jì),該芯連接PCI設(shè)備不需要額外的驅(qū)動電路和邏輯,可直接和主處理板內(nèi)部PCI信號直接連接。

3 底層軟件

主處理板移植性能穩(wěn)健的VxWorks操作系統(tǒng),它對很多設(shè)備提供支持,且設(shè)備驅(qū)動程序都采用模塊化設(shè)計(jì),各模塊之間功能明確、接口規(guī)范。

主處理板的底層軟件由兩個(gè)部分組成:BootRom引導(dǎo)代碼和VxWorks操作系統(tǒng)映像。系統(tǒng)上電先啟動BootRom引導(dǎo)程序,然后把引導(dǎo)代碼段和數(shù)據(jù)段從Flash拷至SDRAM中,引導(dǎo)代碼執(zhí)行后跳轉(zhuǎn)到VxWorks映像執(zhí)行。本系統(tǒng)采用網(wǎng)口加載VxWorks映像,這種啟動形式有獨(dú)特優(yōu)點(diǎn),能適應(yīng)硬件,方便調(diào)試和現(xiàn)場升級等。

BootRom引導(dǎo)代碼固化在主處理板的Flash上,作用是將主處理板的最小系統(tǒng)啟動起來,以完成加載和執(zhí)行VxWorks映像的目的。BootRom相對于VxWorks映像來說功能比較簡單,大小易于控制。BootRom成功運(yùn)行后,啟動了保護(hù)模式和文件系統(tǒng)支持,驅(qū)動了網(wǎng)絡(luò)、串口等輔助設(shè)備,消除了硬件環(huán)境對程序映像的限制,使得VxWorks應(yīng)用程序的制作和加載變得自由隨意。

5 結(jié)束語

CPCI總線是高速同步共享總線,基于此標(biāo)準(zhǔn)總線結(jié)構(gòu)的主處理板設(shè)計(jì)采用高性能的RISC微處理器MPC7410,并且移植VxWorks操作系統(tǒng),保證了基于CPCI總線的主處理板的穩(wěn)定性和可靠性。此外,主處理板還提供多種標(biāo)準(zhǔn)接口,能方便實(shí)現(xiàn)對系統(tǒng)中其他擴(kuò)展板如以太網(wǎng)卡、數(shù)據(jù)采集卡、顯卡、電子盤等的系統(tǒng)控制、管理及信息交換,提高系統(tǒng)性能。本主處理板現(xiàn)已應(yīng)用于某型號顯控處理機(jī),它還適用于任何CPCI總線系統(tǒng),可在聲吶、雷達(dá)、顯控等軍用或民用信號處理領(lǐng)域發(fā)揮作用。