摘要:在工業(yè)控制中如何提高一對多的串口通訊可靠性和系統(tǒng)的集成性成為研究熱點。本文利用嵌入式技術(shù),提出基于CPLD/FPGA的多串口擴展設(shè)計方案。實現(xiàn)并行口到多個全雙工異步通訊口之間的轉(zhuǎn)換,并根據(jù)嵌入式系統(tǒng)實時性的需要,在每個UART接收器中開辟了8個接收緩沖單元,實現(xiàn)高速嵌入式CPU與RS232通訊設(shè)備之間的速度匹配,同時,串行口波特率等參數(shù)可根據(jù)需要進行設(shè)置。通過實踐證明,本文設(shè)計的基于CPLD/FPGA的多串口完全符合工業(yè)控制中一對多串口通訊的要求。

關(guān)鍵詞:CPLD/FPGA;多串口擴展;全雙工;異步通信;嵌入式系統(tǒng)

在工業(yè)控制中,設(shè)備的通訊與控制主要采用簡潔高效的串口方式進行。工控機通過PCI擴展卡方式進行串口的擴展,或采用電路復(fù)雜的擴展芯片實現(xiàn)串口擴展。隨著嵌入式技術(shù)發(fā)展,嵌入式系統(tǒng)的應(yīng)用逐步代替了成本高昂的工業(yè)控制計算機。為了簡化硬件電路的設(shè)計,降低系統(tǒng)成本,本文提出了一種基于CPLD/FPGA多串口擴展的方案,實現(xiàn)多個外設(shè)串口的擴展和管理,同時解決一對多的串口通訊可靠性問題,滿足嵌入式系統(tǒng)串口擴展的需求。

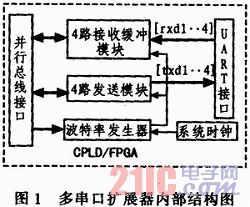

1 系統(tǒng)結(jié)構(gòu)

本設(shè)計以CPLD/FPGA芯片為核心,在芯片內(nèi)部通過設(shè)計、編程實現(xiàn)并行總線接口到多個串行口的擴展。設(shè)計的多串口擴展包括并行總線接口、4路接收緩沖器、4路發(fā)送器、波特率發(fā)生器和UART接口。為實現(xiàn)高速嵌入式CPU與RS232通訊設(shè)備之間的速度匹配,充分利用嵌入式系統(tǒng)的實時性,在每個接收緩沖器中開辟了8個接收緩沖單元。在實際應(yīng)用中,可根據(jù)嵌入式系統(tǒng)擴展的需要,靈活增減串口數(shù)量以及接收緩沖單元個數(shù)。在通訊過程,波特率發(fā)生器的時鐘信號由外部有源晶振提供,選擇合適的晶振頻率即可獲得高性能的數(shù)據(jù)傳輸。系統(tǒng)結(jié)構(gòu)如圖1所示。

2 功能模塊設(shè)計

2.1 接收緩沖模塊

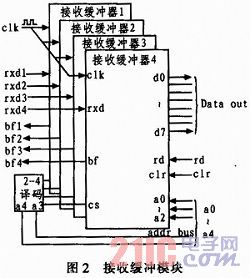

2.1.1 接收緩沖模塊構(gòu)架

在設(shè)計過程中,為便于串口擴展功能的實現(xiàn),將功能相似的部件進行了集成。本設(shè)計以4路UART接口擴展為例,接收緩沖部分包含了4個獨立的接收緩沖器,其結(jié)構(gòu)如圖2所示。接收緩沖器共用clk時鐘信號,并將其作為串行數(shù)據(jù)接收的波特率;每個接收緩沖器均有單獨的rxd、bf、cs引腳,其功能分別為:串行數(shù)據(jù)輸入、接收緩沖器儲存狀態(tài)、接收緩沖器片選。各接收緩沖器的片選端分別與2-4譯碼器的輸出腳相連。譯碼器的輸入端構(gòu)成了4路接收緩沖器選擇的地址線,分別對應(yīng)a3、a4腳;結(jié)構(gòu)圖中數(shù)據(jù)總線d0~d7、讀緩沖端rd、緩沖儲存狀態(tài)清‘0’端clr和緩沖單元地址線a0~a2為共用信號端口,分別與4個接收緩沖器相連。

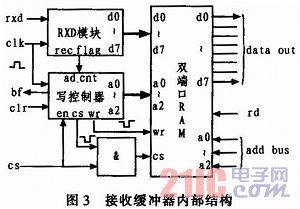

2.1.2 接收緩沖器內(nèi)部結(jié)構(gòu)

接收緩沖器內(nèi)部由RXD接收器、地址及寫控制器和雙端口RAM構(gòu)成,如圖3所示。

1)RXD接收器

RXD接收器的作用是接收串行設(shè)備發(fā)送的數(shù)據(jù)。clk腳引入波特率時鐘后,程序首先檢測串行數(shù)據(jù)輸入腳rxd的電平,當(dāng)檢測到rxd腳電平為‘0’即串行數(shù)據(jù)的開始信號后,接收器開始接收數(shù)據(jù)。連續(xù)接收8位數(shù)據(jù)后,接收到的數(shù)據(jù)將被送至d0~d7端,同時reg_flag端產(chǎn)生一個負(fù)脈沖信號,觸發(fā)寫控制器的ad_cnt端,寫控制器的地址線加‘1’并同時產(chǎn)生雙端口RAM的寫操作信號,完成接收數(shù)據(jù)的存儲。

接收時,clk時鐘為波特率的16倍,clk信號8分頻后即串行數(shù)據(jù)位的周期的中間位置檢測rxd腳電平狀態(tài),以保證串行數(shù)據(jù)準(zhǔn)確地接收,累計計數(shù)至16分頻時完成一位數(shù)據(jù)的接收。連續(xù)接收8位數(shù)據(jù)后,并判斷第9位狀態(tài)為‘1’時(停止位),完成一個字節(jié)的接收。RXD接收器的程序如下:

2)寫控制器

寫控制器的ad_cnt端接收到RXD接收器的reg_flag負(fù)脈沖信號后,對地址寄存器進行加‘1’操作,并將新的地址狀態(tài)送至雙端口RAM的地址總線a0~a2。同時,reg_flag負(fù)脈沖觸發(fā)寫控制器對clk時鐘計數(shù),向雙端口RAM產(chǎn)生cs片選信號和wr寫控制信號,將RXD接收器d0~d7的數(shù)據(jù)寫入雙端口RAM地址線所對應(yīng)的存儲單元中。

3)雙端口RAM

通過一系列時序信號的組合,RXD接收器接收的數(shù)據(jù)將暫存到雙端口RAM中。本設(shè)計中,雙端口RAM直接調(diào)用的Quartus8.0存儲器子庫中的LPM_RAM_DP元件。

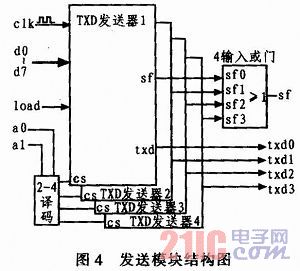

2.2 發(fā)送模塊

發(fā)送部分由4路并行的TXD發(fā)送器、2-4譯碼器和4輸入或門組成,如圖4所示。4路TXD發(fā)送器共用時鐘信號clk、數(shù)據(jù)端d0~d7、發(fā)送啟動端load;每個發(fā)送器均有單獨sf、cs、txd引腳,其功能分別為:發(fā)送狀態(tài)標(biāo)志、TXD發(fā)送器選擇、串行數(shù)據(jù)輸出。TXD發(fā)送器的cs端分別與2-4譯碼器的輸出腳相連,譯碼器的輸入端a0~a1即構(gòu)成發(fā)送部分的地址線;發(fā)送器的sf端經(jīng)過4輸入或門輸出,構(gòu)成發(fā)送部分的發(fā)送狀態(tài)標(biāo)志。

在通訊過程中,load腳接收到CPU的控制信號后,根據(jù)地址線a0~a1的組合選擇相應(yīng)的TXD發(fā)送器,將數(shù)據(jù)總線d0~d7上的數(shù)據(jù)通過txd腳逐位輸出,通過串行總線發(fā)送至接收設(shè)備。一個字節(jié)發(fā)送完成后,發(fā)送狀態(tài)端sf置‘0’,CPU可檢測sf端的電平狀態(tài),以判斷數(shù)據(jù)是否發(fā)送完成,也可以利用sf引腳的狀態(tài)觸發(fā)CPU中斷,完成多個數(shù)據(jù)的連續(xù)發(fā)送。發(fā)送器的程序與接收器相匹配,在此不再闡述。

2.3 波特率發(fā)生器

UART的接收和發(fā)送按照相同的波特率進行數(shù)據(jù)傳送。波特率發(fā)生器分別給接收部分和發(fā)送部分提供時鐘信號,并且接收的波特率時鐘是發(fā)送的16倍,利用16倍波特率時鐘對串行數(shù)據(jù)進行高速采樣,以確保接收數(shù)據(jù)的準(zhǔn)確性。為實現(xiàn)與不同傳輸速率的串行設(shè)備通信,波特率發(fā)生器對系統(tǒng)時鐘進行不同系數(shù)的分頻,根據(jù)CPU控制線的組合可分別產(chǎn)生4800bit/s、9600bit/s、19200bit/s、38400bit/s等多種波特率。

3 仿真與實現(xiàn)

本串口擴展器通過VHDL編程,在Ouartus8.0下進行了仿真。由于仿真信號較多,僅對關(guān)鍵部件的信號進行分析。圖5給出了RXD接收器仿真波形。在測試過程中,首先確定通信的波特率為19 200 bit/s,即RXD接收器CLK時鐘為波特率的16倍,發(fā)送設(shè)備通過串行總線向RXD接收器發(fā)送F1H,當(dāng)RXD接收器完成數(shù)據(jù)的接收后,立即將數(shù)據(jù)送至數(shù)據(jù)總線d0~d7,仿真結(jié)果如圖5所示。

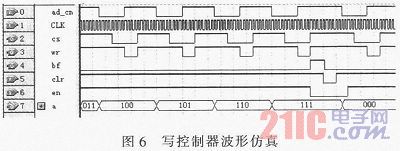

給寫控制器的ad_cnt端輸入地址計數(shù)脈沖,地址線a0~a2進行加‘1’操作,片選線cs和寫操作端wr根據(jù)CLK時鐘信號相應(yīng)輸出低電平,完成接收數(shù)據(jù)的寫存儲。連續(xù)存儲8個字節(jié)后,緩沖器狀態(tài)標(biāo)志bf置‘1’。將clr端輸入低電平,bf標(biāo)志清‘0’,同時地址線a0~a2回到“000”狀態(tài)。寫控制器的仿真結(jié)果如圖6所示。

給TXD發(fā)送器的數(shù)據(jù)總線d0~d7輸入AAH,通過串行總線發(fā)送至接收設(shè)備。load端置‘0’,啟動發(fā)送。發(fā)送完成后,sf標(biāo)志清‘0’。檢查接收設(shè)備的接收值,與發(fā)送數(shù)據(jù)完全匹配。TXD發(fā)送器的波形仿真結(jié)果如圖7所示。

4 結(jié)束語

本文詳細介紹了CPLD/FPGA多串口設(shè)計的內(nèi)部構(gòu)成,對各個模塊的工作原理和關(guān)鍵信號進行了分析,給出了EDA軟件仿真形波和測試結(jié)果。通過對FPGA/CPLD多串口的設(shè)計與實現(xiàn),為嵌入式系統(tǒng)中串口的擴展提供了一定的幫助。