隨著CMOS工藝的發(fā)展,特征尺寸不斷減小,CMOS器件的高頻性能得到了提高,同時(shí)也給RFIC設(shè)計(jì)帶來了一些挑戰(zhàn),如氧化層擊穿電壓降低,電流驅(qū)動(dòng)能力變?nèi)酰r底耦合嚴(yán)重等。雖然在一個(gè)發(fā)射機(jī)中,低噪聲放大器、振蕩器、混頻器已經(jīng)解決了采用CMOS技術(shù)的集成問題,但功率放大器的集成問題已成為制約單片集成發(fā)射機(jī)設(shè)計(jì)的主要因素。從耐壓性能考慮,晶體管氧化層耐壓能力的降低,降低了輸出級(jí)電壓的擺幅;電子驅(qū)動(dòng)能力的變?nèi)踅档土寺O電流數(shù)值;另外功率放大器的功耗也是限制其難以集成的原因。

1 射頻功率放大器設(shè)計(jì)

射頻功率放大器分線性和非線性放大器。非線性放大器的效率高,但線性度差,而且結(jié)構(gòu)復(fù)雜。本設(shè)計(jì)采用線性的A類放大器結(jié)構(gòu),電路簡(jiǎn)單,線性度好,有利于設(shè)計(jì)出穩(wěn)定工作的功率放大器。設(shè)計(jì)要求電路能夠在2.4GHz中心頻率,帶寬為100 MHz,在輸入功率為0dBm時(shí),輸出功率20 dBin,輸入反射系數(shù)S11<-10dB。

1.1 輸入匹配網(wǎng)絡(luò)設(shè)計(jì)

由于晶體管輸入阻抗是復(fù)數(shù),為了實(shí)現(xiàn)輸入阻抗與信號(hào)源阻抗匹配,必須進(jìn)行輸入匹配網(wǎng)絡(luò)設(shè)計(jì)。綜合考慮輸入級(jí)晶體管和偏置電路的影響,本設(shè)計(jì)輸入匹配網(wǎng)絡(luò)采用T形匹配網(wǎng)絡(luò),通過仿真,輸入端反射系數(shù)達(dá)到S11<-14dB。

1.2 輸出匹配網(wǎng)絡(luò)設(shè)計(jì)

由于CMOS晶體管受最大承受電壓和最大輸出電流的限制,為了充分利用電壓源提供功率的能力,輸出匹配網(wǎng)絡(luò)采用負(fù)載線匹配技術(shù),如圖1所示。分析射頻功率放大器的性能要求,確定晶體管最大輸出電流,根據(jù)晶體管的性能確定最大輸出電壓。本次設(shè)計(jì)首先通過計(jì)算確定負(fù)載線電阻的大概取值,然后經(jīng)參數(shù)掃描確定最優(yōu)負(fù)載線電阻,以此負(fù)載線電阻確定輸出匹配網(wǎng)絡(luò)各個(gè)參數(shù)。經(jīng)過優(yōu)化負(fù)載線電阻為6Ω。輸出匹配網(wǎng)絡(luò)采用L匹配。

1.3 級(jí)間匹配網(wǎng)絡(luò)設(shè)計(jì)

本設(shè)計(jì)采用A類單端兩級(jí)放大結(jié)構(gòu)實(shí)現(xiàn),第一級(jí)采用共源共柵結(jié)構(gòu),共源共柵級(jí)特點(diǎn)是高電壓增益,第二級(jí)采用共源結(jié)構(gòu),共源級(jí)特點(diǎn)是大擺幅,根據(jù)各級(jí)電路特點(diǎn),分配功率增益;然后根據(jù)功率分配確定第一級(jí)的最優(yōu)輸出負(fù)載和第二級(jí)的最優(yōu)輸入負(fù)載。通過測(cè)試輸入級(jí)的輸出最優(yōu)負(fù)載為160Ω,輸出級(jí)的最優(yōu)輸入阻抗為10Ω,以此為條件設(shè)計(jì)級(jí)間匹配網(wǎng)絡(luò)。

1.4 穩(wěn)定性設(shè)計(jì)

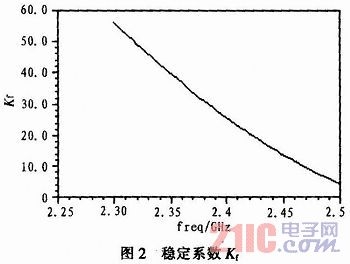

由于集成電容和集成電感以及寄生電容的影響,集成電路在某些條件下形成自激,通過仿真為電路繪制穩(wěn)定性圓,以此為依據(jù)修改電路圖。修改后仿真穩(wěn)定性參數(shù),Kf>1。仿真參數(shù)如圖2所示。進(jìn)行穩(wěn)定設(shè)計(jì)后,輸入0 dBm功率信號(hào)時(shí),輸出功率為25.22dBm。

2 射頻放大器電路結(jié)構(gòu)設(shè)計(jì)

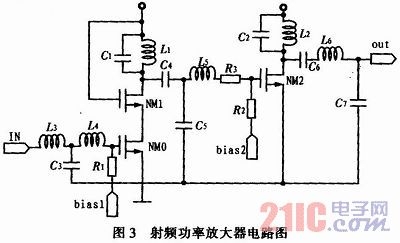

本射頻功率放大器采用兩級(jí)設(shè)計(jì),電路如圖3所示。第一級(jí)的共源共柵結(jié)構(gòu)是模擬電路中常采用的一種電路設(shè)計(jì)技術(shù),它能大幅提高輸出阻抗,很大程度上提高電壓增益,降低輸入級(jí)的Miller效應(yīng),提高輸入和輸出的隔離度,降低晶體管擊穿電壓的壓力,但此結(jié)構(gòu)在一定的擊穿電壓和供電電壓的情況下,降低了輸出電壓擺幅。第二級(jí)采用共源結(jié)構(gòu)實(shí)現(xiàn)功率放大,這種結(jié)構(gòu)可以充分利用大電壓擺幅,降低對(duì)輸出電流的要求,一定程度上減少晶體管的直流損耗。

在放大電路中NM1、NM2、L1、C1構(gòu)成第一級(jí)放大,M1、M2組成共源共柵結(jié)構(gòu),L1在低頻時(shí)提供直流偏置,在高頻時(shí)與C1諧振,形成高阻抗。如果要L1與M2漏極寄生電容和后級(jí)輸入電容諧振,L1無法片上集成,再者電路整體性能變差。L3、L4、C3構(gòu)成T形匹配網(wǎng)絡(luò),提供合理的S11參量,C4起到兩級(jí)電路間交流耦合的作用,L5、C5是級(jí)間匹配網(wǎng)絡(luò),提供級(jí)間最佳功率傳輸。NM3、L2、C2構(gòu)成輸出級(jí),提供大功率輸出,L2、C2在高頻時(shí)諧振,提供高輸出阻抗。由于L2只與M3漏極寄生電容諧振,L2很大,占用芯片面積較大,所以另加電容C2,以減少L2的量值。C6是隔直電容,L6、C7是輸出匹配網(wǎng)絡(luò),提供最優(yōu)輸出功。

2.1 前仿結(jié)果

使用Candence公司的SpectreRF軟件對(duì)電路進(jìn)行仿真,在2.4 GHz中心頻率上,在1 dB功率增益壓縮點(diǎn),輸出功率為25.0469dBm,如圖4所示;輸入0dBm功率信號(hào),輸出功率為252.2dBm,如圖5所示;穩(wěn)定因子Kf在工作頻段內(nèi)大于3;輸入反射系數(shù)S11<-14。

2.2 版圖結(jié)構(gòu)

版圖在Cadence環(huán)境下設(shè)計(jì)完成。版圖設(shè)計(jì)是制造集成電路的基礎(chǔ),在高頻集成電路設(shè)計(jì)中,版圖設(shè)計(jì)的好壞直接影響電路生產(chǎn)的成品率及可靠性。好的設(shè)計(jì)不但本身很少帶來不可靠因素,而且對(duì)于工藝上難以避免的問題,也可預(yù)防或減弱其影響。本次設(shè)計(jì)版圖主要考慮以下幾個(gè)方面的問題:1)功率放大器的輸出晶體管柵寬尺寸很大,為了減少柵極電阻和柵極電容對(duì)電路性能的影響,MOS管選用并聯(lián)和叉指布局設(shè)計(jì);2)功率放大器輸出級(jí)晶體管流過的電流很大,為了避免對(duì)周圍其他器件的影響,在輸出管周圍用隔離環(huán)進(jìn)行隔離;3)由于輸出級(jí)的電流很大,輸出級(jí)金屬線采用多層金屬,以此來減少流過金屬線的電流,避免金屬線過寬產(chǎn)生的寄生效應(yīng);4)在系統(tǒng)布局上,將輸入信號(hào)置于左邊,輸出信號(hào)置于右邊,從而減少高頻輸入信號(hào)和輸出信號(hào)之間的相互影響。

2.3 后仿結(jié)果

利用Candence公司的SpectreRF軟件對(duì)版圖提取的參數(shù)進(jìn)行后仿真,在2.4 GHz頻率0 dBm輸入功率時(shí),輸出功率為23 dBm在1 dB功率增益壓縮點(diǎn),輸出功率為21.36 dBm,在工作頻段內(nèi)穩(wěn)定因子Kf>6,在2.4 GHz處,Kf>10,,比較前后仿真數(shù)據(jù),輸出功率和漏極功率效率都有所下降,這是由于晶體管、電感、電容寄生參數(shù),以及襯底耗散的影響,使功率輸出沒有達(dá)到最優(yōu)。

3 結(jié)論

利用漏極寄生電容與射頻扼流電感諧振,這樣電感量很大,占用的芯片面積增加,為了減少芯片面積,用一電容與射頻扼流電感并聯(lián),在工作頻段內(nèi)諧振,以提供大阻抗。為了避免放大器發(fā)生自激現(xiàn)象,通過穩(wěn)定圓仿真,確定在相應(yīng)的電極加適當(dāng)電阻。

在3.3 V電源電壓下,通過負(fù)載線技術(shù),最大化利用晶體管的耐壓能力和驅(qū)動(dòng)電流能力;優(yōu)化輸入級(jí)的輸出電阻和輸出級(jí)的輸入電阻,通過級(jí)間匹配網(wǎng)絡(luò),達(dá)到級(jí)間最佳功率傳輸;基于輸入阻抗為復(fù)數(shù)的特點(diǎn),利用電感與寄生電容的諧振產(chǎn)生純輸入電阻,以此電阻為前提,設(shè)計(jì)輸入匹配網(wǎng)絡(luò),最后設(shè)計(jì)的匹配網(wǎng)絡(luò)為T形匹配網(wǎng)絡(luò)。

采用SMIC 0.35-μm CMOS射頻工藝,完成了2.4 GHz功率放大器的設(shè)計(jì)。應(yīng)用Candence公司的SpectreRF軟件對(duì)電路進(jìn)行后仿真,輸入0 dBm功率信號(hào),輸出功率為23 dBm。穩(wěn)定因子在工作頻段內(nèi)Kf>6,B1f>0,可實(shí)現(xiàn)全集成并工作于短距離小功率射頻收發(fā)系統(tǒng)中。