搭建一種低成本的嵌入式視覺系統(tǒng),,系統(tǒng)由CMOS圖像傳感器,、CPLD、ARM7微處理器以及SRAM構(gòu)成,。其中,,CPLD識別時序,解決了圖像采集系統(tǒng)存在的嚴(yán)格時序同步和雙CPU共享一片SRAM的總線競爭問題,;用Verilog語言編寫Mealy狀態(tài)機控制圖像數(shù)據(jù)寫入SRAM,,多路數(shù)據(jù)選擇器實現(xiàn)總線切換,避免了總線沖突,。圖像處理算法注重效率,基于ARM實現(xiàn),,系統(tǒng)最終工作速率為25幀/s,。

目前,關(guān)于視覺系統(tǒng)的研究已經(jīng)成為熱點,,也有開發(fā)出的系統(tǒng)可供參考,。但這些系統(tǒng)大多是基于PC機的,由于算法和硬件結(jié)構(gòu)的復(fù)雜性而使其在小型嵌入式系統(tǒng)中的應(yīng)用受到了限制,。上述系統(tǒng)將圖像數(shù)據(jù)采集后,,視覺處理算法是在PC機上實現(xiàn)的。隨著嵌入式微處理器技術(shù)的進步,,32位ARM處理器系統(tǒng)擁有很高的運算速度和很強的信號處理能力,,可以作為視覺系統(tǒng)的處理器,代替PC機來實現(xiàn)簡單的視覺處理算法,。下面介紹一種基于ARM和CPLD的嵌入式視覺系統(tǒng),,希望能分享嵌入式視覺開發(fā)過程中的一些經(jīng)驗。

1 系統(tǒng)方案與原理

在嵌入式視覺的設(shè)計中,,目前主流的有以下2種方案:

方案1 圖像傳感器+微處理器(ARM或DSP)+SRAM

方案2 圖像傳感器+CPLD/FPGA+微處理器+SRAM

方案1系統(tǒng)結(jié)構(gòu)緊湊,,功耗低。在圖像采集時,,圖像傳感器輸出的同步時序信號的識別需要借助ARM的中斷,,而中斷處理時,微處理器需要完成程序跳轉(zhuǎn),、保存上下文等工作[1],,降低了圖像采集的速度,適合對采集速度要求不高、功耗低的場合,。

方案2借助CPLD來識別圖像傳感器的同步時序信號,,不必經(jīng)過微處理器的中斷,因而系統(tǒng)的采集速度提高,,但CPLD的介入會使系統(tǒng)的功耗提高,。

為了綜合以上2種方案的優(yōu)勢,在硬件上采用“ARM+CPLD+圖像傳感器+SRAM”,。該方案充分利用了CPLD的可編程性,,通過軟件編程來兼有方案1的優(yōu)勢,具體體現(xiàn)在以下方面:

①功耗的高低可以控制,。對于功耗有嚴(yán)格要求的場合,,通過CPLD的可編程性將時序部分的接口與ARM的中斷端口相連,僅僅是組合邏輯的總線相連,,可以降低CPLD的功耗從而達到方案1的效果,;對于采集速度要求高而功耗要求不高的情況,可以充分發(fā)揮CPLD的優(yōu)勢,,利用組合與時序邏輯來實現(xiàn)圖像傳感器輸出同步信號的識別,,并將圖像數(shù)據(jù)寫入SRAM中。

②器件的選擇可以多樣,。在硬件設(shè)計上,,所有總線均與CPLD相連;在軟件設(shè)計上,,不同的模塊單獨按功能封裝,。這樣以CPLD為中心,系統(tǒng)的其他器件均可更換而無需對CPLD部分程序進行改動,,有利于系統(tǒng)的功能升級,。

作為本系統(tǒng)的一種應(yīng)用,開發(fā)了視覺跟蹤的程序,,可以在目標(biāo)和背景顏色對比強烈的情況下對物體進行跟蹤,。通過對CMOS攝像頭采集來的數(shù)據(jù)進行實時處理,根據(jù)物體的顏色計算出被追蹤物體的質(zhì)心坐標(biāo),。下面分別描述系統(tǒng)各部分的功能,。

2 系統(tǒng)硬件

2.1 硬件組成及連接

系統(tǒng)的硬件主要有4部分:CMOS圖像傳感器OV6620、可編程器件CPLD,、512 KB的SRAM和32位微處理器LPC2214,。

OV6620是美國OmniVision公司生產(chǎn)的CMOS圖像傳感器,以其高性能,、低功耗適合應(yīng)用在嵌入式圖像采集系統(tǒng)中,,本系統(tǒng)圖像數(shù)據(jù)的輸入都是通過OV6620采集進來的,;可編程器件CPLD采用Altera公司的EPM7128S,用Verilog硬件編程語言在QuartusII下編寫程序,;作為系統(tǒng)的數(shù)據(jù)緩沖,,SRAM選用的是IS61LV5128,其隨機訪問的特性為圖像處理程序提供了便利,;而LPC2214在PLL(鎖相環(huán))的支持下最高可以運行在60 MHz的頻率下,,為圖像的快速處理提供了硬件支持。

OV6620集成在一個板卡上,,有獨立的17 MHz晶振,。輸出3個圖像同步的時序信號:像素時鐘PCLK、幀同步VSYNC和行同步HREF,。同時,,還可以通過8位或16位的數(shù)據(jù)總線輸出RGB或YCrCb格式的圖像數(shù)據(jù)。

在硬件設(shè)計上,,有2個問題需要解決:

①圖像采集的嚴(yán)格時序同步,;

②雙CPU共享SRAM的總線仲裁。

解決第一個問題的關(guān)鍵在于如何實時,、準(zhǔn)確地讀取OV6620的時序輸出信號,,據(jù)此將圖像數(shù)據(jù)寫入SRAM中。這里采用的解決方案是用CPLD來實現(xiàn)時序信號的識別以及圖像數(shù)據(jù)的寫入,。CPLD在硬件上可以識別信號的邊沿,速度更快,,通過Verilog語言編寫Mealy狀態(tài)機來實現(xiàn)圖像數(shù)據(jù)的SRAM寫入,,更加穩(wěn)定。

對于雙CPU共享SRAM,,可以通過合理的連接方式來解決,。考慮到CPLD的可編程性,,將OV6620的數(shù)據(jù)總線,,LPC2214的地址、數(shù)據(jù)總線以及SRAM的總線都連接到CPLD上,。通過編程來控制總線之間的連接,,只要在軟件上保證總線的互斥性,即在同一時刻有且僅有一個控制器(CPLD或者LPC2214)來操作SRAM的總線,,就可以有效地避免總線沖突,。這樣,硬件上的仲裁就可以通過軟件來保證,,該過程可以通過在CPLD中編寫多路數(shù)據(jù)選擇器來實現(xiàn),。

各器件之間的連接關(guān)系如圖1所示,。

圖1 系統(tǒng)結(jié)構(gòu)框圖

由圖1可見,微處理器的總線接在CPLD上,,在對功耗有嚴(yán)格要求的場合中,,只需要在CPLD中,將OV6620的同步時序信號所對應(yīng)的引腳與LPC2214連接在CPLD上的中斷引腳相連,,系統(tǒng)就可以轉(zhuǎn)換成方案1的形式,。對CPLD而言,引腳相連的僅僅是組合邏輯,,降低了功耗,。方案1的具體工作過程可見參考文獻[1]。而對于采集速度要求較高的場合,,CPLD部分的程序源代碼見本刊網(wǎng)站www.mesnet.com.cn——編者注,。下面重點介紹這種情況下的應(yīng)用。

2.2 工作過程

系統(tǒng)上電后,,首先由LPC2214通過I2C總線配置攝像頭的工作狀態(tài),,需要配置的主要有輸出圖像的數(shù)據(jù)格式、速率,、是否白平衡,,以及自動增益是否打開。配置完成后,,LPC2214發(fā)出圖像采集的信號給CPLD,,此時CPLD操作SRAM的總線,并通過對OV6620輸出時序的檢測將圖像數(shù)據(jù)寫入SRAM,。當(dāng)然,,寫入SRAM需要嚴(yán)格符合SRAM的操作時序。一幀圖像采集完成后,,CPLD置位標(biāo)志位來通知LPC2214,,如果LPC2214處于空閑狀態(tài),則通知CPLD將總線使用權(quán)切換至LPC2214,,由LPC2214讀取SRAM中的數(shù)據(jù)并進行圖像處理,。同時,發(fā)送信號給CPLD進行數(shù)據(jù)采集,,圖像的采集和處理將并行執(zhí)行,,提高了系統(tǒng)的工作效率。當(dāng)再次采集完一幀數(shù)據(jù)后,,重復(fù)上述過程,。

2.3 硬件方案的特點

LPC2214負(fù)責(zé)圖像處理,CPLD負(fù)責(zé)圖像數(shù)據(jù)的采集,,很好地實現(xiàn)了功能上的封裝,??梢钥吹剑珻PLD將與硬件時序相關(guān)的程序封裝,,與外界的接口僅為標(biāo)志狀態(tài)線以及數(shù)據(jù)采集總線,,極大地方便了系統(tǒng)的升級而無需改動圖像采集部分的硬件和軟件。甚至更換為其他型號功能更為強大的微處理器,,只要按照上述標(biāo)志狀態(tài)線的約定來操作,,系統(tǒng)仍然可以正常工作,增強了系統(tǒng)的兼容性和可移植性,。

3 系統(tǒng)軟件

系統(tǒng)軟件主要由ARM微處理器和CPLD兩部分程序構(gòu)成,。ARM部分的代碼使用C語言在ADS1.2環(huán)境下開發(fā),而CPLD部分則使用Verilog硬件語言在QuartusII下開發(fā),。

3.1 CPLD部分程序設(shè)計

CPLD的程序主要分為2部分:組合邏輯和時序邏輯,。組合邏輯主要完成總線仲裁,程序并不依賴CPLD的全局時鐘,;時序邏輯完成對信號的檢測,,根據(jù)SRAM的操作時序?qū)D像數(shù)據(jù)寫入。

在總線仲裁部分,,需要注意的是: 對CPLD而言,,不同的時刻同一總線的數(shù)據(jù)流入方向是不同的。因而在Verilog中,,需要聲明總線為雙向端口,。具體的總線仲裁程序如下:

對雙向端口的總線操作總結(jié)如下:

①需要控制信號指明端口在某一時刻的方向;

②輸出高阻即代表該雙向端口是輸入狀態(tài),,此時可以作為普通的輸入端口來使用,。

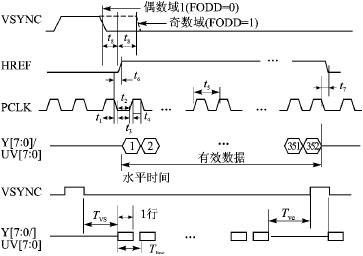

時序邏輯部分主要完成對圖像傳感器時序信號的識別。如圖2所示,,CPLD需要首先檢測VSYNC的下降沿,接著檢測HREF信號的上升沿,,然后在PCLK信號的上升沿將圖像數(shù)據(jù)讀入,。

圖2 OV6620輸出時序圖

在Verilog語言中,對上升沿的檢測是通過always語句來實現(xiàn)的,。例如檢測時鐘信號cam_pclk的上升沿:always@(posedge cam_pclk),。但從上面的分析中可以看出,需要檢測的信號沿有3個,,可以都用always來檢測,,但在Verilog的語法中always語句是不可以嵌套的。為了解決這個問題,,本系統(tǒng)中采用了如下方式:整個模塊只有一個時序邏輯的always塊,,其他的信號沿檢測用與always等價的方式實現(xiàn),。例如對于cam_vsyn信號,設(shè)置2個臨時信號vsyn_0和vsyn_1,,在每個時鐘信號的上升沿,,進行如下賦值:

vsyn_1 <= cam_vsyn;//臨時信號賦值

vsyn_0 <= vsyn_1,;

這樣,,當(dāng)每個時鐘沿到來時都會更新vsyn_0和vsyn_1的值。當(dāng)vsyn_0的值為0且vsyn_1的值為1時,,認(rèn)為是上升沿到來,,同理也可以檢測下降沿。需要注意的是:這種方式下,,時鐘信號的周期要遠(yuǎn)遠(yuǎn)小于被檢測信號的高電平和低電平的持續(xù)時間,。如果信號脈沖過窄,在整個脈沖期間vsyn_0和vsyn_1的值都沒有更新,,就會丟失邊沿的檢測,。

數(shù)據(jù)寫入SRAM的過程是用Mealy狀態(tài)機來實現(xiàn)的,程序具有通用性,。若使用其他型號的SRAM,,只需要根據(jù)器件的讀寫時序在相應(yīng)的狀態(tài)中修改高低電平。狀態(tài)機使程序的結(jié)構(gòu)清晰,,調(diào)試方便,。

3.2 ARM部分程序設(shè)計

目前,基于PC機的視覺處理算法有很多,,但在基于微處理器的嵌入式視覺系統(tǒng)中,,系統(tǒng)在硬件資源和處理速度上都無法與PC機相比。特別是在有實時性要求的情況下,,需要編寫適合嵌入式系統(tǒng)特點的快速有效的算法,。下面編寫的算法都是根據(jù)這個思想來編寫的。

顏色跟蹤:顏色跟蹤的任務(wù)可以分解為顏色標(biāo)定和顏色分割兩個步驟,。顏色標(biāo)定的任務(wù)是通過一個已知的顏色,,找出其在顏色空間內(nèi)與之對應(yīng)的一個封閉區(qū)域。顏色分割則是通過比較器判斷圖像中像素點在顏色空間中是否落在標(biāo)定的空間內(nèi),,若在已標(biāo)定的空間內(nèi),,則認(rèn)為其顏色與已標(biāo)定的顏色一樣,這樣就可以根據(jù)標(biāo)定的封閉區(qū)域識別出圖像中具有與標(biāo)定顏色相同的物體,。

為了滿足不同情況下應(yīng)用的需求,,顏色跟蹤設(shè)置了2種模式。

(1)幀處理模式

該模式需要用戶輸入要跟蹤的R,、G,、B三個顏色邊界,,構(gòu)成一個RGB跟蹤的顏色空間。然后處理器從圖像的左上角開始,,順序逐行逐點的檢查每一個像素,。如果被檢查的像素正好落入用戶定義的顏色范圍,就將這個像素標(biāo)記為跟蹤的,;同時,,需要記錄被跟蹤點中的最高點、最低點,、最左點和最右點,。如果檢測到的像素位置在當(dāng)前跟蹤區(qū)域的標(biāo)記框外,則需要增大標(biāo)記框來包含該像素,;同時,,需要記錄符合要求的像素的數(shù)量,當(dāng)一幀圖像掃描完成后,,可以分別用符合要求的點的橫縱坐標(biāo)和除以符合要求的像素點數(shù),,得出被追蹤物體的中心坐標(biāo)[3]。

這樣在對一幀圖像的一次掃描后,,就可以得到被跟蹤物體的中心坐標(biāo),,同時處理器只需記錄較少的全局變量,在時間復(fù)雜度和空間復(fù)雜度上都適合嵌入式系統(tǒng),。

上述方法中,,只有一個跟蹤點就可以改變標(biāo)記框,因此如果在跟蹤過程中出現(xiàn)噪聲點,,就會對標(biāo)記框產(chǎn)生影響,。去噪的思想是:如果一個像素點周圍的其他點也落在用戶輸入的RGB范圍內(nèi),那么這個點就被認(rèn)為是符合要求的,。

(2)行處理模式

與幀處理模式不同的是,,行處理模式在掃描完一行數(shù)據(jù)后就記錄下所在行中符合要求的連續(xù)點的最左端坐標(biāo)和最右端坐標(biāo),不妨分別記為(XnL,,YnL)和(XnR,,YnR)。在一幀圖像處理完成后,,會得到圖3所示的圖形,。

圖3 行處理得到的線形圖

根據(jù)得到的結(jié)果,,可以計算出更多關(guān)于跟蹤物體的信息:

①計算區(qū)域面積,。計算每條線段的長度l(n),然后將l(n)進行累積疊加,,即可獲得跟蹤區(qū)域面積值S,。

![]()

②計算質(zhì)心橫坐標(biāo),。

③計算質(zhì)心縱坐標(biāo)。

④識別物體的形狀,。根據(jù)得到的每行跟蹤點的長度,,以及同一行中有幾段符合要求的連續(xù)跟蹤點,可以得知物體從攝像頭角度看到的形狀,。特別是在檢測平面上線條時,,可以識別是否有分支,這一點是幀處理模式無法做到的,。

需要指出的是,,行處理模式雖然會得到關(guān)于跟蹤目標(biāo)的更多信息,但是每行處理的方式增大了處理器的負(fù)擔(dān),,處理速度也沒有幀處理快,。

4 提高系統(tǒng)的工作速率

目前,系統(tǒng)工作在幀處理模式下的工作速率是25幀/s,,作為系統(tǒng)功能的驗證,,這里采用的算法是顏色跟蹤。如果僅做純粹的圖像采集,,而不做圖像處理,,那么系統(tǒng)可以達到OV6620的最高工作速率,即60幀/s,。而在圖像處理方面,,不同的圖像處理程序效率對系統(tǒng)的工作頻率有較大的影響。下面給出在通用ARM處理器下提高程序效率的幾個建議:

①內(nèi)嵌(inline)可通過刪除子函數(shù)調(diào)用的開銷來提高性能,。如果函數(shù)在別的模塊中不被調(diào)用,,一個好的建議是用static標(biāo)識函數(shù);否則,,編譯器將在內(nèi)嵌譯碼里把該函數(shù)編譯成非內(nèi)嵌的,。

②在ARM系統(tǒng)中,函數(shù)調(diào)用過程中參數(shù)個數(shù)≤4時,,通過R0~R3傳遞,;參數(shù)個數(shù)>4時,通過壓棧方式傳遞(需要額外的指令和慢速的存儲器操作),。通常限制參數(shù)的個數(shù),,使它為4或更少。如果不可避免,,則把常用的前4個參數(shù)放在R0~R3中,。

③在for(),while() do…while()的循環(huán)中,用“減到0”代替“加到某個值”,。比如:

for (loop = 1,;loop <= total;loop++) //ADD和CMP

替換為:for (loop = total,;loop != 0,;loop--) //SUBS

第1種方式比較需要2條指令A(yù)DD和CMP,而第2種方式只需一條指令SUBS,。

④ARM核不含除法硬件,,除法通常用一個運行庫函數(shù)來實現(xiàn),運行需要很多個周期,。一些除法操作在編譯時作為特例來處理,,例如除以2的操作用左移代替余數(shù)的操作符“%”,通常使用模算法,。如果這個值的模不是2的n次冪,,則將花費大量的時間和代碼空間避免這種情況的發(fā)生。具體辦法是使用if()作狀態(tài)檢查,。

比如,,count的范圍是0~59:

count = (count+1) % 60;

用下面語句代替:

if (++count >= 60)

count = 0,;

⑤避免使用大的局部結(jié)構(gòu)體或數(shù)組,,可以考慮用malloc/free代替。

⑥避免使用遞歸,。

結(jié)語

本文介紹了一種基于ARM和CPLD的嵌入式視覺系統(tǒng),,可以實現(xiàn)顏色跟蹤。在硬件設(shè)計上,,圖像采集和圖像處理分離,,更利于系統(tǒng)功能的升級。而視覺處理算法更注重處理的效率和實時性,,同時根據(jù)不同的需要有兩種模式可供選擇,。最后給出了提高程序效率的一些建議和方法。與基于PC機的視覺系統(tǒng)相比,,該系統(tǒng)功耗低,、體積小,適合應(yīng)用于移動機器人等領(lǐng)域,。