直接數(shù)字式頻率合成器以其極高的頻率分辨率、極短的頻率轉(zhuǎn)換時間、相位精確可調(diào)、設(shè)備結(jié)構(gòu)簡單、易集成、體積小及成本低等優(yōu)點,在高分辨雷達系統(tǒng)、寬帶擴頻通信系統(tǒng)以及現(xiàn)代測控系統(tǒng)中得到廣泛的應(yīng)用。為了便于信息的采集、處理和操作控制,常常要求信號源基于PC機平臺設(shè)計。PC機內(nèi)部有兩種常用的總線,即PCI總線和ISA總線。ISA總線接口關(guān)系簡單.操作控制方便,能夠滿足系統(tǒng)要求,是比較理想的DDS與計算機的接口總線。隨著電子系統(tǒng)復(fù)雜性的不斷增加,單路DDS已經(jīng)不能夠滿足系統(tǒng)需求,多路DDS系統(tǒng)的設(shè)計開始成為研究的熱點。

1 系統(tǒng)工作原理

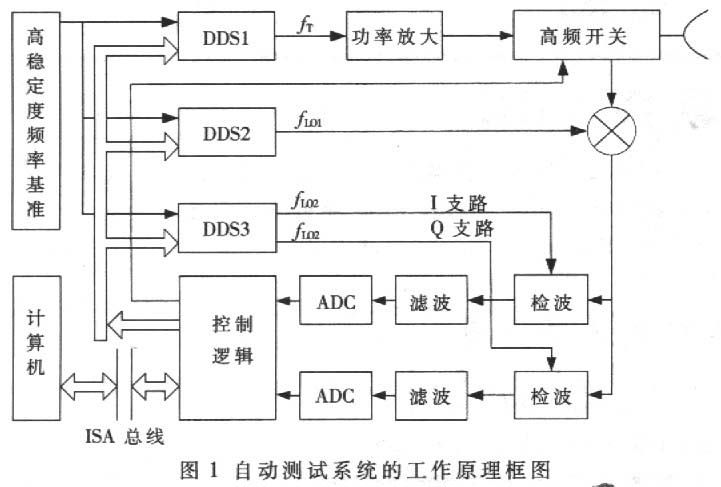

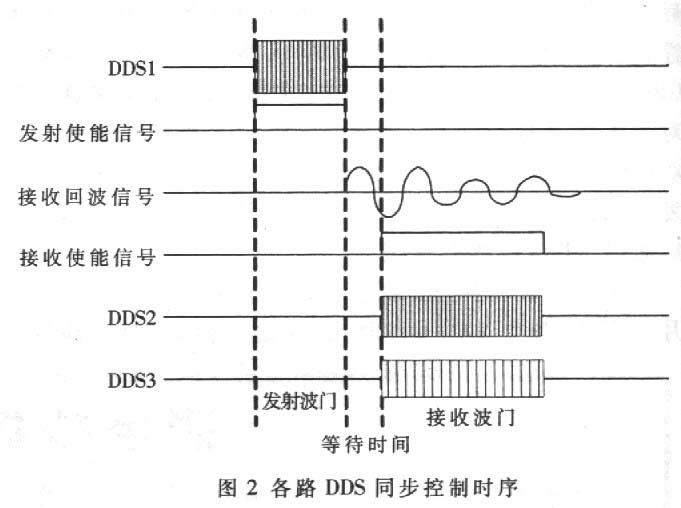

圖1是某自動測試系統(tǒng)的工作原理框圖。圖中的高穩(wěn)定度頻率基準(zhǔn)為整個系統(tǒng)提供頻率為50MHz的參考時鐘。系統(tǒng)的控制命令由計算機發(fā)出,經(jīng)過ISA總線傳輸,送到FPGA進行緩存、譯碼,同步控制三路DDS產(chǎn)生需要的信號。其中,DDS1的輸出信號為初始相位可變,脈沖寬度、脈沖周期、脈沖個數(shù)等由計算機編程設(shè)定的射頻脈沖序列。脈沖的載波頻率在fT=2lMHz附近可調(diào)。該射頻脈沖經(jīng)過功率放大、低通濾波后,在高頻開關(guān)的控制下發(fā)射出去。接收到的反射回波由高頻開關(guān)選通,與DDS2產(chǎn)生的20MHz第一本振fLO1混頻,得到頻率為1MHz的中頻脈沖調(diào)制正弦信號。該中頻信號再分成兩路,分別與DDS3輸出的頻率為1MHz二本振fLO2的1支路和Q支路兩路脈沖調(diào)制正交信號進行相位檢波,得到的信號經(jīng)低通濾波、模數(shù)轉(zhuǎn)換,送到計算機進行數(shù)據(jù)處理。為保證收發(fā)信號有效可靠地隔離,在發(fā)射波門和接收波門之間插入等待時間。各路信號之間的關(guān)系如圖2所示。為簡便起見,圖中只畫出了DDS3輸出的I、Q兩路信號中的一路,這不影響對信號控制時序的理解。

為了便于信號處理,該系統(tǒng)對各路DDS輸出信號的時間關(guān)系提出了嚴(yán)格的要求:(1)相位檢波器的兩路正交參考信號相位應(yīng)嚴(yán)格控制在90°相差上,以保證正交檢波器的性能。(2)其初始相位可以通過計算機控制調(diào)整。(3)DDS2的輸出信號和DDS3的I支路輸出信號必須同步,以保證在DDS3同相支路上的信號相位與中頻信號的相位保持同步;同時Q路信號必須保持相位的正交。(4)每個射頻脈沖周期,各路DDS輸出信號的初始相位嚴(yán)格同步,保證回波信號的相參積累。

2 多路同步設(shè)計

圖3是該自動測試系統(tǒng)的數(shù)據(jù)采集、多路DDS同步單元的實現(xiàn)框圖。經(jīng)過相位檢波、低通濾波的I、0兩路信號輸入到該單元電路中,經(jīng)OP-07放大、AD976采集后,再經(jīng)FPGA由ISA總線送入到計算機中。OP-07具有低偏移、高開環(huán)增益的特點,適合于高增益的測試系統(tǒng)應(yīng)用。AD976是采樣速率為200ksps的高速16位低功耗模數(shù)轉(zhuǎn)換器。FPGA芯片采用Ahera公司的ACEX系列芯片EPlK50,實現(xiàn)ISA總線與三路DDS及數(shù)據(jù)采集的接口。其靈活的可重新配置特性為實現(xiàn)接口電路提供了極大的方便,片上集成有4OKbit的RAM,便于緩存計算機的控制信息。DDS芯片選擇美國模擬器件公司的AD9854。它的相位累加器為48位,利用片上PLL可實現(xiàn)4~20倍的可編程倍頻,內(nèi)部最高時鐘可達300blHz,尤為突出的優(yōu)勢在于具有100MHz的高速并行配置接口,內(nèi)置最大相位誤差小于1°的I、Q兩路的DAC輸出,便于產(chǎn)生lMHz的正交信號。對于該自動測試系統(tǒng),各路DDS之間的同步關(guān)系是電路設(shè)計的核心問題。AD9854芯片本身沒有同步信號,要實現(xiàn)各路的精確同步,必須對電路進行優(yōu)化設(shè)計。為分析方便,分別從參考時鐘、刷新時鐘和內(nèi)部鎖相倍頻三部分進行討論。

2.1 參考時鐘

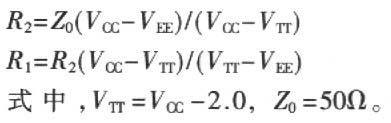

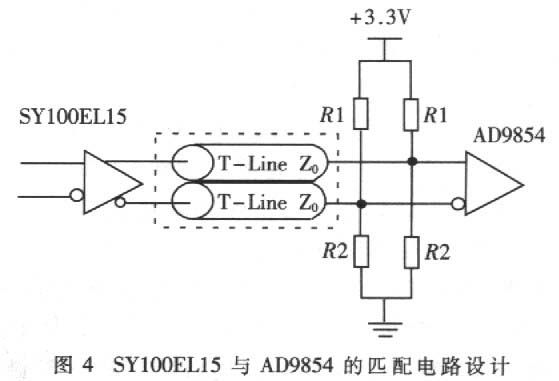

成功的同步設(shè)計要求各路DDS的參考時鐘之間的相位差最小。參考時鐘邊沿的時間差會使各路DDS輸出信號產(chǎn)生相應(yīng)比例的相位差。參考時鐘的邊沿抖動要足夠小,上升/下降時間要短,以免增加時鐘信號的相位誤差。數(shù)據(jù)采集與多路DDS單元電路首先把外部送來的50MHz高精度、高穩(wěn)定度的正弦信號轉(zhuǎn)換成方渡,送給各路DDS作參考時鐘。時鐘轉(zhuǎn)換功能利用1:4的PECL時鐘分配器SYl00EL15實現(xiàn)。ECL電路是現(xiàn)有各種實用數(shù)字邏輯集成電路中速度最快的一種,也是目前惟一能夠提供亞毫微秒開關(guān)時間的實用數(shù)字邏輯電路。SYl00EL15最高可以工作在1.25GHz頻率上,器件間的最大偏斜為200ps,單個器件的最大偏斜為50ps,時鐘均方抖動僅為2.6ps,上升時間介于325ps和575ps之間。AD9854的參考時鐘能夠兼容PECL邏輯。射頻信號在長線傳輸過程中,為了抑制由此產(chǎn)生的反射和串?dāng)_,SY100EL15的輸出與AD9854參考時鐘之問的PECL邏輯電路必須良好地匹配。圖4的匹配方式是一種比較好的方案。圖中:

對于3.3V供電的LVPECL電路,R1取126Ω,R2取82.5Ω。AD9854的時鐘輸入電路有單端方式和差分方式兩種,采用差分方式有利于抑制電路產(chǎn)生共模噪聲。時鐘分配網(wǎng)絡(luò)布線時,要保證每一路差分時鐘信號的走線等長,并且各路DDS時鐘信號之間的走線也應(yīng)當(dāng)?shù)乳L。電路板應(yīng)該按照微帶線設(shè)計。不同的微帶線結(jié)構(gòu)將導(dǎo)致信號傳輸常數(shù)有所差異。

2.2 刷新時鐘

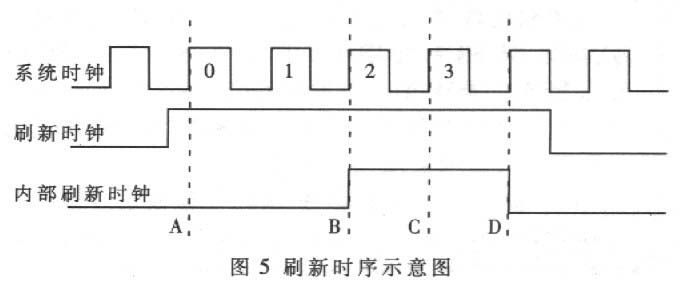

AD9854芯片引腳中與配置內(nèi)核密切相關(guān)的信號除了數(shù)據(jù)線、地址線、寫信號以外,還有刷新時鐘。寫信號的作用是將I/O口上的數(shù)據(jù)傳送到AD9854芯片內(nèi)部的緩沖區(qū)中,而刷新時鐘則用于配置AD9854內(nèi)核的相應(yīng)寄存器。刷新時鐘引腳既可以作為輸入信號,工作于外部刷新模式;又可以作為輸出信號,工作于內(nèi)部刷新模式。鑒于多路同步原因,通常工作于外部刷新模式。刷新信號的時序如圖5所示。從AD9854內(nèi)部看,刷新時鐘UPDATE實際上是電平有效信號。在該信號出現(xiàn)于AD9854引腳后的第一個系統(tǒng)時鐘上升沿,即A時刻,系統(tǒng)時鐘識別到刷新時鐘。在第三個系統(tǒng)時鐘的上升沿,產(chǎn)生AD9854芯片DDS內(nèi)核的內(nèi)部刷新時鐘。該信號與系統(tǒng)刷新時鐘同步,作為將I/O口上的數(shù)據(jù)配置到AD9854內(nèi)部配置寄存器的時鐘信號。在第四個系統(tǒng)時鐘的上升沿,完成對內(nèi)部寄存器的配置。在第五個時鐘的上升沿,產(chǎn)生內(nèi)部刷新時鐘信號的下降沿,配置過程結(jié)束。以圖5為例,為使該過程工作可靠,應(yīng)當(dāng)保證三路DDS芯片的刷新時鐘必須超前于相同的系統(tǒng)時鐘,即時鐘0,否則會導(dǎo)致各路DDS的輸出相差一個AD9854的系統(tǒng)時鐘。

2.3 鎖相倍頻

根據(jù)數(shù)模轉(zhuǎn)換的數(shù)學(xué)模型,DDS輸出信號的頻率通常不得超過系統(tǒng)時鐘頻率的40%。以50MHz作為參考時鐘產(chǎn)生頻率為20MHz的信號會給濾波帶來困難。AD9854內(nèi)部集成了鎖相倍頻電路,可以將50MHz的參考時鐘倍頻至200MHz。片上鎖相倍頻電路帶來的問題是環(huán)路建立時間會隨著AD9854及片外環(huán)路濾波器的器件不同而產(chǎn)生差異。這將導(dǎo)致在鎖相環(huán)路的建立過程中,送給AD9854相位累加器的系統(tǒng)時鐘周期數(shù)目無法準(zhǔn)確預(yù)測。因此在環(huán)路建立過程中,相位控制字的值必須為零以避免相位累加器的值不斷累加。DDS芯片內(nèi)部集成鎖相環(huán)路的建立時間典型值約為400μs。為了保證各路DDS的同步,在起始10ms讓AD9854輸出的頻率控制字和相位控制字始終為零。10ms以后,才啟動AD9854的輸出相位累加過程。待PLL建立起來以后,再改變各路DDS芯片相應(yīng)的控制字。

計算機的主控軟件用VB語言編寫,系統(tǒng)FPGA軟件用VHDL語言編寫。FPGA內(nèi)部設(shè)計了一個基于FIFO技術(shù)的緩沖區(qū),將主控計算機發(fā)送過來的各類控制命令暫存。為了簡化控制時序,采用的方法是利用ISA總線的數(shù)據(jù)線依次傳輸各路AD9854的配置數(shù)據(jù)和寄存器地址,并且暫時存放在緩沖區(qū)中;而后利用ISA總線的寫信號作為各路AD9854的刷新時鐘信號,完成對DDS芯片的同步配置。

ISA總線信號源采用四層印刷電路板設(shè)計。布線時,采取電源退耦濾波、合理分割內(nèi)電層、隔離數(shù)字地和模擬地等措施,有效地克服了計算機內(nèi)部復(fù)雜的電磁干擾環(huán)境,得到了較好的測試結(jié)果。結(jié)果表明,信號在20MHz處的相位噪聲優(yōu)于一100dBc@lkHz,在O~0.5fs范圍內(nèi)的雜散抑制優(yōu)于-55dBc。以DDS的尉新信號作為同步參考信號,三路DDS(包括DDS3的I/Q兩路),從刷新時鐘上升沿到DDS有信號輸出,時間間隔均為305ns,能夠?qū)崿F(xiàn)精確的同步。

本文對基于計算機的DDS技術(shù)做了嘗試。在沒有增加屏蔽結(jié)構(gòu)的條件下。頻率合成器的相位噪聲和雜散指標(biāo)都滿足系統(tǒng)要求,針對AD9854,通過精心設(shè)計,實現(xiàn)了多路DDS的同步和IQ正交輸出。