摘要:在現(xiàn)代數(shù)字通信系統(tǒng)中,,為了擴大信道的傳輸容量提高信號傳輸效率,,常采用數(shù)字復(fù)接的技術(shù)。在分析了PCM30/32路系統(tǒng)基群信號幀結(jié)構(gòu)的基礎(chǔ)上,,以EDA綜合仿真設(shè)計軟件QuartusⅡ8.0為開發(fā)平臺,,利用Verilog HDL硬件描述語言進行系統(tǒng)建模,,設(shè)計了一種基于FPGA的同步數(shù)字信號復(fù)接系統(tǒng)。經(jīng)過對系統(tǒng)的功能仿真測試及綜合布局布線分析,,驗證了輸入/輸出的邏輯關(guān)系,,實現(xiàn)了系統(tǒng)中在發(fā)送端進行數(shù)字復(fù)接和接收端同步分解還原的設(shè)計要求,功能穩(wěn)定可靠,。

0 引言

數(shù)字通信系統(tǒng)包括發(fā)送設(shè)備,、接收設(shè)備和傳輸設(shè)備,在現(xiàn)代數(shù)字通信中,,為了擴大信道傳輸容量提高傳輸效率,,通常需要將若干低速數(shù)字碼流按一定的規(guī)范復(fù)接為一個高速數(shù)據(jù)碼流流,以便在高速寬帶信道中傳輸,。目前采用較多的技術(shù)是頻分多路復(fù)用和時分多路復(fù)用,,頻分多路復(fù)用適用于模擬通信,例如載波通信,;時分多路多復(fù)用適用于數(shù)字通信,,例如PCM通信。數(shù)字復(fù)接技術(shù)就是依據(jù)時分復(fù)用的基本原理完成數(shù)據(jù)碼流合并和分解還原的一種專門技術(shù),,并且是數(shù)字通信中的一項基礎(chǔ)技術(shù),。以往的數(shù)字復(fù)接系統(tǒng)大多采用模擬電路或傳統(tǒng)的ASIC設(shè)計,電路復(fù)雜龐大且受器件局限性約束,;由于近年來基于FPGA可編程器件的電路設(shè)計發(fā)展迅速,,可方便反復(fù)編寫和修改主程序及相關(guān)參數(shù),靈活性和穩(wěn)定性都很高,。本文以我國廣泛應(yīng)用的PCM30/32基群數(shù)字信號為例,,介紹這種基于FPGA流程設(shè)計的同步數(shù)字信號復(fù)接和分解方案,使用EDA仿真設(shè)計工具QuartusⅡ和Verilog HDL硬件描述語言對數(shù)據(jù)復(fù)接和分解的關(guān)鍵步驟進行功能仿真和驗證,。

1 PCM30/32路系統(tǒng)幀結(jié)構(gòu)介紹

時分復(fù)用的基本原理是將時間段分割成若干路時隙,,每一路信號分配一個時隙,幀同步碼和其他業(yè)務(wù)信號,、信令信號再分配一個或兩個時隙,,這種按時隙分配的重復(fù)性比特即為幀結(jié)構(gòu)。在PCM30/32路基群設(shè)備中是以幀結(jié)構(gòu)為單位,,將各種信息規(guī)律性地相互交插匯成2048Kb/s的高速碼流,。PCM30/32路系統(tǒng)的整個系統(tǒng)共分為32個路時隙,其中30個路時隙分別用來傳送30路話音信號,,一個路時隙用來傳送幀同步碼,,另一個路時隙用來傳送信令碼。

PCM30/32路系統(tǒng)中一個復(fù)幀(1復(fù)幀時間為2 ms)包含16幀,,編號分別為F0幀,,F(xiàn)1幀,,F(xiàn)2幀,…,,F(xiàn)15幀,,每幀(每一幀的時間為125μs)又包含有32個路時隙,其編號為TS0,,TS1,,TS2,…,,TS31,,每一路時隙時間為3.9μs,包含有8個位時隙,,其編號分別為D1,,D2,…,,D8,,每個位時隙的時間為0.488μs。其中TS1~TS15及TS17~TS31共30個時隙用于傳送第1~30路的信息信號,。偶幀的TS0時隙傳送幀同步碼,其碼型為{×0011011},;奇幀TS0時隙用于傳送幀失步對告和監(jiān)視告警碼等,,碼型為{×1A1SSSSS}。TS16時隙用于傳送復(fù)幀同步信號,、復(fù)幀失步對告及各路的信令(掛機,、撥號、占用等)信號,,當(dāng)TS16用于傳隨信令時,,它的安排是子幀F(xiàn)0的TS16時隙用于傳復(fù)幀失步對告碼及復(fù)幀同步碼,F(xiàn)1子幀的TS16時隙傳送第1路和第16路的信令信號,,F(xiàn)2子幀的TS16時隙傳送第2路和第17路信令信號,,依次類推,每一子幀內(nèi)的TS16時隙只能傳送2路信令信號碼,,這樣30路的信令信號傳送一遍需要15個子幀的TS16時隙,,每個話路信令信號碼的重復(fù)周期為1個復(fù)幀周期。綜上所述并結(jié)合抽樣理論,,每幀頻率應(yīng)為8000f/s,,幀周期為125μs,所以PCM30/32路系統(tǒng)基群信號總數(shù)碼率為:

![]()

2 同步數(shù)字復(fù)接技術(shù)原理

2.1 數(shù)字復(fù)接系統(tǒng)簡介

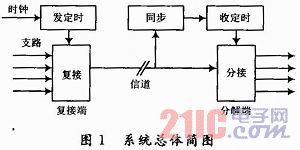

數(shù)字復(fù)接系統(tǒng)包括發(fā)送端和接收端兩部分,,通常稱為復(fù)接器(Digital Multiplexer)和分接器(Digital Demultiplexer),。數(shù)字復(fù)接器由定時單元和復(fù)接單元所組成,,是把2個或多個低速的支路數(shù)字信號按照時分復(fù)用方式合并成為一路高速的數(shù)字信號的設(shè)備;數(shù)字分接器是由同步,、定時和分接單元所組成,,是把合路數(shù)字信號分解還原為原來的支路數(shù)字信號的設(shè)備。定時單元給設(shè)備提供統(tǒng)一的基準(zhǔn)時間信號,;同步單元可以從接收到的復(fù)用信碼中提取與發(fā)送單元相位一致的同步時鐘信號以及幀同步信號,,從而真正實現(xiàn)數(shù)字復(fù)接系統(tǒng)的同步特性。在實際信號傳輸中,,發(fā)送端把低速數(shù)字信號合并為高速信號的同時,,常插入巴克碼用作幀同步碼,以便于解復(fù)用識別定位,;在接收端,,幀同步碼能否被準(zhǔn)確識別直接決定了能否正確地分接還原出各個支路信號。系統(tǒng)總體結(jié)構(gòu)簡圖如圖1所示,。

2.2 時分復(fù)接中的同步技術(shù)

數(shù)字通信中的同步技術(shù),,也稱為定時,包括位同步(也稱時鐘同步)和幀同步,,這是數(shù)字通信系統(tǒng)的一個重要特征,。位同步是最基本的同步,是實現(xiàn)幀同步的前提,,位同步的基本含義是收,、發(fā)兩端的時鐘頻率必須同頻、同相,,這樣接收端才能正確接收和判決發(fā)送端送來的每一個碼元,。為了達到收、發(fā)端頻率同頻,、同相,,在設(shè)計傳輸碼型時,一般要考慮傳輸?shù)拇a型中應(yīng)含有發(fā)送端的時鐘頻率成分,。這樣,,接收端從接收到的經(jīng)過復(fù)用的碼元信號中提取出發(fā)端時鐘頻率來進而得到同頻、同相的收端時鐘,,就可以做到位同步,;幀同步是為了保證收、發(fā)對應(yīng)的話路在時間上保持一致,,這樣接收端就能正確接收發(fā)送端送來的每一個話路信號,,當(dāng)然這必須是在位同步的前提下實現(xiàn)。為了建立收、發(fā)系統(tǒng)的幀同步,,需要在每一幀(或幾幀)中的固定位置插入具有特定碼型的幀同步碼,。這樣,只要收端能正確識別出這些幀同步碼,,就能正確辨別出每一幀的首尾,,從而能正確區(qū)分出發(fā)端送來的各路信號。上面介紹的PCM30/32路基群信號的TSO時隙傳輸?shù)膸叫盘柧褪菫榱藢崿F(xiàn)該功能,。

2.3 復(fù)用方法

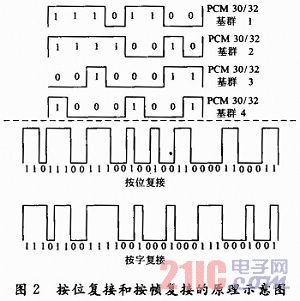

數(shù)字復(fù)接的方法主要有按位復(fù)接和按字復(fù)接,、按幀復(fù)接三種。對PCM基群信號來說,,一個碼字由8位碼組成,,代表一個樣值,所以該系統(tǒng)采用按字復(fù)接的方法,。每個復(fù)接支路依次輪流插入8位碼組成的碼字,。復(fù)接以后的合路信號碼流順序為:第1路的TS0,第2路的TS0,,第3路的TS0,,第4路的TS0;然后再是第1路的TS1,,第2路的TS1,,后面依次類推循環(huán)進行。這種方式完整保留了碼字的結(jié)構(gòu),,有利于多路合成處理和交換,。按字復(fù)接方法要求設(shè)備有較大的存儲容量,至少能存儲一個碼字,。

相對比而言,按位復(fù)接就是指每次只復(fù)接每個支路的一位碼字,,復(fù)接后的碼序列中第1時隙中的第1位表示第1支路第1位碼,,第2位表示第2支路第1位碼,后面依次類推,。各路的第1位碼依次取過以后,,再循環(huán)此后的各位碼,這種方法的特點是復(fù)接時每支路依次復(fù)接1 b,,對設(shè)備要求簡單,,但破壞了原來的樣值碼字結(jié)構(gòu);同理而言,,按幀復(fù)接是指每次復(fù)接一個支路的一幀數(shù)碼,,復(fù)接后的碼元序列相當(dāng)于把按字復(fù)接中的某一時隙替換為某一個幀信號。這種復(fù)接方法的特點是:每次復(fù)接一個支路的一幀信號,因此按幀復(fù)接時不破壞原來各幀的結(jié)構(gòu),,有利于信息交換,,但要求有很大容量的緩沖存儲器,電路結(jié)構(gòu)相對復(fù)雜,。如圖2所示為按位復(fù)接和按字復(fù)接的原理示意圖,。

3 基于FPGA的同步數(shù)字復(fù)接系統(tǒng)設(shè)計與實現(xiàn)

根據(jù)系統(tǒng)實現(xiàn)功能要求的特征,本文以Verilog HDL硬件描述語言為基礎(chǔ)對電路進行功能描述,,建立FPGA模型,,利用綜合仿真設(shè)計工具QuartusⅡ8.0對復(fù)用端和分解端分別進行系統(tǒng)功能仿真、綜合布局布線,,并結(jié)合仿真波形結(jié)果,,分析說明系統(tǒng)功能實現(xiàn)的正確性。

3.1 復(fù)用端電路設(shè)計原理

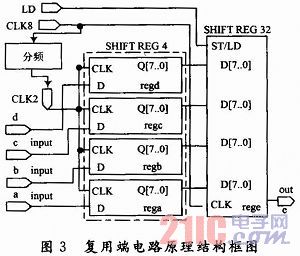

復(fù)用端主要由定時時鐘輸入,、時鐘分頻和復(fù)接模塊組成,,電路原理框圖如圖3所示。定義一路8MHz的定時時鐘輸入信號CLK8和4路2048Kb/s的PCM基群信號a,,b,,c,d為支路輸入,。定時時鐘通過分頻產(chǎn)生一路2MHz的模塊內(nèi)部時鐘信號,,并由模塊內(nèi)部邏輯產(chǎn)生一路LD控制信號。復(fù)接器主要完成功能為在2 MB時鐘控制下,,接受支路輸入的基群碼元信號,,每接收到8個碼元信號后將其分別鎖存在4個支路鎖存器re-ga,regb,,regc和regd中,,然后在LD控制下將其搬移到32位并入串出移位寄存器,同時在8MHz時鐘信號控制下串行輸入經(jīng)過復(fù)用的8196Kb高速信號e,,其中LD信號的周期被設(shè)計為PCM信號的一個時隙間隔,,系統(tǒng)利用時鐘的同步性可實現(xiàn)4路低速支路輸入和一路高速串行輸出,電路原理結(jié)構(gòu)圖如圖3所示,。

3.2 復(fù)用端功能仿真結(jié)果分析

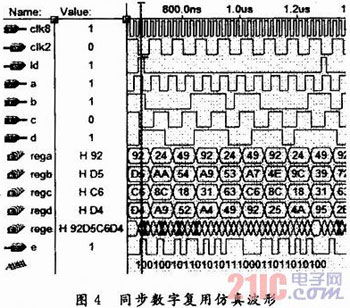

利用QuartusⅡ進行綜合仿真后,,加載波形進行功能仿真分析。由于一幀信號碼元信息太多,,為了便于分析,,對仿真結(jié)果截取了一個LD周期,也即一個時隙的碼元信號復(fù)用情況,。CLK2時鐘上升沿采集支路某一時隙碼元信號并存入鎖存器,,為方便表示,利用十六進制數(shù)據(jù)表示信號某時刻狀態(tài)值,如圖4所示,。

LD上升沿到來時刻,,支路寄存器采集到的一個時隙碼元信號情況值為:rega=10010010B(92H);regb=11010101B(D5H),;regc=11000110B(C6H),;regd=11010100B(D4H)。經(jīng)過時分同步復(fù)用后的高速輸出信號為:e=10010010110101011100011011010100B(92D5C6D4H),,信道傳輸速率提高了4倍,。碼元信號復(fù)用過程及仿真波形示意如圖4所示。

3.3 分解端電路設(shè)計原理

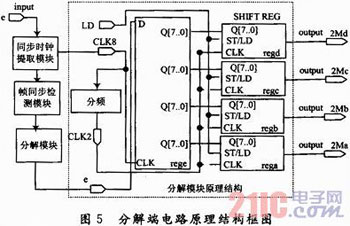

在分解端,,8MHz高速串行信號e首先經(jīng)過同步時鐘提取模塊,,根據(jù)串行數(shù)據(jù)的內(nèi)部特點,利用數(shù)字鎖相環(huán)等技術(shù)提取出和發(fā)送端同頻,、同相的時鐘信號CLK8,,然后經(jīng)過幀同步檢測模塊,建立狀態(tài)機對串行數(shù)據(jù)中的TS0時隙的幀同步碼元進行檢測,;這樣保證了接收端能夠準(zhǔn)確無誤的恢復(fù)發(fā)送端的數(shù)據(jù),。對于高速數(shù)據(jù)分解為4路支路信號的電路原理剛好和復(fù)用端相反,如圖5所示,。

3.4 分解端功能仿真結(jié)果分析

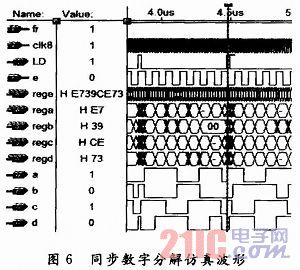

與復(fù)接端相反,,利用CLKS高頻時鐘讀取串行e的碼元信號到鎖存器rege中,LD信號為內(nèi)部邏輯產(chǎn)生的控制信號,,負責(zé)碼元分解搬移,。由于一幀信號容量過大,故截取了某幀內(nèi)的一個時隙以便于觀察分解還原功能的實現(xiàn),,在32個CLK8時鐘周期內(nèi)從串行輸入數(shù)據(jù)e采集到的碼元信號鎖存在rege移位寄存器中,,如圖6所示,rege=11100111001110011100111001110011B(E739CE73H),,從波形圖上可見分解后的支路鎖存實時狀態(tài)值為:rega=111001 11B(E7H),;regb=OO11l001B(39H);regc=11001110B(CEH),;regd=01110011B(73H),而恢復(fù)出4個支路的時隙碼元信號為:a:11100111,;b:00111001,;c:11001110;d:01110011,。分解過程及其信號分解還原波形如圖6所示,。

4 結(jié)語

本文主要依據(jù)PCM30/32基群信號的特點,結(jié)合FPGA建模仿真,利用QuartusⅡ8.0仿真綜合軟件,,實現(xiàn)4路低速信號的同步時分復(fù)用,,提高信號傳輸效率;并在分解端將其分解還原為4路原始信號,。功能仿真結(jié)果正確,,在允許的信號延時下實現(xiàn)了系統(tǒng)主要功能。系統(tǒng)基于FPGA的設(shè)計,,便于功能修改和擴展,,只需實時修改內(nèi)部參數(shù)即可。

作者:張華偉 宗瑞良 西北工業(yè)大學(xué) 來源:現(xiàn)代電子技術(shù)