引言

服務(wù)器、交換機(jī)、前端編碼器以及專用演播顯示器等廣播基礎(chǔ)設(shè)備系統(tǒng)支持各種輸入圖像格式,在存儲(chǔ)、編碼和顯示之前,通常需要將圖像轉(zhuǎn)換為高清晰(HD) 或者其他分辨率格式。專用ASSP 雖然滿足了這一市場需求,取得了一定的成功,但仍然面臨通過采用單芯片方案來滿足廣播設(shè)備供應(yīng)商各種特殊需求這一挑戰(zhàn)。例如,在交換機(jī)應(yīng)用中,總延時(shí)非常重要,延時(shí)是顯示和視頻會(huì)議系統(tǒng)的關(guān)鍵因素,而圖像質(zhì)量是攝制后期設(shè)備最重要的指標(biāo)。除了這些特殊應(yīng)用需求,器件還必須能夠支持各種幀速率、分辨率和格式。

而且,這類設(shè)備的設(shè)計(jì)周期相對較短,當(dāng)需求變化時(shí),設(shè)計(jì)人員沒有足夠的時(shí)間等待長周期ASSP 重制的完成。結(jié)果,很多優(yōu)秀的視頻技術(shù)ASSP 供應(yīng)商在這一領(lǐng)域未能及時(shí)跟上市場的腳步,被消費(fèi)類電子芯片生產(chǎn)商收購,為消費(fèi)類市場提供視頻處理專業(yè)技術(shù)。例如, Gennum (VXP)、Genesis、Silicon Optix 和LetIt Wave 分別被Sigma Designs、ST Micro、IDT 和Zoran 收購。

在這一ASSP 行業(yè)合并和重新定位過程中, FPGA 視頻處理功能不斷增強(qiáng),成為定制圖像格式轉(zhuǎn)換應(yīng)用的理想平臺(tái)。為支持加速實(shí)現(xiàn)FPGA 圖像格式轉(zhuǎn)換, Altera 開發(fā)了本白皮書介紹的1080p 視頻設(shè)計(jì)工作臺(tái),幫助系統(tǒng)設(shè)計(jì)人員輕松開發(fā)定制圖像格式轉(zhuǎn)換信號(hào)鏈。本文所討論的圖像格式轉(zhuǎn)換參考設(shè)計(jì)可以作為起點(diǎn),適當(dāng)修改后用于定制視頻處理應(yīng)用開發(fā)。本設(shè)計(jì)經(jīng)過硬件驗(yàn)證,可以提供給授權(quán)用戶。

1 視頻設(shè)計(jì)工作臺(tái)

Altera 視頻設(shè)計(jì)工作臺(tái)集成了各種工具和構(gòu)建模塊視頻功能,有助于加速定制圖像格式轉(zhuǎn)換設(shè)計(jì)的開發(fā)和實(shí)現(xiàn)。它包括以下組成:

■ 構(gòu)建模塊視頻知識(shí)產(chǎn)權(quán)(IP) 內(nèi)核

■ 格式轉(zhuǎn)換參考設(shè)計(jì),展示FPGA 功能,提供設(shè)計(jì)起點(diǎn)。

■ 低開銷開放視頻接口,支持混合匹配定制或者商用IP 模塊。

■ 用于集成處理器和存儲(chǔ)器子系統(tǒng)的系統(tǒng)級(jí)設(shè)計(jì)工具

■ 可迅速進(jìn)行原型設(shè)計(jì)的各種視頻開發(fā)套件

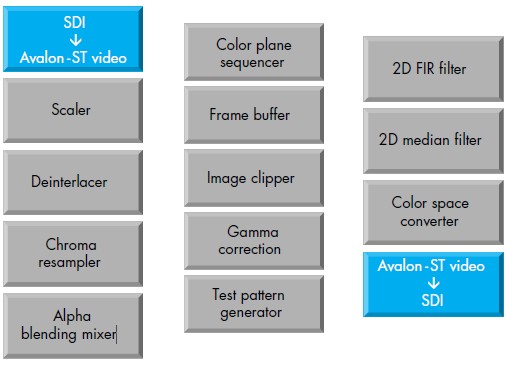

Altera 為視頻處理開發(fā)了各種構(gòu)建模塊,即,視頻和圖像處理(VIP) 包( 參見圖1)。在這一開發(fā)包的眾多功能中,縮放和去隔行是圖像格式轉(zhuǎn)換設(shè)計(jì)最常用的功能。Altera 的VIP 包具有復(fù)雜的多相縮放引擎和去隔行功能,可以配置實(shí)現(xiàn)運(yùn)動(dòng)自適應(yīng)去隔行功能。其他常用的功能包括色度重新采樣、顏色空間轉(zhuǎn)換以及幀速率轉(zhuǎn)換等,這些都含在VIP 包中。可以把這些視頻功能結(jié)合在一起,開發(fā)定制視頻格式轉(zhuǎn)換設(shè)計(jì)。

圖1. 視頻圖像處理(VIP) 包

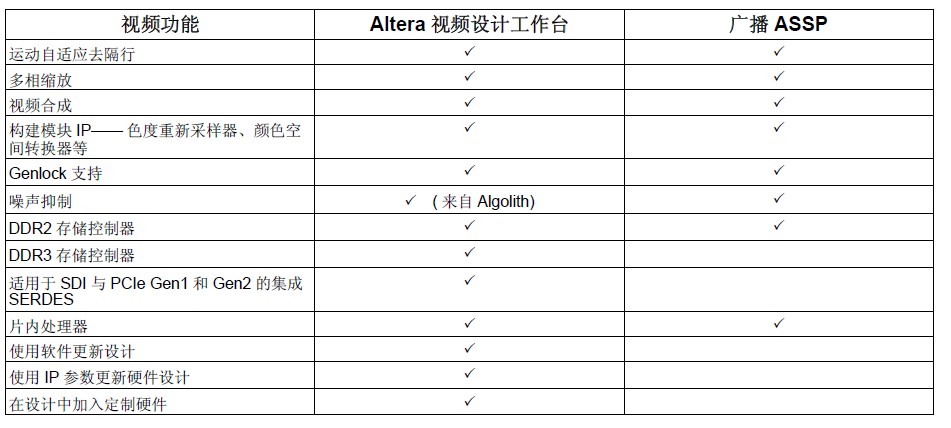

這一視頻設(shè)計(jì)工作臺(tái)提供以前由ASSP 實(shí)現(xiàn)的功能,還具有定制設(shè)計(jì)并進(jìn)行更新的優(yōu)點(diǎn)( 參見表1)。

表1. Altera 視頻設(shè)計(jì)工作臺(tái)與廣播ASSP 的對比

2 圖像格式轉(zhuǎn)換設(shè)計(jì)

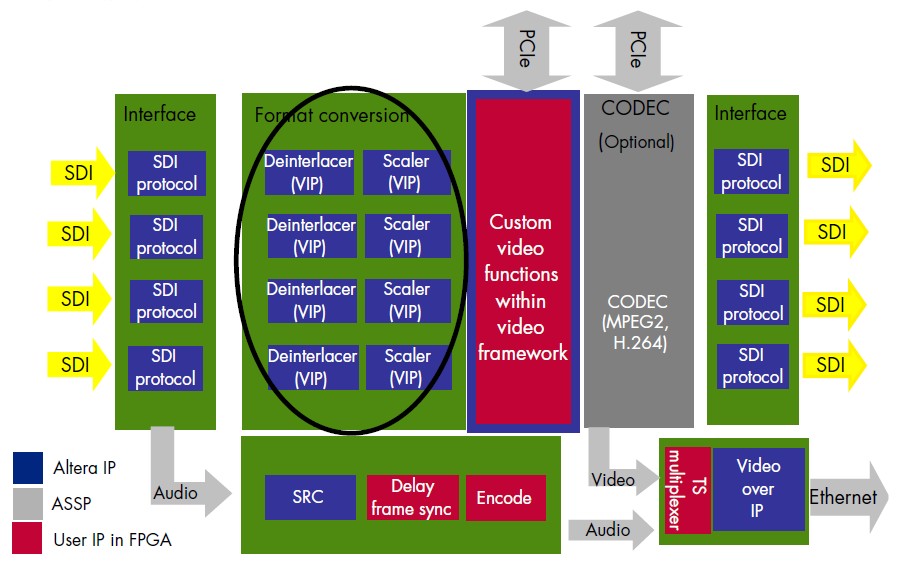

如圖2 所示,幾乎所有的演播系統(tǒng),包括服務(wù)器、交換機(jī)、前端編碼器和面板等都需要進(jìn)行定制圖像格式轉(zhuǎn)換,這是非常適合可編程FPGA 體系結(jié)構(gòu)的應(yīng)用。Altera 圖像格式轉(zhuǎn)換設(shè)計(jì)實(shí)現(xiàn)了隔行和逐行格式視頻標(biāo)準(zhǔn)清晰度(SD) 和HD 視頻流的高質(zhì)量上、下、交叉轉(zhuǎn)換。這一設(shè)計(jì)在硬件中進(jìn)行了驗(yàn)證,可以從當(dāng)?shù)谹ltera 現(xiàn)場應(yīng)用工程師(FAE) 那里獲得。

圖2. 典型演播系統(tǒng)的功能結(jié)構(gòu)圖

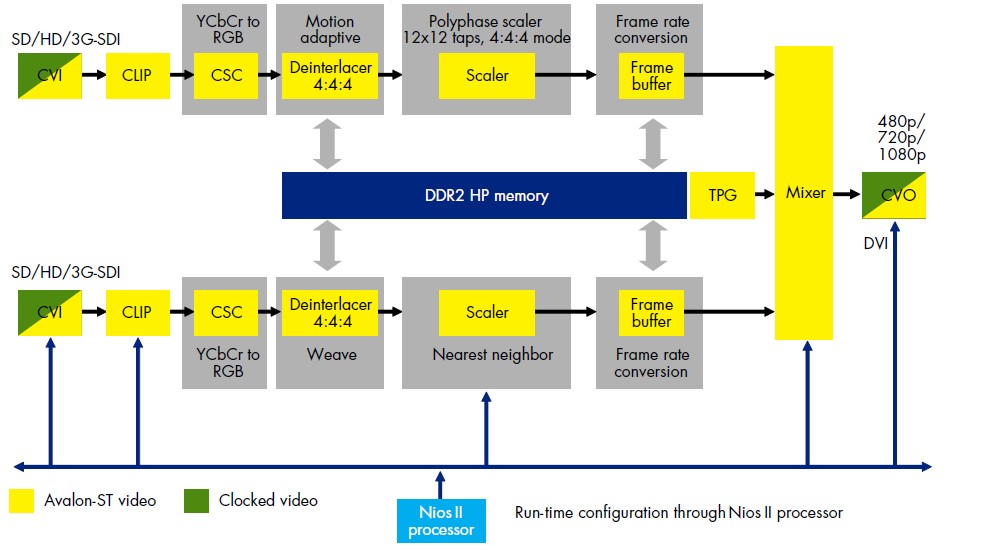

圖3 所示的格式轉(zhuǎn)換設(shè)計(jì)實(shí)現(xiàn)了雙通道視頻的圖像格式轉(zhuǎn)換。該設(shè)計(jì)包括兩路SDI 通道視頻,處理SD、HD 以及3G-SDI ( 全HD)。

圖3. Altera 采用視頻設(shè)計(jì)工作臺(tái)開發(fā)的圖像格式轉(zhuǎn)換設(shè)計(jì)

首先由同步視頻輸入MegaCore 功能來處理SDI 視頻數(shù)據(jù)。該功能將同步視頻格式數(shù)據(jù)( 例如, BT656 或者DVI) 轉(zhuǎn)換為流控制Avalon 流(Avalon-ST) 視頻協(xié)議,實(shí)現(xiàn)與數(shù)據(jù)通路后面其他視頻處理功能的鏈接。

采用高質(zhì)量視頻處理數(shù)據(jù)通路來處理第一個(gè)視頻通道。對每一輸入視頻圖像( 這個(gè)例子中是NTSC) 場的前三行進(jìn)行剪輯,輸出720x240 圖像。剪輯后的視頻數(shù)據(jù)在從YcbCr 顏色空間轉(zhuǎn)換為RGB 之前,經(jīng)過色度上采樣,轉(zhuǎn)換為YCbCr 4:4:4 格式。色度上采樣功能使用具有固定Lanczos-2 系數(shù)的4 抽頭濾波器。顏色空間轉(zhuǎn)換器也采用了取整( 向上半數(shù)取整) 算法,輸出8 位位寬數(shù)據(jù)。

然后,將視頻傳送至去隔行功能模塊。由于運(yùn)動(dòng)自適應(yīng)算法要求輸入顏色通道具有相同的采樣率,因此,在進(jìn)行去隔行處理之前,先進(jìn)行色度上采樣。( 今后的去隔行IP 將支持4:2:2 模式的視頻處理功能)。去隔行器經(jīng)過配置后,能夠同時(shí)接收逐行和隔行視頻。當(dāng)輸入視頻是隔行格式時(shí),運(yùn)動(dòng)自適應(yīng)算法產(chǎn)生逐行格式的視頻流。當(dāng)輸入視頻是逐行格式時(shí),去隔行器直接輸出數(shù)據(jù),不對其進(jìn)行處理。當(dāng)進(jìn)行運(yùn)動(dòng)自適應(yīng)去隔行處理時(shí),數(shù)據(jù)在外部存儲(chǔ)器中進(jìn)行緩沖,完成基本幀速率轉(zhuǎn)換處理。

然后,通過參數(shù)賦值縮放器功能( 具有12 個(gè)橫向和12 個(gè)縱向抽頭) 的多相算法對逐行視頻流進(jìn)行縮放。

采用Avalon 存儲(chǔ)器映射(Avalon-MM) 從機(jī)控制接口對縮放器進(jìn)行配置,支持縮放器輸出分辨率運(yùn)行時(shí)規(guī)范要求。此外,當(dāng)縮放比率變化時(shí), Nios? II 處理器上運(yùn)行的軟件計(jì)算并重新裝入合適的系數(shù),從而提高了圖像質(zhì)量。最后,在將視頻流與背景測試碼型以及第二個(gè)視頻流混合之前,幀緩沖功能在外部存儲(chǔ)器中緩沖視頻數(shù)據(jù)。兩路視頻流輸入到合成器進(jìn)行縮放和同步,需要對突發(fā)數(shù)據(jù)流進(jìn)行平滑處理。

第二個(gè)通道處理質(zhì)量稍差,這樣可以提高視頻格式轉(zhuǎn)換的資源利用率。主要有兩種方法來處理兩路不同格式的視頻流:

■ 使用簡單的最近鄰居縮放算法對第二個(gè)視頻流進(jìn)行縮放,需要較少的片內(nèi)存儲(chǔ)器和乘法器資源。

■ 使用場合并去隔行算法對第二個(gè)視頻流進(jìn)行去隔行處理,需要較少的邏輯資源和外部存儲(chǔ)器帶寬。

3 定制您的圖像格式轉(zhuǎn)換設(shè)計(jì)

Altera 視頻工作臺(tái)從根本上支持用戶定制設(shè)計(jì)。工作臺(tái)支持三級(jí)定制,非常靈活,如圖4 所示。在FPGA 領(lǐng)域,這種定制功能是前所未有的,采用ASSP 進(jìn)行設(shè)計(jì)是無法實(shí)現(xiàn)的。

圖4. Altera 視頻工作臺(tái)支持不同層面的定制功能

采用Altera 視頻工作臺(tái)開發(fā)設(shè)計(jì)時(shí),可以使用兩種創(chuàng)新技術(shù)實(shí)時(shí)進(jìn)行更新:

■ 數(shù)據(jù)包格式流接口——設(shè)計(jì)用于在功能模塊之間同時(shí)傳送視頻和控制數(shù)據(jù)包。

■ 算法功能模塊配置——可以配置為存儲(chǔ)器映射組件,通過寫入相應(yīng)的控制寄存器,實(shí)時(shí)更新功能。

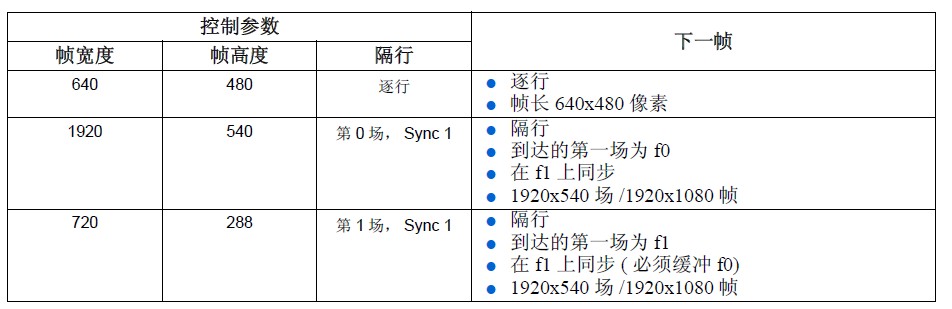

Avalon-ST 視頻協(xié)議是Altera 新的低開銷流協(xié)議,提供面向數(shù)據(jù)包的方法來發(fā)送視頻和控制數(shù)據(jù)。控制數(shù)據(jù)包用于發(fā)送動(dòng)態(tài)參數(shù),該參數(shù)描述流視頻幀格式。這些參數(shù)應(yīng)用于將要到達(dá)的下一視頻數(shù)據(jù)包,或者在編譯時(shí)設(shè)定,用在復(fù)位后接收到的第一個(gè)視頻數(shù)據(jù)包上。( 表2 列出了控制數(shù)據(jù)包是怎樣提供下一幀信息的)。數(shù)據(jù)到達(dá)時(shí),視頻數(shù)據(jù)流中的嵌入式控制數(shù)據(jù)包支持采用新數(shù)據(jù)對視頻處理流水線進(jìn)行重新配置。

表2. 控制數(shù)據(jù)包支持對視頻流格式的動(dòng)態(tài)更新

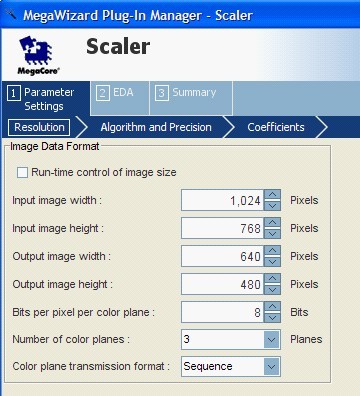

除了通過流接口實(shí)現(xiàn)運(yùn)行時(shí)更新, Altera 開發(fā)的大部分視頻功能模塊都具有運(yùn)行時(shí)更新功能。這表明,這些模塊使用存儲(chǔ)器映射從機(jī)接口,支持對狀態(tài)機(jī)和片內(nèi)處理器的更新。每個(gè)從機(jī)接口支持對一組控制寄存器的訪問。例如,可以使用片內(nèi)處理器,在運(yùn)行時(shí)更新這些控制寄存器。在新一幀的開始,更新后的控制數(shù)據(jù)被裝入到IP 功能模塊中。這樣,您可以在系統(tǒng)運(yùn)行時(shí)更新圖像大小和縮放系數(shù),改變縮放比。圖5 顯示了Altera 視頻工作臺(tái)多相縮放引擎是怎樣實(shí)現(xiàn)運(yùn)行時(shí)控制的。

圖5. 更新縮放功能

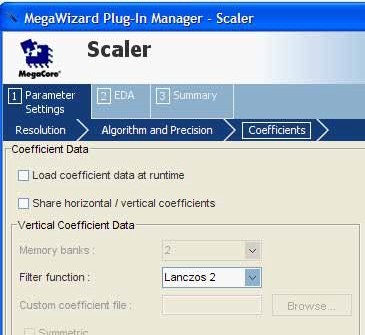

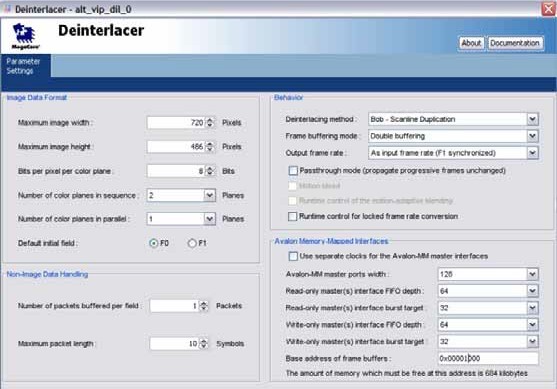

為進(jìn)一步定制設(shè)計(jì),您可以針對MegaCore 功能來修改參數(shù)。Altera 開發(fā)的所有視頻功能都是可以進(jìn)行參數(shù)賦值的。如圖6 所示,利用去隔行器功能,您不但可以選擇去隔行算法,還可以選擇默認(rèn)場、直通模式、外部存儲(chǔ)器緩沖幀數(shù)量、輸出幀速率和運(yùn)動(dòng)控制補(bǔ)償?shù)人惴ā?/p>

圖6. 參數(shù)賦值硬件功能模塊

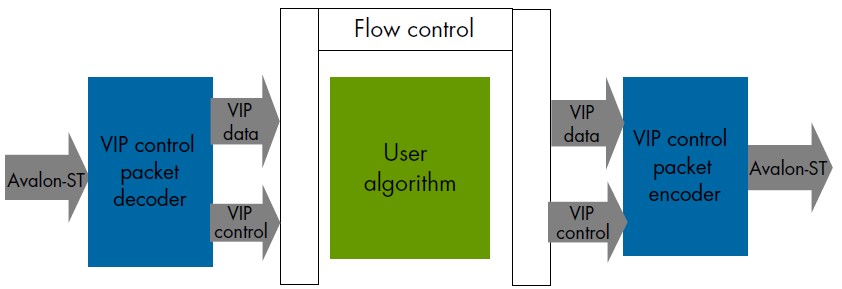

Avalon-ST 和Avalon-MM 接口標(biāo)準(zhǔn)的開放即插即用規(guī)范意味著您可以先進(jìn)行圖像格式轉(zhuǎn)換設(shè)計(jì),然后,采用定制模塊來替換Altera 模塊。很多設(shè)計(jì)人員都有適合自己應(yīng)用的定制算法。為實(shí)現(xiàn)定制算法的簡單集成,Altera 提供支持Avalon-ST 接口打包器的HDL 模板。打包器包括以下模塊:

■ VIP 控制數(shù)據(jù)包解碼器——從數(shù)據(jù)流中解碼VIP 控制數(shù)據(jù)包,將解碼后的數(shù)據(jù)( 寬度、高度、隔行信息)作為單獨(dú)的信號(hào)發(fā)送給算法功能模塊。

■ VIP 控制數(shù)據(jù)包編碼器——根據(jù)接收到的寬度、高度和隔行信息對VIP 控制數(shù)據(jù)包編碼,將其插入到數(shù)據(jù)流中。

■ VIP 流控制打包器——圍繞用戶算法進(jìn)行打包處理,實(shí)現(xiàn) Avalon-ST 與簡單讀寫接口的流控制轉(zhuǎn)換。

■ 用戶算法內(nèi)核——HDL 模板在用戶算法模塊中提供了簡單的設(shè)計(jì)實(shí)例。您可以采用自己的算法替代這一模塊。

圖7 所示為HDL 模板的高級(jí)結(jié)構(gòu)視圖。

圖7. Avalon 流HDL 模板

Algolith 作為Altera IP 合作伙伴,是視頻IP 領(lǐng)域的專業(yè)公司,采用了HDL 模板來評估其內(nèi)核。Algolith 開始時(shí)采用Altera 參考設(shè)計(jì)進(jìn)行圖像格式轉(zhuǎn)換,然后使用自己的專用運(yùn)動(dòng)自適應(yīng)去隔行器替代Altera 去隔行器,并提供給用戶,在硬件中進(jìn)行評估。同樣, Algolith 使用Altera 視頻設(shè)計(jì)工作臺(tái)開發(fā)了參考設(shè)計(jì),幫助用戶評估他們的噪聲抑制IP。

4 結(jié)論

Altera 視頻工作臺(tái)為廣播基礎(chǔ)實(shí)施系統(tǒng)實(shí)現(xiàn)圖像格式轉(zhuǎn)換提供所有必須的關(guān)鍵功能。采用Altera 視頻設(shè)計(jì)工作臺(tái)和圖像格式轉(zhuǎn)換參考設(shè)計(jì), FPGA 設(shè)計(jì)人員現(xiàn)在可以使用以前只有廣播ASSP 才能提供的功能,而且還具有靈活性和硬件定制等優(yōu)勢。