0 引言

在設(shè)備更新?lián)Q代時,對現(xiàn)有設(shè)備進(jìn)行合理的升級,不僅能提升設(shè)備的性能,同時還可以延長設(shè)備壽命,降低全壽命周期的費用,同時升級后的設(shè)備在使用維護(hù)上還具有良好的繼承性。

80486處理器雖然已問世十多年,但在各個領(lǐng)域,尤其是機(jī)載航電系統(tǒng)中仍有大量應(yīng)用。目前使用80486處理器的大多數(shù)模塊,普遍存在系統(tǒng)集成度偏低、總線傳輸速率較慢的缺點。針對這一問題,本文結(jié)合某計算機(jī)系統(tǒng)CPU模塊的升級,提出一種解決方案,該方案采用PCI總線提升系統(tǒng)性能,同時將部分功能單元以IP核(InteUectual Property Core)的形式集成到FPGA中,實現(xiàn)了小型化設(shè)計(CPU模塊采用PMC標(biāo)準(zhǔn)板卡外形及安裝方式)。

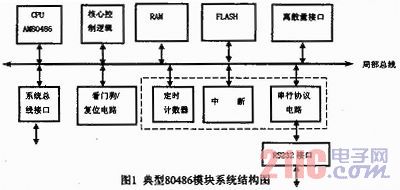

1 典型采用80486處理器的模塊結(jié)構(gòu)

圖1為一種典型的采用80486處理器的模塊(以下簡稱典型80486模塊)結(jié)構(gòu)圖。該模塊采用標(biāo)準(zhǔn)的1/2ATR外形尺寸,系統(tǒng)總線采用LBE(Local Bus Extension)總線,最大傳輸速率約40Mb/s,模塊重量約380g,功耗約5W(5V,1A)。

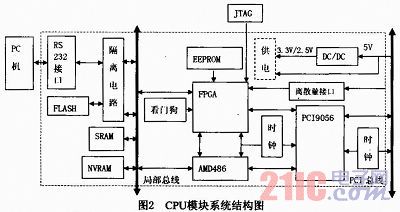

2 小型化80486 CPU模塊設(shè)計

小型化80486CPU模塊(以下簡稱CPU模塊)由處理器、FLASH、SRAM、NVRAM、可編程邏輯、看門狗、時鐘、PCI接口電路、RS232串行接口電路、DC/DC電路和隔離電路組成,系統(tǒng)結(jié)構(gòu)圖如圖2所示。

CPU模塊與典型80486模塊的系統(tǒng)結(jié)構(gòu)差異對比見表1。

2.1 硬件設(shè)計

2.1.1 處理器及存儲器電路

CPU模塊的處理器及存儲器配置如下;a.處理器采用AMD公司的AM80486DX2處理器,外部輸入時鐘33MHz,內(nèi)部工作頻率66MHz,芯片工作在保護(hù)模式下,最大尋址空間為4GB;b.FLASH 4MB,SRAM 1MB,NVRAM 32KB。

2.1.2 外圍工作電路

外圍工作電路主要包括復(fù)位及看門狗電路、離散量接口電路、RS232接口電路和DC/DC電路,具體配置如下:a.復(fù)位及看門狗電路,采用MAX706芯片實現(xiàn),看門狗周期1s;b.離散量接口電路,3路輸入TTL離散量;c.RS232接口電路,采用MAX232AESE芯片實現(xiàn)2路RS232接口;d.DC/DC電路,采用2個LT1085芯片實現(xiàn)5V/2.5V和5W3.3V的電源轉(zhuǎn)換。

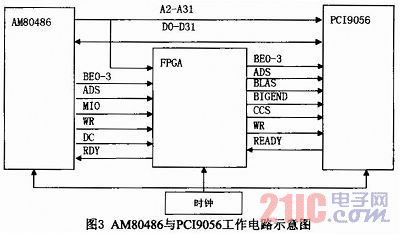

2.1.3 PCI接口電路

CPU模塊的系統(tǒng)總線采用PCI總線,PCI總線寬度為32位(地址/數(shù)據(jù)復(fù)用),總線工作時鐘33MHz,最大傳輸速度可達(dá)132Mb/s。CPU模塊采用PCI9056芯片作為PCI總線接口,主從選擇為Host方式,工作模式為C模式。由于AM80486處理器應(yīng)用年代較早,無法直接與PCI接口芯片連接,因此CPU模塊采用可編程邏輯連接AM80486局部總線和PCI9056。

AM80486與PCI9056的交聯(lián)如圖3所示。AM80486的地址和數(shù)據(jù)可直接與PCI9056相連。針對控制信號,在本系統(tǒng)中,CPU模塊是PCI總線上唯一的主設(shè)備,在訪問PCI總線時,需對圖3中的控制信號進(jìn)行邏輯綜合。

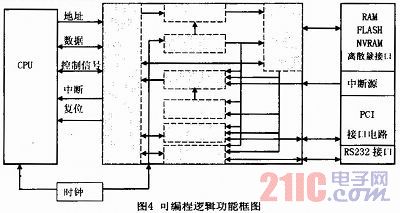

2.1.4 可編程邏輯電路

可編程邏輯電路是系統(tǒng)控制器設(shè)計中的重點。由于模塊的小型化要求,CPU模塊在設(shè)計可編程邏輯時將部分功能單元以IP核的形式集成到FPGA中,以提高系統(tǒng)集成度。

CPU模塊的可編程邏輯采用采用一片XCV300芯片來實現(xiàn),除了地址譯碼、邏輯控制、時序控制、總線超時以及PCI控制邏輯等功能外,還使用IP核完成中斷控制器、定時/計數(shù)器和串行協(xié)議轉(zhuǎn)換功能。可編程邏輯電路的功能示意圖如圖4。

2.1.4.1 中斷控制器

可編程邏輯采用IP核實現(xiàn)一個具有1路非屏蔽中斷和16路可屏蔽中斷的中斷控制器功能。中斷的觸發(fā)方式(電平觸發(fā)/沿觸發(fā))和16路可屏蔽中斷的優(yōu)先級軟件可調(diào)。系統(tǒng)控制器在實現(xiàn)時使用了1路非屏蔽中斷和11路可屏蔽中斷,剩余資源可根據(jù)用戶需求使用。

2.1.4.2 定時/計數(shù)器

可編程邏輯采用IP核實現(xiàn)一個3路獨立的8位定時/計數(shù)器功能,其工作模式與MD8254的MODE2方式相同,每路定時器的輸出使能和計數(shù)頻率軟件可調(diào)。系統(tǒng)控制器在實現(xiàn)時使用了兩路定時器供操作系統(tǒng)使用,剩余的1路留可根據(jù)用戶需求使用。

2.1.4.3 串行協(xié)議控制

可編程邏輯采用IP核實現(xiàn)2路RS232串行協(xié)議控制,用戶可以通過軟件對串行接口的工作方式(查詢/中斷)、串行數(shù)據(jù)的格式(數(shù)據(jù)位/起始位/停止位/奇偶校驗等)和串行通信速率(9600-119200bps可調(diào),默認(rèn)38400bps)等參數(shù)進(jìn)行設(shè)置。

2.2 軟件設(shè)計

CPU模塊使用VxWorks5.5操作系統(tǒng),軟件開發(fā)環(huán)境為Tornado 2.2。VxWorks操作系統(tǒng)具有實時性、可靠性、可剪裁性、支持眾多的目標(biāo)機(jī)、系統(tǒng)的開放性、豐富的環(huán)境工具和第三方支持等特點。VxWorks操作系統(tǒng)功能結(jié)構(gòu)如圖5所示。

CPU膜塊的軟件包括以下內(nèi)容:a.FLASH編程工具;b.BIT測試程序;c.Vxworks操作系統(tǒng):d.驅(qū)動程序;e.應(yīng)用程序。

3 結(jié)束語

小型化的CPU模塊,已成功應(yīng)用在升級后的系統(tǒng)中,取得了良好的成效。除了總線傳輸速度提高(PCI總線最大傳輸速度可達(dá)132Mb/s)、使系統(tǒng)性能得到提升外,還具有以下特點:

(1)安裝方式靈活,節(jié)約系統(tǒng)資源。CPU模塊采用PMC板卡形式,占用空間小(面積下降33%),可以方便地安裝在其它模塊上,同時與典型的80486模塊相比,重量下降70%、功耗下降15%,節(jié)約了系統(tǒng)資源。

(2)配置靈活,升級潛力大。CPU模塊在本設(shè)計中作為PCI總線控制器(Host)使用,但是只要更改PCI9056的配置,并且對可編程邏輯做相應(yīng)更改,即可作為PCI總線的主設(shè)備(Master)和從設(shè)備(Slave)使用。由于采用了SoPC技術(shù)進(jìn)行可編程邏輯設(shè)計,CPU模塊上還有可利用的空間進(jìn)行功能擴(kuò)展(例如增加I2C電路和網(wǎng)絡(luò)接口),同時只要提高處理器和PCI接口的工作頻率,即可進(jìn)一步提高CPU模塊的性能。

(3)通用性強(qiáng),應(yīng)用前景廣泛。由于采用了標(biāo)準(zhǔn)的PCI接口和PMC外形,CPU模塊可以方便地配置在一個PCI總線系統(tǒng)中,并且具有可靈活配置的工作方式(Host/Master/Slave)。同時為現(xiàn)有采用80486處理器計算機(jī)系統(tǒng)的升級,提供了可借鑒的模型,具有廣泛的應(yīng)用前景。