引言

近年來(lái)可編程器件的應(yīng)用日益廣泛,使用較多的是現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)和復(fù)雜可編程邏輯器件(CPLD)。FPGA器件性能優(yōu)越,使用方便,成本低廉,投資風(fēng)險(xiǎn)小,使用FPGA設(shè)計(jì)可以完全根據(jù)設(shè)計(jì)者需要開(kāi)發(fā)ASIC芯片,可方便地反復(fù)編寫(xiě)和修改程序,即使制成PCB后仍能進(jìn)行功能修改。本文將著重介紹運(yùn)用FPGA技術(shù)實(shí)現(xiàn)基群與二次群之間復(fù)接與分接系統(tǒng)的總體設(shè)計(jì)方案。

數(shù)字復(fù)接基本原理及系統(tǒng)構(gòu)成

二次群幀結(jié)構(gòu)及其復(fù)接子幀結(jié)構(gòu)按ITU-TG.742協(xié)議,工作在8448kbit/s的采用正碼速調(diào)整的二次群復(fù)接設(shè)備幀結(jié)構(gòu)如圖1所示,一幀共有848bit,前12位幀碼組包括幀同步碼10位,碼型為1111010000;失步對(duì)告碼,同步為“0”,失步為“1”;國(guó)內(nèi)通信備用碼。Cj1、Cj2、Cj3(j=1,2,3,4)為插入標(biāo)志碼,Vj(j=1,2,3,4)為碼速調(diào)整插入比特,其作用是調(diào)整基群碼速。二次群由四支路的子幀構(gòu)成,子幀結(jié)構(gòu)如圖2所示,一子幀有212bit,1、2、3位碼為幀碼組,記Fj;插入標(biāo)志碼用Cj表示;碼速調(diào)整插入比特用Vj表示。

復(fù)接系統(tǒng)構(gòu)成

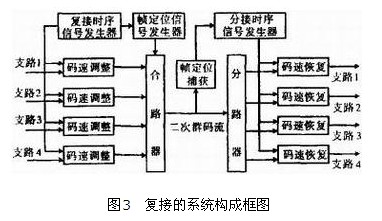

復(fù)接系統(tǒng)構(gòu)成的框圖如圖3。復(fù)接時(shí)序信號(hào)發(fā)生器產(chǎn)生碼速調(diào)整需要的時(shí)序信號(hào),四路基群信號(hào)先各自經(jīng)正碼速調(diào)整,變?yōu)?.112Mbit/s的同步碼流。合路器順序循環(huán)讀取四路碼流,并在每幀開(kāi)頭插入幀定位信號(hào),輸出8.448Mbit/s的標(biāo)準(zhǔn)二次群。

在接收端,合路碼流先進(jìn)行幀定位捕獲,判定系統(tǒng)處于同步態(tài)、失步態(tài)還是過(guò)渡態(tài)。一旦捕獲到幀定位信號(hào),便驅(qū)動(dòng)分接時(shí)序信號(hào)發(fā)生器工作,產(chǎn)生分路和碼速恢復(fù)需要的時(shí)序信號(hào),同時(shí)分路器工作,把幀定位信號(hào)拋掉,順序循環(huán)分別送入4個(gè)碼速恢復(fù)單元,扣除插入碼元,恢復(fù)成四路2.048Mbit/s的基群信號(hào)。

數(shù)字復(fù)接系統(tǒng)的FPGA設(shè)計(jì)

本次FPGA設(shè)計(jì)采用分層設(shè)計(jì),頂層為整個(gè)系統(tǒng)的原理框圖(見(jiàn)圖3),用一些符號(hào)表示功能塊,然后把每個(gè)功能塊分成若干子模塊,各模塊獨(dú)立設(shè)計(jì)。下面就各模塊的設(shè)計(jì)思想進(jìn)行詳細(xì)介紹。

復(fù)接電路設(shè)計(jì)

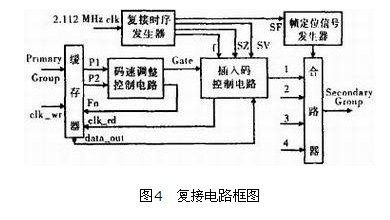

復(fù)接電路如圖4所示,它由復(fù)接時(shí)序發(fā)生器、緩存器、碼速調(diào)整控制電路、插入碼控制電路、幀定位信號(hào)發(fā)生器和合路器6個(gè)模塊構(gòu)成。圖中只畫(huà)了第一條支路參與復(fù)接的實(shí)現(xiàn)過(guò)程,因?yàn)樗臈l支路的過(guò)程完全相同,因而略去其余3個(gè)支路的電路。

(1)復(fù)接時(shí)序發(fā)生器模塊

輸入為2.112MHz頻率的均勻時(shí)鐘,通過(guò)該模塊產(chǎn)生插入碼控制電路所需的插入標(biāo)志時(shí)隙脈沖SZ、調(diào)整插入時(shí)隙脈沖SV、頻率為2.112MHz的非均勻時(shí)鐘f(從輸入的均勻時(shí)鐘扣除了時(shí)隙SZ和SF)和幀定位信號(hào)發(fā)生器所需的時(shí)隙脈沖SF。

(2)緩存器模塊

基群信號(hào)以2.048MHz的均勻時(shí)鐘clk_wr寫(xiě)入緩存器,同時(shí)以2.112MHz的非均勻時(shí)鐘clk_rd讀出,clk_rd由插入碼控制電路產(chǎn)生。該模塊還需輸出每次寫(xiě)入和讀出一幀數(shù)據(jù)時(shí)第一個(gè)clk_wr脈沖P1和clk_rd脈沖P2,送給碼速調(diào)整控制電路模塊。在該模塊的設(shè)計(jì)中,應(yīng)注意每一幀信息碼的位數(shù)不是固定的,必須通過(guò)碼速調(diào)整控制電路模塊的反饋信號(hào)Fn來(lái)確定,當(dāng)反饋信號(hào)表明本幀需要調(diào)整,則位數(shù)為205;反之,位數(shù)為206。

(3)碼速調(diào)整控制電路模塊

緩存器的寫(xiě)入脈沖超前于讀出脈沖的時(shí)間量稱(chēng)為讀寫(xiě)時(shí)差,讀寫(xiě)時(shí)差的大小總隨時(shí)間不斷變化著。該電路中緩存器的寫(xiě)入速率低于讀出速率,隨著時(shí)間的推移,緩存器中所存信息碼數(shù)目越來(lái)越少,最后導(dǎo)致“取空”而造成錯(cuò)誤的數(shù)據(jù)傳輸。因此,我們必須設(shè)定一門(mén)限,當(dāng)信碼數(shù)降到門(mén)限值時(shí),就進(jìn)行碼速調(diào)整。

通過(guò)對(duì)各時(shí)刻讀寫(xiě)時(shí)差的聯(lián)系以及趨向最終狀態(tài)變化的分析得出,讀寫(xiě)時(shí)差的最低點(diǎn)總是發(fā)生在一幀末尾,而在幀首通過(guò)兩脈沖相位差就能判斷本幀是否需要碼速調(diào)整。具體地說(shuō),P1和P2輸入進(jìn)行鑒相判決得到幀首的讀寫(xiě)時(shí)差T0,與調(diào)整門(mén)限值TS進(jìn)行比較,若T0>TS則本幀不需要調(diào)整,反之若T0≤TS,則需要調(diào)整。這時(shí)模塊輸出反饋信號(hào)Fn給緩存器,和調(diào)整控制負(fù)脈沖Gate給輸入碼控制電路模塊。

(4)插入碼控制電路模塊

該模塊的功能是對(duì)緩存器的讀出信息進(jìn)行插入碼控制,輸出2.112MHz的非均勻時(shí)鐘clk_rd和參與合路的支路碼流。為了標(biāo)志是否在時(shí)隙SZ有插入調(diào)整比特,就必須引入插入標(biāo)志碼。通常在一幀中規(guī)定一個(gè)特定時(shí)隙SV,提供一次碼速調(diào)整的機(jī)會(huì)。如果某支路需要進(jìn)行調(diào)整,就在該時(shí)隙插入一比特脈沖,如不需要調(diào)整則該時(shí)隙仍傳支路信息。為確保可靠性,通常采用3位碼作為插入標(biāo)志碼。如果某支路有插入調(diào)整,用標(biāo)志碼為111來(lái)表示,否則用000表示。

(5)幀定位信號(hào)發(fā)生器模塊

該模塊產(chǎn)生幀同步信號(hào)和告警指示碼,幀定位信號(hào)可以集中插入,也可以分散到各支路插入,考慮到設(shè)備和延遲問(wèn)題,我們選擇集中插入。

(6)合路器模塊

根據(jù)每個(gè)時(shí)間間隔傳送碼字的多少,有3種排列方式:按位復(fù)接、按字復(fù)接和按幀復(fù)接。其中按位復(fù)接要求緩存器容量較小,較易實(shí)現(xiàn),而且二次群幀結(jié)構(gòu)是由4個(gè)支路子幀按位復(fù)接而成,所以一般采用按位復(fù)接,本文采用的也是該方式。該模塊按位順序循環(huán)讀取四路碼速調(diào)整后的碼流,在對(duì)應(yīng)SF時(shí)隙插入幀定位信號(hào)“111101000000”,得到二次群信號(hào),即完成整個(gè)復(fù)接部分。

分接電路設(shè)計(jì)

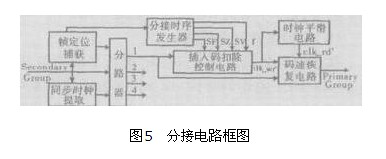

分接過(guò)程如圖5所示,它是由幀定位捕獲電路、同步時(shí)鐘提取電路、分路器、分接時(shí)序信號(hào)發(fā)生器、插入碼扣除控制電路、時(shí)鐘平滑電路和碼速恢復(fù)控制電路7個(gè)模塊構(gòu)成。由于四路分接電路基本相同,所以略去其余三路電路。

(1)幀定位捕獲電路模塊

該模塊通過(guò)捕獲幀定位信號(hào)分辨幀首位置,并判定系統(tǒng)的狀態(tài)。當(dāng)連續(xù)3次捕獲到幀定位信號(hào),則判定系統(tǒng)處于同步態(tài);之后若連續(xù)4次沒(méi)捕獲到幀定位信號(hào),則判定系統(tǒng)進(jìn)入失步態(tài),并關(guān)閉分接時(shí)序信號(hào)發(fā)生器,也不再接收數(shù)據(jù);一旦捕獲到幀定位信號(hào),便驅(qū)動(dòng)分接時(shí)序信號(hào)發(fā)生器工作,并開(kāi)始接收數(shù)據(jù)。這里要求模塊在系統(tǒng)失步后能重新進(jìn)入同步,如果傳輸中幀同步碼組連續(xù)丟失了幾幀,而系統(tǒng)又沒(méi)有自恢復(fù)能力,那么整個(gè)系統(tǒng)將無(wú)法再正常工作。

(2)同步時(shí)鐘提取模塊

數(shù)據(jù)流的接收需要與之速率相同的時(shí)鐘,這就需要對(duì)二次群碼流進(jìn)行位同步時(shí)鐘提取,得到與之速率一致的均勻時(shí)鐘給分路器。

(3)分路器模塊

一旦捕獲到幀定位信號(hào),分接器便開(kāi)始工作,把幀定位信號(hào)拋掉,其余在8.448MHz的位同步時(shí)鐘下按位順序循環(huán)進(jìn)行同步分離,分別送入4個(gè)碼速恢復(fù)單元。

(4)分接時(shí)序信號(hào)發(fā)生器模塊

該模塊設(shè)計(jì)思想基本同于復(fù)接時(shí)序信號(hào)發(fā)生器,其基準(zhǔn)時(shí)鐘由位同步時(shí)鐘分頻得到。幀定位捕獲電路驅(qū)動(dòng)它工作,產(chǎn)生幀定位時(shí)隙脈沖SF,插入標(biāo)志時(shí)隙脈沖SZ,調(diào)整插入時(shí)隙脈沖SV和2.112MHz的非均勻時(shí)鐘f,送給插入碼扣除控制電路。

(5)插入碼扣除控制電路模塊

該模塊的功能是扣除復(fù)接時(shí)插入碼流的碼字,輸出作為碼速恢復(fù)電路的寫(xiě)入時(shí)鐘clk_wr’,在接收端對(duì)收到的SZ時(shí)隙的標(biāo)志碼進(jìn)行擇多判決,即標(biāo)志碼中有2個(gè)以上為1,判為有插入調(diào)整,分接時(shí)應(yīng)將SV時(shí)隙內(nèi)容扣除;否則判為無(wú)插入調(diào)整,分接時(shí)無(wú)需扣除SV時(shí)隙內(nèi)容。如果輸入碼流對(duì)應(yīng)SZ時(shí)隙出現(xiàn)“1”的個(gè)數(shù)比“0”的個(gè)數(shù)多,f中對(duì)應(yīng)SV的一個(gè)節(jié)拍被扣除;如果對(duì)應(yīng)SZ時(shí)隙“0”的個(gè)數(shù)比“1”的個(gè)數(shù)多,則f中對(duì)應(yīng)SV的節(jié)拍仍起作用。

(6)時(shí)鐘平滑電路模塊

該模塊對(duì)非均勻時(shí)鐘clk_wr’進(jìn)行平滑均勻,提取2.048MHz的均勻時(shí)鐘clk_rd’作為碼速恢復(fù)電路的讀出時(shí)鐘。這里可用VHDL語(yǔ)言來(lái)實(shí)現(xiàn),也可以用一般的二階鎖相環(huán)。

(7)碼速恢復(fù)電路模塊

從分路器輸出的支路碼流以2.112MHz的非均勻時(shí)鐘clk_wr’寫(xiě)入該模塊,同時(shí)以2.048MHz的均勻時(shí)鐘clk_rd’讀出,即還原出基群信號(hào),完成整個(gè)分接過(guò)程。

結(jié)束語(yǔ)

系統(tǒng)仿真波形良好,除了允許范圍內(nèi)的信號(hào)延遲外,能準(zhǔn)確實(shí)現(xiàn)數(shù)字信號(hào)的復(fù)接和分接。誤碼率小于0.1%,系統(tǒng)信號(hào)平均時(shí)延小于4.5μs,去抖效果良好。而且本設(shè)計(jì)便于擴(kuò)展,只需修改FPGA中相應(yīng)控制參數(shù),就可以實(shí)現(xiàn)高次群的復(fù)接與分接。該系統(tǒng)作為IP核應(yīng)用于信號(hào)傳輸電路,對(duì)數(shù)字信號(hào),或經(jīng)PCM編碼調(diào)制后的語(yǔ)音信號(hào)進(jìn)行處理,可提高信道的利用率和傳輸質(zhì)量,也可以進(jìn)行光電轉(zhuǎn)換后用于光纖通信或大氣激光通信中。