TMS320VC5402(VC5402)是德州儀器公司推出的具有較高性價(jià)比的定點(diǎn)數(shù)字信號(hào)處理器。VC5402增強(qiáng)外設(shè)由軟件等待狀態(tài)發(fā)生器、鎖相環(huán)時(shí)鐘發(fā)生器、6通道直接存儲(chǔ)器訪問(DMA)控制器、增強(qiáng)型8位并行主機(jī)接口(HPI)等組成。兩個(gè)可編程的多通道緩沖串口(McBSP)能夠全雙工、快速地與其他同步串口進(jìn)行數(shù)據(jù)交換,硬件連接簡(jiǎn)單,串口的工作模式和傳送數(shù)據(jù)的格式可通過(guò)編程實(shí)現(xiàn)。DSP和單片機(jī)之間的通信一般利用雙口RAM,通過(guò)串口或DSP的HPI接口實(shí)現(xiàn)。

利用雙口RAM實(shí)現(xiàn)

CY7C026是CYPRESS公司生產(chǎn)的16k×16B高速雙口靜態(tài)RAM,存取速度小于25ns。他具有真正的雙端口,可以同時(shí)進(jìn)行數(shù)據(jù)存取,兩個(gè)端口具有獨(dú)立的控制信號(hào)線、地址線和數(shù)據(jù)線,另外通過(guò)主?從選擇可以方便地?cái)U(kuò)存儲(chǔ)容量和數(shù)據(jù)寬度。通過(guò)芯片的信號(hào)量標(biāo)志器,左、右兩端口可以實(shí)現(xiàn)芯片資源的共享。

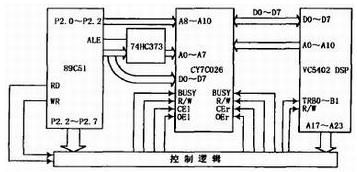

由于DSP的數(shù)據(jù)是16位,而單片機(jī)的數(shù)據(jù)是8位,所以TMS320VC5402與雙口RAM的接口并無(wú)特別之處,但是89C51與雙口RAM之間的接口電路中就需要對(duì)89C51進(jìn)行總線擴(kuò)展了。具體做法是利用鎖存器74HC373的鎖存功能,通過(guò)對(duì)其使能信號(hào)的控制,進(jìn)行分時(shí)讀寫,實(shí)現(xiàn)數(shù)據(jù)總線的擴(kuò)展,即利用鎖存器作為虛擬總線。DSP,單片機(jī)與雙口RAM之間的接口電路如圖1所示。

圖1 通過(guò)雙口RAM實(shí)現(xiàn)的接口電路

雙口RAM必須采用一定的機(jī)制來(lái)協(xié)調(diào)左右兩邊CPU對(duì)他的讀寫操作,否則會(huì)出現(xiàn)讀寫數(shù)據(jù)的錯(cuò)誤。通常可以用中斷、硬件、令牌和軟件這4種方式來(lái)協(xié)調(diào)雙方。在接口電路中利用89C51的最低地址位A0把雙口RAM的存儲(chǔ)空間分為奇、偶地址兩個(gè)空間。其中,奇地址空間專供89C51寫,偶地址空間專供89C51讀。那么只需對(duì)VC5402的軟件做相應(yīng)處理即可,即VC5402對(duì)雙口RAM的奇地址空間只讀,對(duì)偶地址空間只寫。這樣就避免了DSP和單片機(jī)對(duì)雙口RAM同一地址單元的寫入操作。另外,在對(duì)雙口RAM進(jìn)行訪問之前,單片機(jī)和DSP首先對(duì)本端的BUSY信號(hào)進(jìn)行查詢,只有本端/BUSY信號(hào)無(wú)效時(shí)才進(jìn)行讀寫操作,進(jìn)一步保證了數(shù)據(jù)讀寫的可靠性。

通過(guò)串口實(shí)現(xiàn)

VC5402多通道緩沖串行口(McBSP)主要特點(diǎn):雙緩沖區(qū)發(fā)送,三緩沖區(qū)接收以便數(shù)據(jù)的連續(xù)性;接收與發(fā)送的幀同步、時(shí)鐘信號(hào)獨(dú)立;多通道發(fā)送和接收,最多可以到達(dá)128個(gè)通道;數(shù)據(jù)大小可為8,12,16,20,24和32b;μ率和A率壓縮;幀同步、數(shù)據(jù)時(shí)鐘極性可編程;內(nèi)部時(shí)鐘和幀同步可自行設(shè)定。

VC5402串口通過(guò)16b寬度的控制寄存器與內(nèi)部總線通信。

數(shù)據(jù)接收過(guò)程:數(shù)據(jù)從輸入引腳(DR)移位到接收移位寄存器(RSR),然后拷貝數(shù)據(jù)到接收緩沖寄存器(RBR),接著把數(shù)據(jù)拷貝到數(shù)據(jù)接收寄存器(DRR),CPU或者DMA控制器讀取DRR。

數(shù)據(jù)輸出過(guò)程:CPU或者DMA把數(shù)據(jù)寫到數(shù)據(jù)傳輸寄存器(DXR),再通過(guò)寄存器(XSR)移位到數(shù)據(jù)輸出引腳DX6。

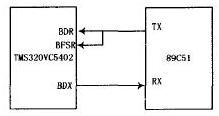

對(duì)串口寄存器的訪問是間接尋址方式,例如要對(duì)McBSP數(shù)據(jù)寄存器進(jìn)行訪問,首先寫串口控制寄存器SPCR子地址到子地址寄存器SPSA,然后對(duì)數(shù)據(jù)寄存器進(jìn)行訪問。硬件連接如圖2所示。

圖2 通過(guò)McBSP實(shí)現(xiàn)的硬件連接

McBSP的位時(shí)鐘由內(nèi)部采樣率發(fā)生器產(chǎn)生,為UART波特率×16。

在軟件的設(shè)計(jì)中McBSP的16位代表UART的1位。發(fā)送時(shí),軟件將UART的每一位擴(kuò)展為16位,再由McBSP發(fā)送。接收時(shí),軟件將McBSP接收的16位壓縮為UART的1位,并進(jìn)行合并。軟件還應(yīng)負(fù)責(zé)處理UART的起始位、奇偶校驗(yàn)位和停止位。

通過(guò)HPI和電平轉(zhuǎn)換器件實(shí)現(xiàn)

DSP芯片中的HPI(主機(jī)接口)是為了滿足DSP與其他的微處理器接口而專門設(shè)計(jì)的。他分為HPI—8和HPI1—6,分別針對(duì)具有8位和16位數(shù)據(jù)線的單片機(jī)。每一種又分為標(biāo)準(zhǔn)型和增強(qiáng)型,區(qū)別在于標(biāo)準(zhǔn)型只可以訪問固定的地址空間,而增強(qiáng)型可以訪問整個(gè)DSP的片內(nèi)存儲(chǔ)器。利用C5402的增強(qiáng)型8位并行主機(jī)接口(HPI)與單片機(jī)通信。

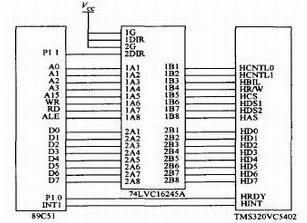

VC5402DSP的外部I/P引腳用的是3.3V的邏輯電平,而大部分51單片機(jī)用的是5V的邏輯電平。前者輸出高電平,最小值為2.4V;后者輸入高電平,最小值為2.0V。所以前者的輸出可以直接接到后者的輸入。但是前者允許輸入高電平最大值為3.6V,而后者的輸出高電平一般都在4.6V以上。所以前者的輸入和后者的輸出不能直接連接,需要做電平轉(zhuǎn)換。如果引腳數(shù)量少,可以直接用三極管電阻來(lái)轉(zhuǎn)換。這里由于引腳較多,所以選用TI74LVC16245A芯片來(lái)進(jìn)行電平轉(zhuǎn)換。硬件電路如圖3所示。

圖3 通過(guò)電平轉(zhuǎn)換芯片實(shí)現(xiàn)

HPI的數(shù)據(jù)傳輸分為2部分:外部傳輸和內(nèi)部傳輸。外部傳輸是指主機(jī)和HPI寄存器之間的傳輸,由主機(jī)發(fā)出指令完成。內(nèi)部傳輸是指HPI寄存器和DSP內(nèi)部RAM之間的傳輸,由DSP內(nèi)部的DMA控制器自動(dòng)完成。主機(jī)在進(jìn)行外部傳輸時(shí),要先檢查內(nèi)部傳輸是否完成,這是通過(guò)檢測(cè)HRDY信號(hào)實(shí)現(xiàn)的。外部傳輸操作的一般步驟是:檢查HRDY信號(hào)的電平。為高,表示可以進(jìn)行傳輸;為低,表示DSP正在進(jìn)行內(nèi)部傳輸,此時(shí)不能進(jìn)行外部傳輸。主機(jī)發(fā)出指令,設(shè)置HCNTL0,HCNTL1,BHIL,HR?W信號(hào)的狀態(tài),以確定讀或?qū)懙募拇嫫饕约白止?jié)的選擇。主機(jī)發(fā)出時(shí)序控制信號(hào),按時(shí)序進(jìn)行操作,從而完成一次外部傳輸。

結(jié)語(yǔ)

雙口RAM實(shí)現(xiàn)VC5402和89C51之間的數(shù)據(jù)通信,極大地提高了數(shù)據(jù)傳輸速度和可靠性,能滿足控制系統(tǒng)的實(shí)時(shí)、高速的控制要求。

利用McBSP的方法,硬件結(jié)構(gòu)簡(jiǎn)單所用芯片少,但是將占用片上系統(tǒng)中為數(shù)不多的同步串行口資源,而且也要占用DSP的處理時(shí)間,他是用于傳輸數(shù)據(jù)較少,傳輸速率慢而又希望DSP與單片機(jī)之間是緊耦合的場(chǎng)合。

HPI方案比較簡(jiǎn)單,附加硬件少、成本低、數(shù)據(jù)吞吐量非常大,但不適合于實(shí)時(shí)控制的場(chǎng)合,因?yàn)楣ぷ髦锌赡軐SP掛起,影響實(shí)時(shí)工作。而一般應(yīng)用在對(duì)成本比較敏感而數(shù)據(jù)量又比較大的場(chǎng)合。讀者可以根據(jù)系統(tǒng)要求選取合適的方案。