摘要:針對(duì)跳頻通信系統(tǒng)有固有噪聲的特點(diǎn),結(jié)合DDS+DPLL高分辨率、高頻率捷變速度的優(yōu)點(diǎn),并采用Altera公司的Quartus-Ⅱ_10.1軟件進(jìn)行設(shè)計(jì)綜合,提出了一種新型的跳頻信號(hào)源。結(jié)果表明,該設(shè)計(jì)中DPLL時(shí)鐘可達(dá)到120 MHz,性能較高,而僅使用了30個(gè)LUT和18個(gè)觸發(fā)器,占用資源很少。

關(guān)鍵詞:數(shù)字鑒相器;濾波器;數(shù)控振蕩器;DPLL

0 引言

軍事通信中,常采用跳頻技術(shù)來(lái)實(shí)現(xiàn)通信信息的保密和抗干擾,尤其是應(yīng)用在通信系統(tǒng)中抗跟蹤式干擾方面,它是電子對(duì)抗中非常重要的一個(gè)研究課題。

最初的頻率綜合器全由模擬電路實(shí)現(xiàn),由于模擬電路存在溫度漂移、電網(wǎng)電壓等缺點(diǎn),給系統(tǒng)的同步帶來(lái)困難。隨著大規(guī)模、超大規(guī)模數(shù)字集成電路的發(fā)展,在部分應(yīng)用領(lǐng)域,數(shù)字頻率綜合器逐漸取代了模擬頻率綜合器。近年來(lái)隨著FPGA和CPLD技術(shù)的迅猛發(fā)展,數(shù)字頻率綜合器的實(shí)現(xiàn)方式和工作速度都到了本質(zhì)的改進(jìn)和提高,可以說(shuō)數(shù)字頻率綜合器是隨著FPGA的發(fā)展而發(fā)展起來(lái)的。

1 各個(gè)功能模塊的組成原理與實(shí)現(xiàn)

1.1 數(shù)字鑒相器

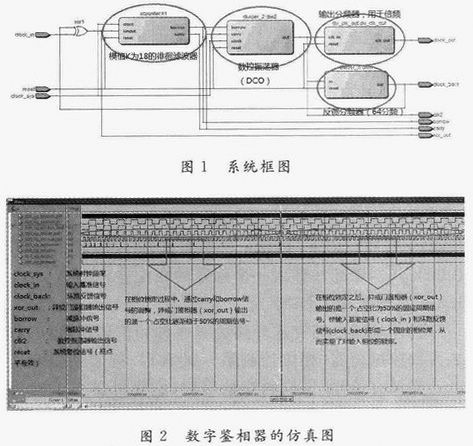

在數(shù)字鑒相器(異或門(mén)鑒相器)中,首先將輸入信號(hào)與本地估算信號(hào)進(jìn)行比較(其中,輸入clock_in基準(zhǔn)頻率與clk2反饋回來(lái)的頻率相同,只存在相位差),從而得到一個(gè)表明相位誤差的脈沖輸出,實(shí)際上就是一個(gè)異或門(mén)。系統(tǒng)框圖如圖1所示,仿真結(jié)果如圖2所示。

![]()

從仿真波形中可以看出:當(dāng)系統(tǒng)對(duì)頻率進(jìn)行鎖定的過(guò)程中,使可變模計(jì)數(shù)器產(chǎn)生增脈沖(carry)和減脈沖(borrow)信號(hào),鑒相器輸出(xor _out)的是一個(gè)逐漸趨于占空比為50%的方波,從而使輸入基準(zhǔn)頻率與反饋頻率鎖定在一個(gè)固定的相位上。

1.2 徘徊濾波器

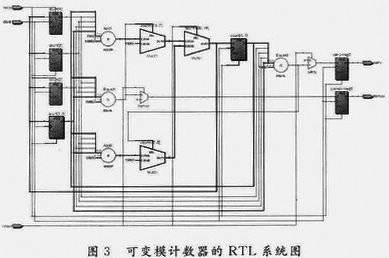

徘徊濾波器的作用是平滑鑒相器帶來(lái)的相位抖動(dòng),選用雙向計(jì)數(shù)器來(lái)實(shí)現(xiàn)該功能,其RTL系統(tǒng)構(gòu)架如圖3所示。在PLL工作過(guò)程中,環(huán)路鎖定時(shí),異或門(mén)鑒相器的輸出XOR_OUT是一個(gè)占空比為50%的方波。因?yàn)樵贒PLL的基本結(jié)構(gòu)中,K變模可逆計(jì)數(shù)器始終起作用。因此當(dāng)環(huán)路鎖定后,如果模數(shù)K取值較小,K變模可逆計(jì)數(shù)器會(huì)頻繁地周期性輸出進(jìn)位脈沖信號(hào)CARRY和借位脈沖信號(hào)BORROW,從而在脈沖加減電路中產(chǎn)生周期性的脈沖加入和扣除動(dòng)作,這樣就在脈沖加減電路的輸出信號(hào)XOR_OUT中產(chǎn)生了周期性的誤差,稱(chēng)為“紋波”;如果模數(shù)K取值足夠大(對(duì)于異或門(mén)鑒相器,K應(yīng)大于M/4),則這種“紋波”誤差通過(guò)除N計(jì)數(shù)器后,可以減少到N個(gè)周期出現(xiàn)一次。也就是說(shuō)K變模可逆計(jì)數(shù)器的進(jìn)位脈沖信號(hào)CARRY和借位脈沖信號(hào)BORROW的周期是N個(gè)參考時(shí)鐘周期。只有當(dāng)本地枯算信號(hào)與輸入信號(hào)的相位誤差在同一極性持續(xù)增加時(shí),計(jì)數(shù)器會(huì)朝一個(gè)方向計(jì)數(shù),直到有進(jìn)位或借位脈沖輸出。該脈沖即是數(shù)控振蕩器的控制信號(hào),用以控制數(shù)控振蕩器輸出的本地估算脈沖的頻率與相位。由此可見(jiàn),由于徘徊濾波器的作用,使得鎖相環(huán)只有在本地估算信號(hào)與輸入數(shù)字的相位有一定的誤差時(shí),才進(jìn)行調(diào)整,以達(dá)到平滑噪聲干擾帶來(lái)的相位抖動(dòng)的目的。

![]()

若系統(tǒng)失鎖,如圖4所示,則異或門(mén)鑒相器(xor_out)輸出的不是一個(gè)占空比固定的周期信號(hào)。從而使反饋的信號(hào)(clock_back)無(wú)法跟蹤輸入的基準(zhǔn)信號(hào)(clock_in),即無(wú)法形成一個(gè)固定的相位差。

1.3 數(shù)控振蕩器DCO

脈沖加減電路完成環(huán)路的頻率和相位調(diào)整,可以稱(chēng)之為數(shù)控振蕩器(相位控制器),其RTL構(gòu)架如圖5所示。當(dāng)沒(méi)有進(jìn)位/借位脈沖信號(hào)時(shí),它把外部參考時(shí)鐘進(jìn)行2分頻;當(dāng)有進(jìn)位脈沖信號(hào)CARRY時(shí),則在輸出的2分頻信號(hào)中插入半個(gè)脈沖,以提高輸出信號(hào)的頻率;當(dāng)有借位脈沖信號(hào)BORROW時(shí),則在輸出的2分頻信號(hào)中減去半個(gè)脈沖,以降低輸出信號(hào)的頻率。這樣就達(dá)到了調(diào)整本地時(shí)鐘的相位,并使其跟蹤鎖定在輸入信號(hào)相位上的目的。

當(dāng)carry=0和borrow=O時(shí),輸出為系統(tǒng)時(shí)鐘的2分頻(clk2為輸出;clock_sys位系統(tǒng)時(shí)鐘),如圖6所示。

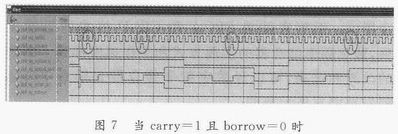

當(dāng)carry=1且borrow=0時(shí),輸出為在系統(tǒng)2分頻的基礎(chǔ)上加上一個(gè)系統(tǒng)周期(clk2為輸出;clock_sys位系統(tǒng)時(shí)鐘),如圖7所示。

1.4 N分頻器

分頻數(shù)N為鎖相環(huán)的一個(gè)重要參數(shù),它與鎖相環(huán)的最大相位誤差θ及同步建立時(shí)間t滿(mǎn)足如下關(guān)系:

θ=2π/N,t=TN

式中:T為輸入信號(hào)的周期。

可見(jiàn),為了取得較小的相位誤差,N的取值變大,相對(duì)的鎖相環(huán)的建立時(shí)間也就變長(zhǎng)。所以對(duì)于這兩個(gè)指標(biāo)而言,N的取值是矛盾的,為了達(dá)到較好鎖相效果,需對(duì)N取一個(gè)中間值。在該設(shè)計(jì)中N取值為32,由仿真圖可知,此時(shí)同步建立時(shí)間大概為18 μs,而相位誤差為π/16。另外,徘徊濾波器中,雙向計(jì)數(shù)器的計(jì)數(shù)峰值Q也對(duì)同步建立時(shí)間有直接影響。當(dāng)計(jì)數(shù)頻率和相差不變時(shí),Q越大,則計(jì)數(shù)器達(dá)到滿(mǎn)值所需時(shí)間越長(zhǎng),同步建立時(shí)間也就越長(zhǎng);反之亦然。可見(jiàn)Q與建立時(shí)間t成反比,在該設(shè)計(jì)中Q取18。

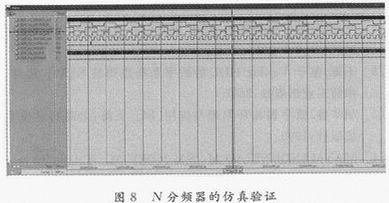

clk2,carry,borrow,oxr_out為測(cè)試端口;dIv_elk_out為分頻值小于divider_n的一個(gè)分頻器;從而輸出一個(gè)高于基準(zhǔn)輸入頻率的信號(hào),并對(duì)輸入的基準(zhǔn)頻率進(jìn)行倍頻,如圖8所示。

2 DPLL的FPGA實(shí)現(xiàn)

下面給出詳細(xì)描述DPLL的工作過(guò)程:

(1)當(dāng)環(huán)路失鎖時(shí),異或門(mén)鑒相器比較輸入信號(hào)(clock_in)和反饋信號(hào)(clock_back)之間的相位差異,產(chǎn)生K變模可逆計(jì)數(shù)器的計(jì)數(shù)方向控制信號(hào)(xor_out)。

(2)K變模可逆計(jì)數(shù)器根據(jù)計(jì)數(shù)方向控制信號(hào)(xor_out)調(diào)整計(jì)數(shù)值。xor_out為高進(jìn)行加計(jì)數(shù),并當(dāng)計(jì)數(shù)值到達(dá)預(yù)設(shè)的K值時(shí),輸出進(jìn)位脈沖信號(hào)(carry);為低進(jìn)行加計(jì)數(shù),并當(dāng)計(jì)數(shù)值達(dá)到0時(shí),輸出借位脈沖信號(hào)(borrow)。

(3)脈沖加減電路則根據(jù)進(jìn)位脈沖信號(hào)(carry)和借位脈沖信號(hào)(borrow)在電路輸出信號(hào)(clk2)中進(jìn)行脈沖的增加和扣除操作,來(lái)調(diào)整clk2信號(hào)的頻率,以實(shí)現(xiàn)clock_back信號(hào)對(duì)clock_in信號(hào)的相位跟蹤。

(4)重復(fù)上面的調(diào)整過(guò)程,當(dāng)環(huán)路進(jìn)入鎖定狀態(tài)時(shí),異或門(mén)鑒相器的輸出xor_out為一占空比50%的方波,而K變模可逆計(jì)數(shù)器則周期性地產(chǎn)生進(jìn)位脈沖輸出CARRY和借位脈沖輸出BORROW,導(dǎo)致脈沖加減電路的輸出IDOUT周期性地加入和扣除半個(gè)脈沖。

失鎖狀態(tài)如圖9所示。當(dāng)輸入的基準(zhǔn)頻偏離PLL系統(tǒng)的中心頻率合適時(shí),系統(tǒng)將實(shí)現(xiàn)相位的鎖定,如圖10所示,且鎖定之后可形成固定的相位差。

利用ALTERA自帶的SignalTapⅡ進(jìn)行在線(xiàn)調(diào)試如圖11所示,調(diào)試后照片如圖12所示。其中參數(shù)為:PLL系統(tǒng)的環(huán)路中心頻率為24 414 Hz;單片機(jī)產(chǎn)生輸入鑒相頻率為24 348 Hz;分頻器N值為1 024;可變模計(jì)數(shù)器K值為600;系統(tǒng)輸出頻率為:24 408~24 418Hz(數(shù)碼管顯示)。

在PLL的基礎(chǔ)上加入頻率檢測(cè)模塊,如圖13所示。圖中:Clk_ref_in為輸入鑒相頻率;Clk_sys為系統(tǒng)工作頻率;Reset為系統(tǒng)復(fù)位信號(hào)(低電平有效);Seg[7:0]為數(shù)碼管段選輸出;Dig[7:0]為數(shù)碼管位選輸出;Clock_out為系統(tǒng)輸出信號(hào)(此系統(tǒng)中沒(méi)有實(shí)現(xiàn)倍頻)。

從圖中可以看出:鑒相器輸出了一個(gè)占空比固定的周期信號(hào),并且實(shí)現(xiàn)了較為精確的相位鎖定。

設(shè)計(jì)中反饋分頻器和環(huán)路濾波器是系統(tǒng)能否成功鎖相的關(guān)鍵。輸入的鑒相頻率應(yīng)該盡可能的滿(mǎn)足:

clk_in=clk_sys/(2N)

式中:N為系統(tǒng)反饋環(huán)路的分頻值。環(huán)路濾波器和可變模計(jì)數(shù)器應(yīng)該滿(mǎn)足關(guān)系式:

K>N/4

即濾波寬度至少大于相位鎖定之后異或門(mén)輸出近似50%方波的高電平寬度,如圖14所示。

3 結(jié)論

本文主要研究了一種基于FPAG、自頂向下、模塊化、用于頻率綜合器的全數(shù)字鎖相環(huán)設(shè)計(jì)方法。應(yīng)用Verilog硬件描述語(yǔ)言使設(shè)計(jì)更加靈活,不僅縮短了設(shè)計(jì)周期,而且可實(shí)現(xiàn)復(fù)雜的數(shù)字電路系統(tǒng)。該設(shè)計(jì)中的一階DPLL使用Quartus-Ⅱ_10.1軟件進(jìn)行設(shè)計(jì)綜合,采用Quartus的Cyclone-Ⅱ系列的EP2C8Q208C8 FPGA器件實(shí)現(xiàn),并使用ModelSim 6.6C軟件進(jìn)行仿真。經(jīng)仿真測(cè)試,該P(yáng)LL具有鎖定相位時(shí)間短,鎖定后相位穩(wěn)定的特點(diǎn),最大偏差不超過(guò)10%,已給出測(cè)試圖片,從而驗(yàn)證了設(shè)計(jì)的正確性。