在數(shù)字通信系統(tǒng)中,同步技術(shù)是非常重要的,而位同步是最基本的同步。位同步時(shí)鐘信號(hào)不僅用于監(jiān)測(cè)輸入碼元信號(hào),確保收發(fā)同步,而且在獲取幀同步及對(duì)接收的數(shù)字碼元進(jìn)行各種處理的過(guò)程中也為系統(tǒng)提供了一個(gè)基準(zhǔn)的同步時(shí)鐘。位同步的目的是使每個(gè)碼元得到最佳的解調(diào)和判決。位同步可以分為外同步法和自同步法兩大類。一般而言,自同步法應(yīng)用較多。外同步法需要另外專門傳輸位同步信息。

自同步法則是從信號(hào)碼元中提取其包含的位同步信息。自同步法又可以分為兩種,即開(kāi)環(huán)同步法和閉環(huán)同步法。開(kāi)環(huán)法采用對(duì)輸入碼元做某種變換的方法提取位同步信息。閉環(huán)法則用比較本地時(shí)鐘和輸入信號(hào)的方法,將本地時(shí)鐘鎖定在輸入信號(hào)上。閉環(huán)法更為準(zhǔn)確,但是也更為復(fù)雜。

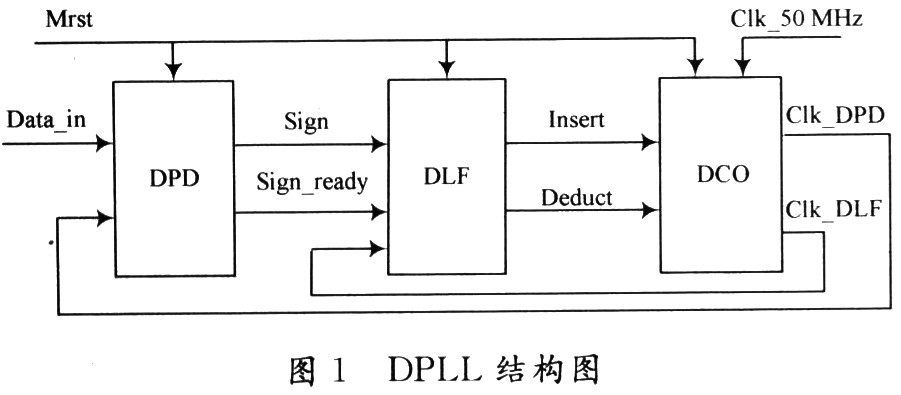

本文采用了自同步法,在FPGA構(gòu)造片內(nèi)對(duì)超前一滯后全數(shù)字鎖相環(huán)提取曼徹斯特碼中包含的位同步時(shí)鐘。1提取位同步時(shí)鐘全數(shù)字鎖相環(huán)總體結(jié)構(gòu)與工作原理這種超前一滯后全數(shù)字鎖相環(huán)采用加減門結(jié)構(gòu),每輸入一個(gè)碼元后,根據(jù)鑒相器判斷是超前還是滯后,通過(guò)反饋回路控制的加減門來(lái)調(diào)整相位,使之逼近輸入碼元的相位。一旦失步,就需要通過(guò)反饋回路重新調(diào)整。每一個(gè)超前和滯后脈沖僅能調(diào)整一步,如果接收碼元出現(xiàn)連“1”或是連“O”的情況,鎖定時(shí)間會(huì)很長(zhǎng),使其同步建立時(shí)間和調(diào)整精度變得相互制約。盡管有此缺點(diǎn),但由于這種結(jié)構(gòu)具有失鎖后的自我調(diào)節(jié)性,因此,碼元消失或是碼元相位出現(xiàn)抖動(dòng)時(shí),同步脈沖不會(huì)出現(xiàn)較大變化,仍然可以輸出穩(wěn)定的同步脈沖。由于采用曼徹斯特碼進(jìn)行傳輸,該設(shè)計(jì)主要應(yīng)用于地鐵車輛總線上,傳輸速率為250 Kb/s,速率較低,且每個(gè)碼元內(nèi)都有一次電平跳變,不會(huì)出現(xiàn)連續(xù)的“O”或“1”,因此采用閉環(huán)的超前一滯后全數(shù)字鎖相環(huán)非常適合提取比特流中的位時(shí)鐘。基本結(jié)構(gòu)如圖1所示,主要由數(shù)字鑒相器(DPD)、數(shù)字環(huán)路濾波器(DLF)、數(shù)控振蕩器(DCO)三部分構(gòu)成。DPLL是一種相位反饋控制系統(tǒng),它將輸入信號(hào)Data_in與本地恢復(fù)時(shí)鐘Clk_DPD之間的相位誤差(超前還是滯后)信號(hào)送入數(shù)字環(huán)路濾波器DLF中,對(duì)相位誤差信號(hào)進(jìn)行平滑濾波,并生成控制DCO動(dòng)作的控制信號(hào),DCO根據(jù)控制信號(hào)給出的指令,調(diào)節(jié)內(nèi)部高速振蕩器的震蕩頻率,通過(guò)連續(xù)不斷的反饋調(diào)節(jié),使其輸出時(shí)鐘Clk_DPD的相位跟蹤輸入數(shù)據(jù)Data_in的相位。

2 環(huán)路功能及其實(shí)現(xiàn)方法

下面沿環(huán)路依次介紹DPLL環(huán)路各個(gè)組成模塊的詳細(xì)功能、內(nèi)部結(jié)構(gòu)、對(duì)外接口信號(hào)及實(shí)現(xiàn)方法。

2.1 鑒相器結(jié)構(gòu)及其工作原理

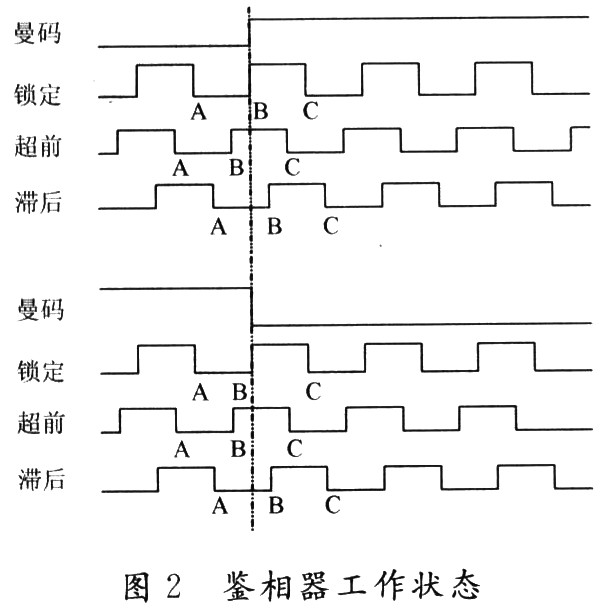

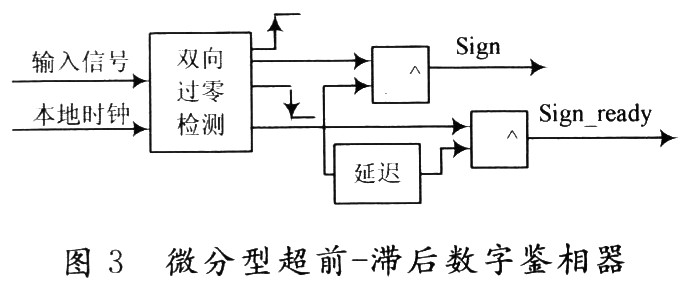

超前一滯后型數(shù)字鑒相器輸出一個(gè)表示本地估算信號(hào)超前或滯后于輸入信號(hào)的量。如果本地估算信號(hào)超前于輸入信號(hào),則輸出“超前脈沖”,以便利用該“超前脈沖”控制本地估算信號(hào)的相位推后。反之,則輸出“滯后脈沖”,并使本地估算信號(hào)的相位前移,這樣隱含在曼徹斯特碼中的位時(shí)鐘就被鑒相器比較了出來(lái)。超前一滯后型數(shù)字鑒相器可分為積分型和微分型兩種。積分型超前一滯后數(shù)字鑒相器,結(jié)構(gòu)和硬件實(shí)現(xiàn)比較復(fù)雜,但具有優(yōu)良的抗干擾性能。而微分型數(shù)字鑒相器結(jié)構(gòu)相對(duì)簡(jiǎn)潔,硬件實(shí)現(xiàn)也比較簡(jiǎn)單,但是它的抗干擾能力比較差。這里采用微分型超前一滯后型數(shù)字鑒相器,將抗干擾的任務(wù)留給后面的數(shù)字濾波器環(huán)節(jié)實(shí)現(xiàn)。DPD的工作狀態(tài)如圖2所示。

![]()

當(dāng)Sign為1時(shí),表示本地時(shí)鐘超前于輸入信號(hào);當(dāng)Sign為O時(shí),表示本地時(shí)鐘落后于輸入信號(hào)。

當(dāng)Sign_ready=1時(shí),表示輸入信號(hào)有跳變,Sign有效;當(dāng)Sign_readyr=0時(shí),表示輸入信號(hào)無(wú)跳變,Sign無(wú)效。

微分型超前一滯后數(shù)字鑒相器的原理圖如圖3所示。

2.2 數(shù)字濾波器結(jié)構(gòu)及其買現(xiàn)方法

在數(shù)字鎖相環(huán)路中,環(huán)路濾波器通常使用數(shù)字濾波器,它們與模擬鎖相環(huán)路中的模擬環(huán)路濾波器相對(duì)應(yīng)。數(shù)字環(huán)路濾波器在環(huán)路中對(duì)輸入噪聲起抑制作用,并且對(duì)環(huán)路的校正速度起調(diào)節(jié)作用。

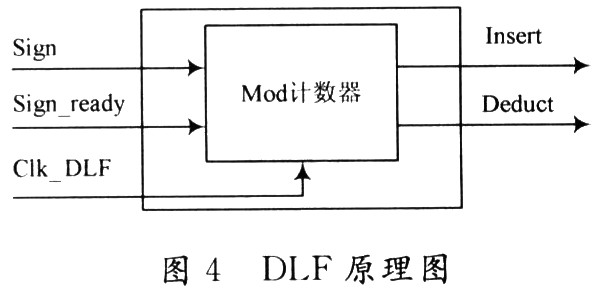

由于采用微分型超前一滯后型數(shù)字鑒相器,隨機(jī)噪聲會(huì)引起DPD的相位抖動(dòng),會(huì)生成影響DCO動(dòng)作的控制脈沖,所以對(duì)于DPD輸出的Sign和Sign_ready不能作為直接驅(qū)動(dòng)指導(dǎo)后面DCO的控制信號(hào),DPD的濾波功能是通過(guò)一個(gè)Mod為8的計(jì)數(shù)器來(lái)實(shí)現(xiàn)的。當(dāng)Sign_ready為1時(shí),DPD的Mod開(kāi)始加減計(jì)數(shù)(Mod復(fù)位后為8),計(jì)數(shù)的方向由Sign來(lái)控制。當(dāng)Sign為1時(shí),表示本地時(shí)鐘超前于輸入信號(hào),Mod做加法計(jì)數(shù),逐次加法直到15,進(jìn)位變?yōu)?,Inset輸出一個(gè)1μs的高電平;同樣,當(dāng)Sign為0時(shí),表示本地時(shí)鐘超前于輸入信號(hào),Mod做減法計(jì)數(shù),逐次加法直到1,借位變?yōu)?,Deduct輸出一個(gè)1μs的高電平。DLF原理圖如圖4所示。

由于噪聲和抖動(dòng)一般是無(wú)序的,除非噪聲在同一方向出現(xiàn)8次,濾波器才會(huì)輸出誤動(dòng)作。另外Clk_DLF是Clk_DPD的兩倍頻率,有助于提高濾波精度。

2.3 振蕩器結(jié)構(gòu)及其實(shí)現(xiàn)方法

數(shù)控振蕩器,又稱為數(shù)字鐘,它在數(shù)字鎖相環(huán)路中所處的地位相當(dāng)于模擬鎖相環(huán)中的電壓控制振蕩器。它的輸出是一個(gè)脈沖序列,而該輸出脈沖序列的周期受數(shù)字環(huán)路濾波器產(chǎn)生的校正信號(hào)所控制。本次設(shè)計(jì)主要采用加、扣脈沖式DCO,該振蕩器的特點(diǎn)是每一個(gè)鑒相周期輸出本地估算信號(hào)是超前或者滯后于輸入信號(hào)的信息,經(jīng)濾波器處理后輸出加或扣脈沖信號(hào),以此控制DCO的輸出相位。

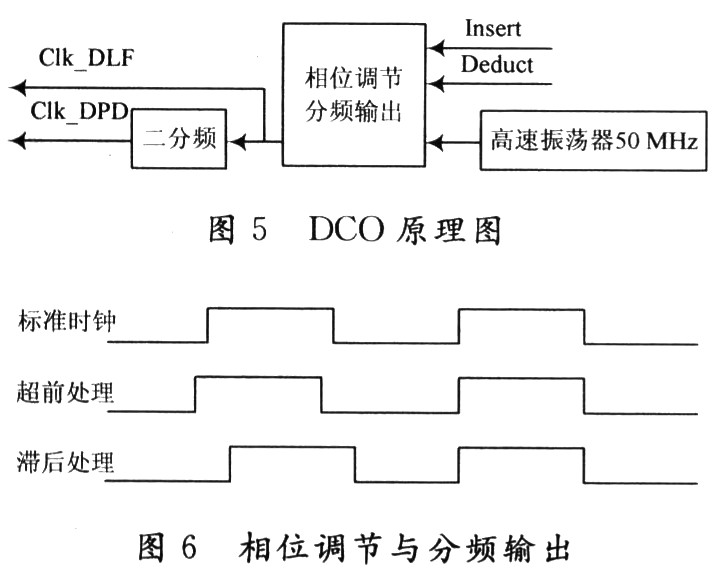

DCO根據(jù)DLF輸出的Insert和Deduct來(lái)調(diào)節(jié)本地時(shí)鐘,輸出與曼徹斯特碼位信號(hào)同相同頻的時(shí)鐘。另外,DPD和DLF的工作時(shí)鐘也由DCO產(chǎn)生(Clk_DPD和Clk_DLF同相,前者是后者頻率的1/2),構(gòu)成了DPLL系統(tǒng)閉環(huán)。DCO原理圖如圖5所示。一般DCO分為三個(gè)工作模塊,即高速振蕩器、相位調(diào)節(jié)器和分頻器。由于本次設(shè)計(jì)的特殊性,將DCO劃分為兩個(gè)工作模塊,即將相位調(diào)節(jié)器和分頻器合并,由DLF產(chǎn)生的Insert和Deduct來(lái)指導(dǎo)相位調(diào)節(jié),并輸出系統(tǒng)要求的位信號(hào)時(shí)鐘。

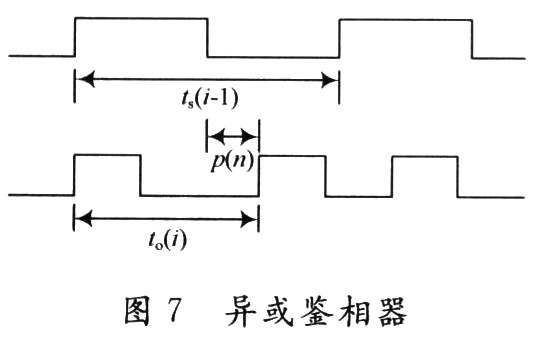

相位調(diào)節(jié)與分頻輸出如圖6所示。

由于之前的DLF的Mod為8,而Clk_DLF的頻率是500 kHz,周期即2μs,所以每次調(diào)節(jié)的相位最小單位為120 ns,20 ns×(5+1)=120ns。DLF在同一方向上接到DPD的Sign信號(hào)4次后動(dòng)作,由于本次項(xiàng)目做曼徹斯特解碼時(shí),前導(dǎo)碼是32個(gè),換算成位信號(hào)有64個(gè),由于曼徹斯特碼是10交替的,故輸入信號(hào)的有效跳變是32次。經(jīng)過(guò)多次仿真和實(shí)驗(yàn),DPLL一般在前25個(gè)前導(dǎo)碼內(nèi)即可穩(wěn)定,穩(wěn)定后在120 ns的范圍內(nèi)跳動(dòng)。

3 鎖相環(huán)路建模及分析

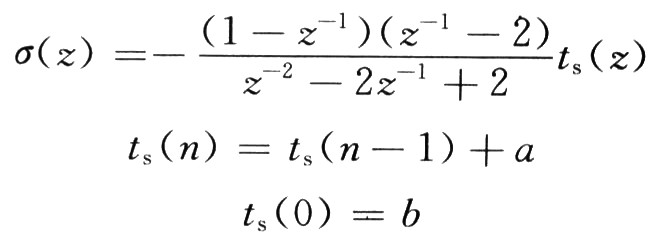

定義如下變量:ts為外加信號(hào)周期;to為反饋信號(hào)周期;p(n)為輸出信號(hào)和外加信號(hào)的相位差。當(dāng)輸出信號(hào)和外加信號(hào)的相位差小于π時(shí),鑒相特性是線性的,如圖7所示。

![]()

異或鑒相器的輸出為:

q(n)=q(n-1)+p(n) (2)

由上可得出反饋信號(hào)周期與輸入信號(hào)周期的差分方程:

to(n)=ts(n-1)+q(n-1)+ε{u(n-1)·[ts(n-1)-ts(n-2)]} (3)

式中:ε[·]是由于相位差引入的一個(gè)二階量,當(dāng)p(n)很小時(shí),ε[·]是一個(gè)無(wú)窮小的量。在p(0)=O,q(O)==0,ε[·]=0的情況下,對(duì)式(3)進(jìn)行z變換得:

![]()

其特征方程為:

![]()

解得:z1,2=0.5±0.5i,z3=0

由于|z1,2|=0.707<1,|z3|=0

由此可知,系統(tǒng)穩(wěn)定。接下來(lái)討論系統(tǒng)對(duì)輸入信號(hào)的跟蹤誤差:

式中:b>0,當(dāng)|b|/|a|足夠小時(shí),對(duì)上式做單邊z變換,利用中值定理得:

![]()

由此可見(jiàn),穩(wěn)態(tài)誤差取決于輸入信號(hào)與本地信號(hào)初始相位誤差。由于系統(tǒng)最后穩(wěn)定在120 ns內(nèi),而每個(gè)待鎖定碼元的寬度是2 000 ns,使用△表示鎖定后的最大誤差范圍,可得:![]()

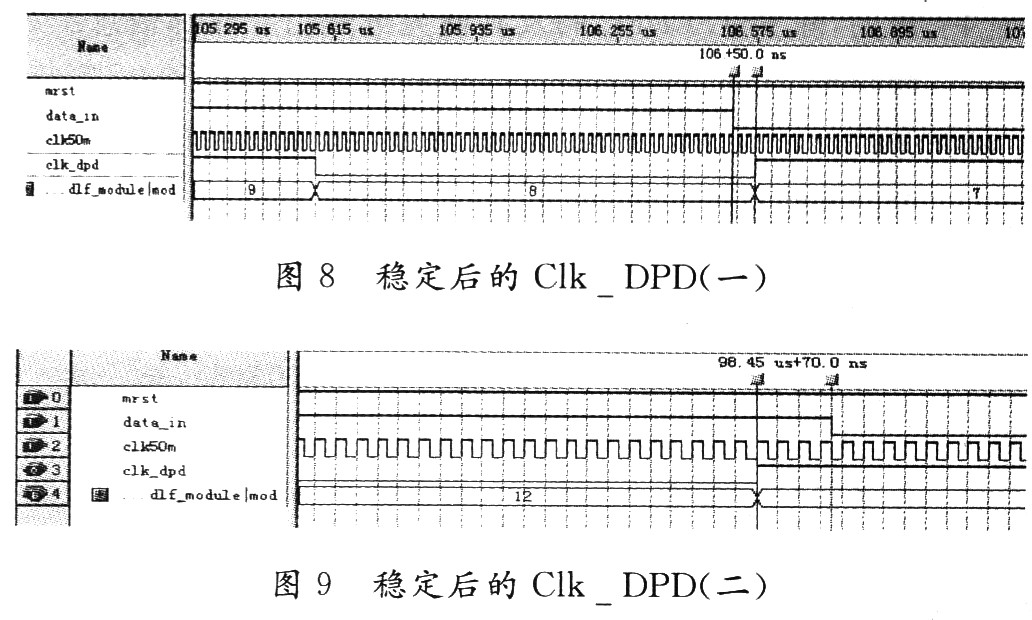

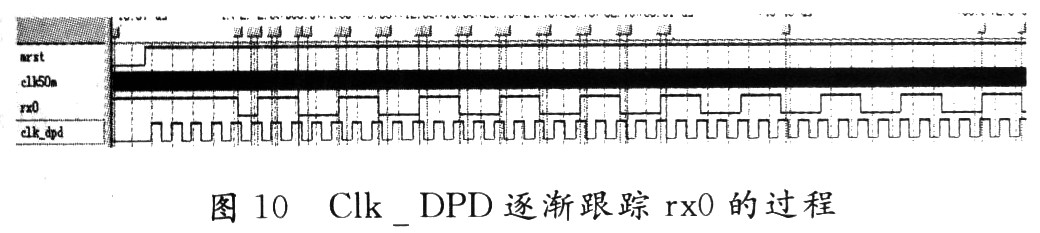

可見(jiàn),穩(wěn)定后,偏移量△最多不超過(guò)6%。所以120 ns的穩(wěn)態(tài)誤差能滿足需要,系統(tǒng)可根據(jù)DPLL輸出周期為2μs的同步位時(shí)鐘下降沿可靠采樣,避免了亞穩(wěn)態(tài)現(xiàn)象的發(fā)生。穩(wěn)定后的Clk_DPD如圖8、圖9所示,滯后50ns,累計(jì)4次后,超前70ns,穩(wěn)定于絕對(duì)誤差120ns。Clk_DPD逐漸跟蹤rx0提取出其中隱含的位時(shí)鐘的過(guò)程如圖10所示。

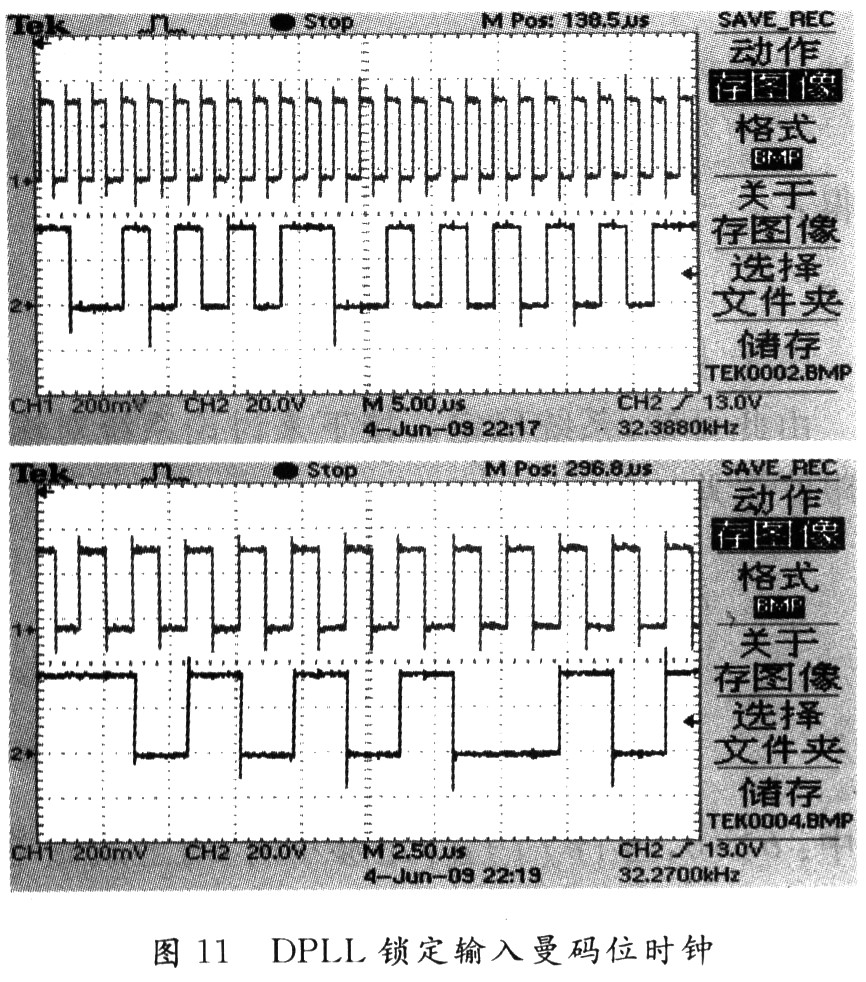

示波器撲捉到DPLL鎖定輸入的曼徹斯特碼位時(shí)鐘的波形如圖11所示。

4 結(jié) 語(yǔ)

本文主要研究了一種基于FPGA、自頂向下、模塊化、用于提取位同步時(shí)鐘的全數(shù)字鎖相環(huán)設(shè)計(jì)方法。應(yīng)用Verilog硬件描述語(yǔ)言使設(shè)計(jì)更加靈活,不僅縮短了設(shè)計(jì)周期,而且可實(shí)現(xiàn)復(fù)雜的數(shù)字電路系統(tǒng)。本文測(cè)試中所用的待鎖定輸人數(shù)據(jù)由AM7960芯片輸出的曼徹斯特碼提供,通信速率為250 Kb/s,經(jīng)由MAx3485轉(zhuǎn)換成LVTTL電平信號(hào),輸入FPGA芯片EPlC3T10017。由于曼徹斯特碼在每個(gè)碼元內(nèi)有一次跳變,鎖定后的時(shí)鐘是500 Kb/s。經(jīng)仿真測(cè)試,該DPLL具有鎖定相位時(shí)間短,鎖定后相位穩(wěn)定的特點(diǎn),最大偏差不超過(guò)6%,這在理論上已加以證明,從而驗(yàn)證了設(shè)汁的正確性。