現(xiàn)代計算機和通信系統(tǒng)中廣泛采用數(shù)字信號處理的技術(shù)和方法,其基本思路是先把信號用一系列的數(shù)字來表示,然后對這些數(shù)字信號進行各種快速的數(shù)學運算。其目的是多種多樣的,有的是為了加密,有的是為了去掉噪聲等無關(guān)的信息,稱為濾波;有時也把某些種類的數(shù)字信號處理運算成為變換,如離散的傅里葉變換,小波變換等。VerilogHDL是目前應用最廣泛的一種硬件描述語言,用于數(shù)字電子系統(tǒng)的設計。可用它進行各種級別的邏輯設計,并進行數(shù)字邏輯系統(tǒng)的仿真驗證,時序分析,邏輯綜合。小波濾波器的設計屬于復雜算法的電路設計,因此利用Veril—ogHDL對雙正交小波濾波器進行建模、仿真,實現(xiàn)電路的自動化設計,將是一種較為理想的方法。

Verilog HDL介紹

Verilog HDL是一種硬件描述語言,是一種以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。 Verilog HDL和VHDL是目前世界上最流行的兩種硬件描述語言,都是在20世紀80年代中期開發(fā)出來的。前者由Gateway Design Automation公司開發(fā)。兩種HDL均為IEEE標準。

Verilog HDL就是在用途最廣泛的C語言的基礎(chǔ)上發(fā)展起來的一種硬件描述語言,它是由GDA公司的PhilMoorby在1983年末首創(chuàng)的,最初只設計了一個仿真與驗證工具,之后又陸續(xù)開發(fā)了相關(guān)的故障模擬與時序分析工具。1985年Moorby推出它的第三個商用仿真器Verilog-XL,獲得了巨大的成功,從而使得Verilog HDL迅速得到推廣應用。1989年CADENCE公司收購了GDA公司,使得VerilogHDL成為了該公司的獨家專利。1990年CADENCE公司公開發(fā)表了Verilog HDL,并成立LVI組織以促進Verilog HDL成為IEEE標準,即IEEE Standard 1364-1995.

Verilog HDL的最大特點就是易學易用,如果有C語言的編程經(jīng)驗,可以在一個較短的時間內(nèi)很快的學習和掌握,因而可以把Verilog HDL內(nèi)容安排在與ASIC設計等相關(guān)課程內(nèi)部進行講授,由于HDL語言本身是專門面向硬件與系統(tǒng)設計的,這樣的安排可以使學習者同時獲得設計實際電路的經(jīng)驗。與之相比,VHDL的學習要困難一些。但Verilog HDL較自由的語法,也容易造成初學者犯一些錯誤,這一點要注意。

l 小波濾波器的設計

對于小波函數(shù),要求它具有正交性、緊支集、對稱性和平滑性。正交性可以使變換無冗余;緊支集則帶來優(yōu)良的空間分辨率;對稱性保證了與其對應濾波器的相位為線性;平滑性可以產(chǎn)生較小的失真。這樣使離散二進小波變換受到很大的限制,為此,人們提出一種雙正交的小波變換。本文設計小波濾波器正是基于雙正交小波變換的一種雙通道完全重構(gòu)濾波器,因此可以對信號進行分解后實現(xiàn)精確重構(gòu),所以對信號的濾波有很好的作用。由于它具有正變換二元上抽樣采樣和反變換二元下抽樣采樣特性,在進行濾波器設計時可以將雙正交小波濾波器設計成具有多相結(jié)構(gòu)的雙通道完全重構(gòu)濾波器。雙正交小波變換可以看成原始信號通過一系列高低通濾波器濾波并經(jīng)過抽樣后所得到的結(jié)果,重構(gòu)過程與此相反。為了使變換后的信號能夠完全重建,須滿足Y(n)=x-kX(n),在這里取k=1。雙正交小波濾波器分解和重構(gòu)過程如圖1所示。

設G(z),H(z)分別為分解低通,高通濾波器,下采樣后用H(z)濾波等價于先用H(z2)濾波,然后下采樣,所以:

其中:Ge和Go分別是G(z)的偶數(shù)項和奇數(shù)項,He和H。分別是H(z)的偶數(shù)項和奇數(shù)項。根據(jù)式(1),式(2)可以建立雙正交小波濾波器的多相結(jié)構(gòu)模型如圖2所示。

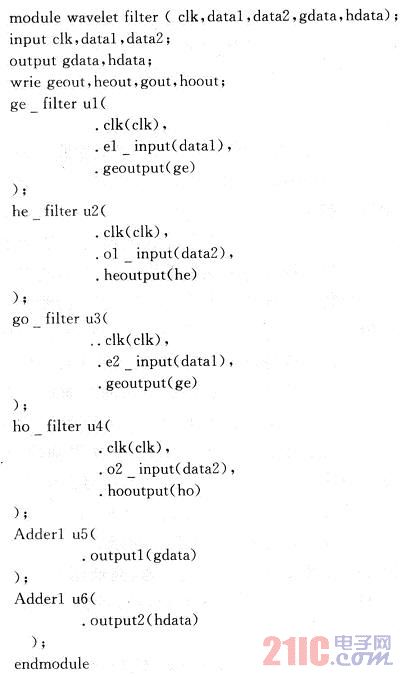

下面對雙正交小波濾波器用VerilogHDL進行頂層設計:

對于雙正交小波濾波器的部件Ge,Go,He,Ho設計,采用行為描述方式進行設計。VerilogHDL行為描述語言作為一種結(jié)構(gòu)化和過程性的語言,其語法結(jié)構(gòu)非常適合于算法級和RTL級的模型設計。在Veril—ogHDL語言中行為描述分為算法和RTL兩種。算法級:用語言提供的高級結(jié)構(gòu)能夠?qū)崿F(xiàn)算法的運行模型。RTL級:描述數(shù)據(jù)在寄存器之間的流動和如何處理,控制這些數(shù)據(jù)的流動,采用改進的DA算法(如圖3所示)。DA算法完成一次濾波所需要B次的累加也就是B個時鐘周期完成一次運算,B位輸入數(shù)據(jù)的位寬。它的查找表(LUT)的大小是由濾波器的階數(shù)N決定的,共需要2N個查找表單元,如果系數(shù)N過多,用單個LUT不能夠執(zhí)行全字查找則可把系數(shù)分組,利用部分表并將結(jié)果相加,為了簡單的闡述算法,在此系數(shù)只分了2組,每個單元的位寬是由濾波器的系數(shù)的量化決定的。Ge,Go,He,Ho四個濾波器雖然長度不同,但具有相同的電路結(jié)構(gòu),如圖4所示。

計算控制器用于控制濾波單元中移位寄存器移位,累加器的循環(huán)周期和計算輸出,并控制移位寄存器的數(shù)據(jù)輸入。

2 利用VerilogHDL語言實現(xiàn)以上功能

2.1 用VerilogHDL語言進行算法建模

計算機控制器的veril—ogHDL模型:

寄存器組中每個寄存器的位數(shù)為0,1,…,num一1。

2.2 定制ROM

QuartusⅡ包含有許多有用的LPM模塊,它們是復雜或高級系統(tǒng)構(gòu)建的重要組成部分,可以與QuartusⅡ普通設計文件一起使用,該文使用“Tools”菜單下的MegaWizardPlug—In Manager命令定制ROM的元件。如圖5所示。

2.3 用VerilogHDL進行數(shù)據(jù)流建模

濾波器的建模過程如下:

3 驗證仿真

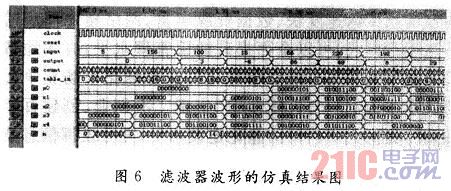

利用Altera公司的QuartusⅡ7.2軟件內(nèi)部帶有仿真器對濾波器的VerilogHDL模型進行波形仿真,通過建立正確的Vector Waveform File就可以開始仿真了。如圖6所示。

通過QuartusⅡ的波形仿真功能,對輸入輸出進行波形仿真,對其結(jié)果進行定量分析。通過時序分析和功能分析結(jié)果,對設計進行進一步的完善。在仿真中,in—put濾波器輸入數(shù)據(jù),output濾波器輸入數(shù)據(jù)x0,x1,x2,x3,x4為移位寄存器組中寄存器,count為控制計數(shù)器,table-in為流水線寄存器。所得結(jié)果如圖6所示。經(jīng)驗證,仿真結(jié)果和實際運算結(jié)果一致。所以對于大多數(shù)連續(xù)的LTI系統(tǒng)都可以采用以上方法進行分析,但是他也有局限性:對于時變系統(tǒng),非線性系統(tǒng)分析,它無能為力;只適合分析一維變量,對于多維變量,它無能為力;可采用狀態(tài)變量分析方法;就精確度來說,這種分析方法不是很高。

盡管連續(xù)LTI系統(tǒng)有很多缺點,但是通過對LTI系統(tǒng)的分析可以培養(yǎng)系統(tǒng)建模和求解能力,為以后分析其他系統(tǒng)作參考。