1 引 言

隨著各種便攜式移動通信和計算產(chǎn)品的普及,對電池的需求大大加強,但是電池技術(shù)發(fā)展相對落后,降低電路的功耗成為IC設(shè)計關(guān)注的一個焦點;電路的功耗會全部轉(zhuǎn)換成熱能,過多的熱量會產(chǎn)生焦耳熱效應(yīng),加劇硅失效,導(dǎo)致可靠性下降,而快速散熱的要求又會導(dǎo)致封裝和制冷成本提高;同時功耗大將導(dǎo)致溫度高,載流子速度飽和,IC速度無法再提升;并且功耗降低,散熱減少,也能減少對環(huán)境的影響。因此,功耗已成為超大規(guī)模集成電路設(shè)計中除速度,面積之外需要考慮的第三維度。

傳統(tǒng)的帶隙電壓基準(zhǔn)源面積大、功耗大、不適應(yīng)低功耗小面積的要求。本文立足于低功耗、小面積、利用工作于弱反型區(qū)晶體管的特點,對傳統(tǒng)的帶隙電壓基準(zhǔn)源做出改進,設(shè)計了一款最大消耗380 nA電流的電壓基準(zhǔn)源,大大減小了面積,且與CMOS工藝兼容,同時提出一種新的不耗電的啟動電路。本文先介紹傳統(tǒng)典型帶隙基準(zhǔn)電路的原理與功耗組成,提出改進電路結(jié)構(gòu),并進行分析,最后給出基于0.5μm CMOS工藝模型的仿真結(jié)果和測試結(jié)果。

2 傳統(tǒng)帶隙電壓基準(zhǔn)源

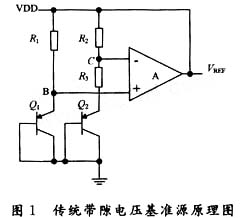

傳統(tǒng)帶隙基準(zhǔn)源如圖1所示。

由PTAT產(chǎn)生電路,負(fù)PTAT產(chǎn)生電路,放大器,加法器組成。原理是由Q1,Q2兩個PNP三極管和電阻R3產(chǎn)生PTAT電流,流過電阻R2產(chǎn)生PTAT電壓,再疊加上Q2的負(fù)PTAT電壓Vbe,通過合理調(diào)整電阻R2和R3的比例產(chǎn)生與溫度無關(guān)的電壓基準(zhǔn)。運算放大器A是為了保證B,C兩點電壓相等。

這種結(jié)構(gòu)需要三極管、運算放大器以及若干電阻,面積比較大。其工作時電流由3部分組成:Q1支路的集電極電流;Q2支路的集電極電路,運算放大器A的工作電流。其中Q1,Q2支路的電流為VTln N/R3,其中VT=kT/q;q是電荷常量;k是波爾滋曼常數(shù);T是絕對溫度;N是三極管Q2與Q1的比值,通常為8,同時要達到好的性能運算放大器的電流不能太小以使晶體管工作于飽和區(qū)。通常傳統(tǒng)帶隙電壓基準(zhǔn)源消耗電流不小于10μA。

3 弱反型區(qū)晶體管模型

本文利用了工作在弱反型區(qū)晶體管的特點,對傳統(tǒng)帶隙電壓基準(zhǔn)電路進行了改進。工作在弱反型區(qū)的晶體管特性模型假設(shè):

(1)晶體管溝道長度足夠長,溝道長度近似成立,并且溝道長度調(diào)制效應(yīng)可以忽略;

(2)空間電荷區(qū)的產(chǎn)生電流可以忽略;

(3)表面態(tài)密度和表面勢的波動可以忽略。

在這些假設(shè)之下,工作在弱反型區(qū)的晶體管的I-V特性可以表示為:

ID0是特征電流;S是晶體管的寬長比;n是斜率因子;VG,VS,VD分別為晶體管柵、源、漏端與襯底的電壓差。當(dāng)晶體管由相同的VS電壓偏置時,斜率因子n是常數(shù),ID0也可以認(rèn)為是常數(shù)。由式(1)可以看出,當(dāng)VD-VS》0時,弱反型工作的MOS晶體管與三極管的直流傳輸特性一致。

4 電路實現(xiàn)

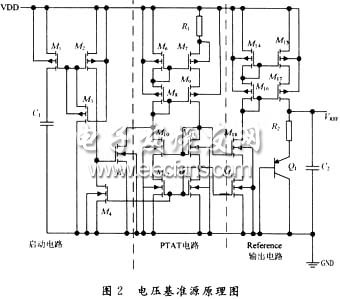

圖2為本文改進的電壓基準(zhǔn)源的原理示意圖。電壓基準(zhǔn)電路由3部分組成:啟動電路、PTAT產(chǎn)生電路和輸出電路。輸出電路包括電流放大和電壓疊加。

PTAT電路由M6-M13和R1構(gòu)成,利用其工作在弱反型區(qū)晶體管的特點,取代了傳統(tǒng)的三極管PTAT產(chǎn)生電路,且不需要運算放大器,面積大大減小,弱反型區(qū)晶體管特性令工作功耗大大降低。P型晶體管M6與M7組成第一對電流鏡,增益為S7/S6,N型晶體管M12與M13組成第二對電流鏡,增益為S12/S13,只要2路電流足夠小,電阻R1的影響就可以忽略,2路電流相等。M6~M13組成一個閉合環(huán)路,環(huán)路的增益為2組電流鏡增益的乘積。其中晶體管M6與M7的寬長比要足夠大,工作在弱反型區(qū),M12與M13溝道長度要足夠長,工作在飽和區(qū)。M8,M9和M10,M11分別與M6,M7和M12,M13構(gòu)成共源共柵結(jié)構(gòu),增大阻抗,提高基準(zhǔn)電壓源的電源抑制比。環(huán)路的起始增益大于1令兩支路的電流增加,直到平衡則增益降為1,電阻R1上的壓降為VR1。根據(jù)公式(1),VR1可以表示為:

則流過電阻R1的電流為:

由式(3)可以看出,電流IR只與晶體管寬長比,電阻R1,斜率因子n;波爾滋曼常數(shù)k,絕對溫度T有關(guān),與電源電壓無關(guān),是與溫度成正比的PTAT電流。

電壓基準(zhǔn)輸出電路由晶體管M14~M19,以及電阻R2,三極管Q1,電容C2組成。M18與M19鏡像PTAT電流同時M15與M17鏡像M18,M19支路的PTAT電流,組成電流放大,采用共源共柵結(jié)構(gòu)是為了鏡像更準(zhǔn)確。PTAT電流流過電阻R2,產(chǎn)生與溫度成正比的PTAT電壓,此PTAT電壓和二極管方式連接的三極管Q1的Vbe電壓疊加,產(chǎn)生與溫度無關(guān)的基準(zhǔn)電壓,電容C2是為了濾波,降低噪聲。

其中Eg為硅的帶隙能量;m為遷移率的溫度系數(shù)常數(shù)。

將式(7)代入(6)可以看出,只要合理設(shè)置晶體管的寬長比和電阻R2,R1的比值就可以得到與溫度無關(guān)的基準(zhǔn)電壓。

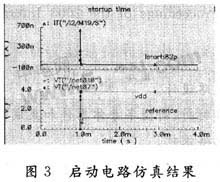

由于電壓基準(zhǔn)源電路存在2個電路平衡點,零點和正常工作點。當(dāng)基準(zhǔn)源工作在零點時,晶體管M8,M9柵源電壓為高,M10,M11管柵源電壓為低,PTAT電路沒有電流產(chǎn)生,啟動電路就是避免電壓基準(zhǔn)工作在零點上。本文提出的啟動電路的最大特點是不耗電,它由晶體管M1~M5以及電容C1組成。當(dāng)電源電壓為低時,若電容C1上存有電荷,則M3導(dǎo)通,將電荷放完,等電源電壓為高時,M1,M2導(dǎo)通,流過M2的瞬間大電流迅速將M5打開,同時將M8,M9的柵電位拉低導(dǎo)通,產(chǎn)生PTAT電流,電路正常工作,當(dāng)M12,M13柵壓升高時,M4導(dǎo)通,將M5柵壓拉低,啟動電路停止工作,幾乎不消耗電流,達到了低功耗的目的。啟動時間由M2管子的大小和電容C1決定。電壓基準(zhǔn)的啟動電路仿真結(jié)果如圖3所示,啟動時間只要50μs,啟動之后只要消耗82 pA的電流。若沒有M3,電容C1上可能存在電荷沒有放完,再次啟動時有啟動不了的可能。

5 版圖及測試結(jié)果

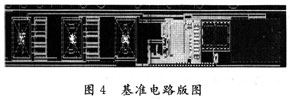

本文介紹的電壓基準(zhǔn)源采用CSMC 0.5 μm,兩層POLY,一層金屬的CMOS工藝實現(xiàn),已經(jīng)成功流片。該工藝的閾值電壓分別為N管0.87 V,P管-0.97 V。由于產(chǎn)生PTAT電流的2個P型管存在失調(diào)會導(dǎo)致2支路不平衡,版圖匹配技術(shù)可以減少失調(diào),在版圖中可以增加虛擬晶體管使匹配晶體管間的環(huán)境相同來減少失調(diào),同時,晶體管M7要在一個獨立的N阱中,使與M6的偏置條件一樣來減少失調(diào)。二極管可以用CMOS工藝中寄生的PNP三極管實現(xiàn),N阱中的P+區(qū)作為發(fā)射區(qū),N阱本身作為基區(qū),P型稱底作為集電區(qū),電阻采用具有負(fù)溫度系數(shù)的高阻POLY2電阻,方塊阻值為2 kΩ/□,節(jié)省面積。電壓基準(zhǔn)的版圖如圖4所示,版圖面積為:490μm×75μm-0.036 75 mm2。

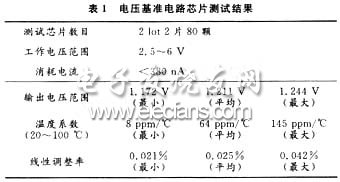

芯片在Micromanipulator 8860高精度探針臺和高精度溫度控制臺上進行測試,測試儀器為Agilent4155A半導(dǎo)體參數(shù)分析儀,芯片測試結(jié)果小結(jié)如表1所示。

芯片在Micromanipulator 8860高精度探針臺和高精度溫度控制臺上進行測試,測試儀器為Agilent4155A半導(dǎo)體參數(shù)分析儀,芯片測試結(jié)果小結(jié)如表1所示。

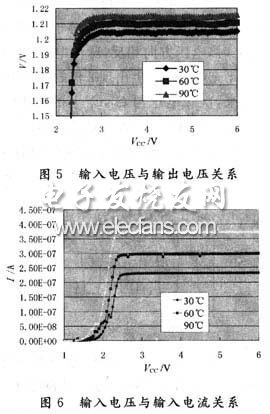

圖5是不同溫度下輸入電源電壓與輸出基準(zhǔn)電壓的關(guān)系圖。當(dāng)電源電壓大于2.5 V時,電壓基準(zhǔn)電路開始正常工作,由于用了共源共柵結(jié)構(gòu)來提高電源抑止比,最小輸入電壓降不下去。在測量的80顆芯片中,輸出電壓的平均值為1.211 V,最小值為1.172 V,最大值為1.244 V,與仿真結(jié)果1.251 V相近,誤差主要來自三極管模型的誤差以及PTAT支路匹配管的失調(diào)。在2.5~6 V的工作電壓范圍內(nèi),測得的線性電壓調(diào)整率平均值為0.025%,最小值為0.021%,最大值為0.042%。

圖6是不同溫度下電壓基準(zhǔn)電路消耗電流與電源電壓的關(guān)系。電壓基準(zhǔn)電路在正常工作時消耗電流與電源電壓無關(guān),與溫度成比例。在20~100℃之間,室溫下工作時消耗電流小于250 nA,100℃時工作電流不超過380 nA,與仿真結(jié)果吻合。在6 V工作電壓下,最大功耗不超過2.28μW。

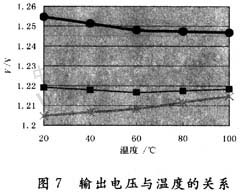

圖7是芯片的輸出電壓與溫度的關(guān)系圖。基準(zhǔn)電壓溫度系數(shù)的漂移受工藝參數(shù)的影響,如負(fù)溫度特性三極管的Vbe溫度系數(shù)在圓片不同位置,不同lot中的變化,PTAT匹配晶體管版圖上的失調(diào)等。在測試的80顆芯片中,溫度在20~100℃之間變化時,溫度系數(shù)在50 ppm/℃以下的有43顆,50~100 ppm/℃的有34顆,100~150 ppm的有4顆。

6 結(jié) 語

測試結(jié)果表明,電源電壓由2.5~6 V變化時,線性調(diào)整率平均為0.025%,溫度在20~100℃之間變化時,測得的平均溫度系數(shù)是64 ppm/℃。但是該電壓基準(zhǔn)電路由于采用了共源共柵結(jié)構(gòu),最小工作電壓2.5 V有點偏高,采用低壓共源共柵結(jié)構(gòu)將會獲得更優(yōu)的性能。