摘要:作為高傳輸速率和低設(shè)計成本的傳輸技術(shù),串行傳輸技術(shù)被廣泛應(yīng)用于高速通信領(lǐng)域,并已成為業(yè)界首選。在此基于對高速串行傳輸系統(tǒng)的分析,對實例進(jìn)行了總體設(shè)計驗證,最終達(dá)到高速傳輸?shù)哪康摹?/span>

隨著網(wǎng)絡(luò)技術(shù)的不斷發(fā)展,數(shù)據(jù)交換、數(shù)據(jù)傳輸流量越來越大。尤其像雷達(dá),氣象、航天等領(lǐng)域,不僅數(shù)據(jù)運算率巨大,計算處理復(fù)雜,而且需要實時高速遠(yuǎn)程傳輸,需要長期穩(wěn)定有效的信號加以支持,以便能夠獲得更加精準(zhǔn)的數(shù)據(jù)收發(fā)信息,更好的為工程項目服務(wù)。傳統(tǒng)的并行傳輸方式由于走線多、信號間串?dāng)_大等缺陷,無法突破自身的速度瓶頸。而串行傳輸擁有更高的傳輸速率但只需要少量的信號線,降低了背板開發(fā)成本和復(fù)雜度,滿足高頻率遠(yuǎn)距離的數(shù)據(jù)通信需求,被廣泛應(yīng)用到各種高速數(shù)據(jù)通信系統(tǒng)設(shè)計中。

目前,高速串行接口取代并行拓?fù)浣Y(jié)構(gòu)已經(jīng)是大勢所趨。當(dāng)今很多公用互連標(biāo)準(zhǔn)(如USB,PCI-Express)都是基于串行連接來實現(xiàn)高速傳輸?shù)摹O啾扔诓⑿锌偩€,串行連接的物理緊密度和鏈路韌性具有很多優(yōu)勢。因此,很多傳輸領(lǐng)域都轉(zhuǎn)向了串行傳輸,如筆記本電腦顯示互連、高速背板互連和存儲器內(nèi)部互連。該系統(tǒng)涉及到的技術(shù)主要包括:光纖傳輸、PCIE(PCI-Express)傳輸和DDR緩存技術(shù),以及這幾種技術(shù)在FPGA中融合為一個完整的串行傳輸鏈路,并實現(xiàn)了在兩臺服務(wù)器之間的高速數(shù)據(jù)傳輸測試,這對于實際工程應(yīng)用具有重要的現(xiàn)實意義。

1 系統(tǒng)結(jié)構(gòu)

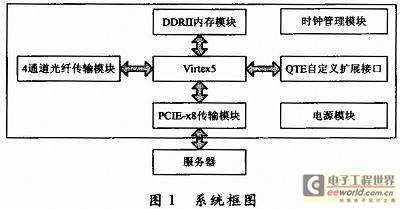

高速串行傳輸系統(tǒng)作為數(shù)據(jù)采集、傳輸、存儲中的一部分,對傳輸性能指標(biāo)有著嚴(yán)格的要求。該系統(tǒng)要完成光信號到PCI-Express接口信號的相互轉(zhuǎn)換,并在轉(zhuǎn)換過程中完成數(shù)據(jù)的高速傳輸。信號一般可達(dá)4.25Gb/s,處理如此高的數(shù)據(jù)對硬件設(shè)計提出了很大的挑戰(zhàn)。其中所包含的硬件有:高速光電轉(zhuǎn)換電路,FPGA數(shù)據(jù)處理電路、DDRⅡ數(shù)據(jù)緩存電路、時鐘管理電路、PCIE傳輸模塊電路、電源模塊電路、自定義擴(kuò)展接口電路。系統(tǒng)框圖如圖1所示。

技術(shù)要求主要有以下幾點:首先,傳輸卡中的4個光纖通道,每通道要達(dá)到2Gb/s以上。其次,PCIE傳輸速率不小于6Gb/s,支持DMA傳輸。再有,光纖和PCI-E傳輸誤碼率要小于1×10-10,連續(xù)傳輸相對穩(wěn)定。

圖1中各個模塊的功能如下:Virtex5作為傳輸卡的核心,用來實現(xiàn)數(shù)據(jù)從光纖接口到PCIE接口的高速轉(zhuǎn)換。光纖傳輸模塊的作用是將內(nèi)部數(shù)據(jù)經(jīng)過編碼后,通過光纜傳輸給接收系統(tǒng),以及接收外來光數(shù)據(jù),并將光數(shù)據(jù)傳送給FPGA處理電路DDR緩存模塊的作用,就是將傳輸過程中的高速數(shù)據(jù),進(jìn)行緩存,以保持?jǐn)?shù)據(jù)的完整性。PCI-Express傳輸模塊的作用,就是與PC之間實現(xiàn)PCI-Express傳輸協(xié)議,與PC實現(xiàn)串行數(shù)據(jù)傳輸,同時與外部擴(kuò)展接口,DDR緩存,光纖傳輸模塊實現(xiàn)內(nèi)部并行數(shù)據(jù)的交換。QTE自定義接口模塊的作用,就是進(jìn)行外部功能擴(kuò)展。比如,可以擴(kuò)展高速數(shù)據(jù)采集板卡、存儲硬盤卡、圖像采集卡等。時鐘管理模塊的作用,是給光纖傳輸模塊提供參考時鐘。時鐘頻率由FPGA的時鐘控制模塊控制。根據(jù)光模塊的性能,給出指定的時鐘。PCI-Express的參考時鐘,是通過芯片從PC主板上提取的。電源管理模塊的作用,是給整個系統(tǒng)提供各種不同的電壓。

2 系統(tǒng)模塊設(shè)計與實現(xiàn)

為了實現(xiàn)所要求的系統(tǒng)配置,更好地發(fā)揮各模塊自身及相互之間的作用,必須對模塊間進(jìn)行系統(tǒng)的協(xié)議分析。該系統(tǒng)的數(shù)據(jù)傳輸是雙向的,既可以傳輸數(shù)據(jù),也可以接收數(shù)據(jù)。它主要由電源管理模塊,時鐘管理模塊,PCI-Express傳輸模塊,DDR緩存模塊,光纖傳輸模塊和外部擴(kuò)展接口組成。其中,時鐘控制模塊和Aurora發(fā)送模塊、Aurora接收模塊是整個設(shè)計的重點。

2.1 時鐘控制模塊

時鐘控制模塊主要用來控制FPGA外圍的時鐘芯片ICS8442來產(chǎn)生所需要的高信噪比、低抖動的差分時鐘。

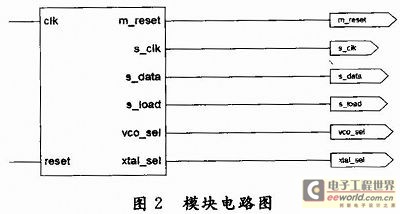

其模塊電路如圖2所示:輸出其中的信號用來完成對ICS8442的編程,使其能夠產(chǎn)生所需要的時鐘信號。

ICS8442的性能參數(shù)如下:

輸出信號頻率范圍為31.25~700MHz;晶振頻率范圍為10~25MHz;VCO頻率范圍為250~700MHz;ICS8442是LVDS邏輯電平,具有極低的相位噪聲,這種特性使它非常適合用來為吉比特以太網(wǎng)或同步光纖網(wǎng)提供時鐘信號。

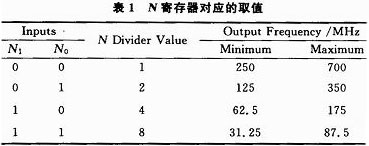

ICS8442的內(nèi)部結(jié)構(gòu)圖3所示。ICS8442內(nèi)部有一個完整的PLL鎖相環(huán),其VCO的輸出頻率范圍在250~700MHz之間,倍頻系數(shù)是由M決定的,M的取值范圍在10~28之間。VCO的輸出頻率為:

![]()

ICS8442最終的輸出結(jié)果還要經(jīng)過一個分頻器N,最終輸出結(jié)果的頻率和晶振輸入頻率的關(guān)系式為:

![]()

中:N是一個2位的寄存器,其對應(yīng)的取值如表1所示。

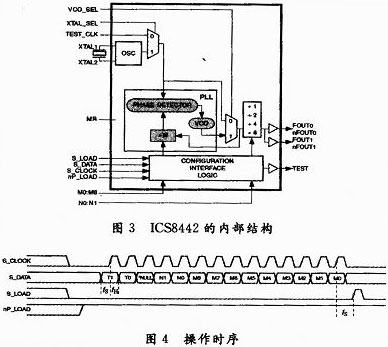

對ICS8442時鐘芯片的操作主要是對寄存器M,N的寫操作。ICS8442支持并行寫操作和串行寫操作,根據(jù)硬件電路的設(shè)計,程序采用串行的寫操作時序。當(dāng)ICS8442的nP_LOAD置為高電平和S_LOAD置為低電平時,芯片實現(xiàn)串行操作。操作時序如圖4所示。

當(dāng)S_LOAD置為低且nP_LOAD置為高之后,數(shù)據(jù)在S_CLOCK的上升沿處寄存在緩沖器中,在S_LOAD的下降沿處將數(shù)據(jù)鎖存到寄存器M,N中。

由于AURORA光纖通信的輸出時鐘頻率設(shè)定的是125MHz,結(jié)合硬件電路的設(shè)計,硬件晶振的頻率為20MHz,因此選擇M值為000011001(25),N的值為10(4),故時鐘芯片的時鐘輸出頻率為:

![]()

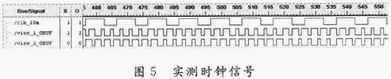

時鐘控制模塊的實測時鐘信號如圖5所示。

圖5是用Chipscope在線邏輯分析儀得到的波形,由于Chipscope在線邏輯分析儀的觸發(fā)時鐘是100MHz,因此在抓取125MHz的時鐘信號時,在圖上顯示的時鐘信號占空比不定,若將時鐘芯片產(chǎn)生的時鐘頻率降低,則此現(xiàn)象消失。

2.2 AURORA發(fā)送模塊

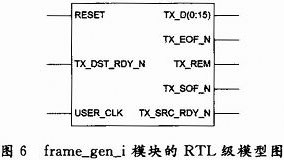

在生成AURORA IP CORE時,同時生成了一個基于AURORA協(xié)議的例示程序。因此,要實現(xiàn)基于AURORA協(xié)議的光纖通信,在發(fā)送端只需要在frame_gen_i模塊將要發(fā)送的數(shù)據(jù)打包,然后通過AURORA模塊發(fā)送出去。因此該模塊著重介紹如何將上一級傳送過來的數(shù)據(jù)進(jìn)行打包壓縮,形成適合AURORA協(xié)議的數(shù)據(jù)幀,通過AURORA協(xié)議發(fā)送到接收端。圖6為frame_gen_i模塊的RTL級模型圖。

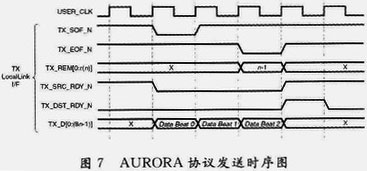

考慮到上一級傳輸數(shù)據(jù)速率可能會與AURORA傳輸?shù)臅r鐘頻率不同,因此在發(fā)送端建立一個FIFO來做緩沖器。并且AURORA協(xié)議的發(fā)送時序圖如圖7所示。可以看出,TX_SOF_N為數(shù)據(jù)包幀的開始標(biāo)志,TX_EOF_N為數(shù)據(jù)包幀的結(jié)束.標(biāo)志,TX_REM[0:r(n)]記錄最后的傳輸數(shù)據(jù)的線程,TX_SRC_RDY_N為低代表數(shù)據(jù)有效,TX_DST_RDY_N為低代表準(zhǔn)備好接受數(shù)據(jù),TX_D[0:(8n-1)]是此模塊的輸出數(shù)據(jù)。以上信息是AURORA協(xié)議的發(fā)送時序,在使用FIFO做緩沖時也應(yīng)該遵循這樣的協(xié)議。

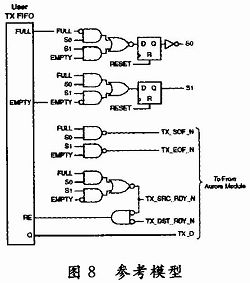

發(fā)送端的FIFO模塊分別包括FIFO的復(fù)位信號、FIFO空、FIFO滿、以及讀/寫時鐘、使能和數(shù)據(jù)信號線。因此應(yīng)該根據(jù)FIFO的標(biāo)志位empty和full來產(chǎn)生AURORA的發(fā)送時序,參考模型如圖8所示:當(dāng)RESET信號到來之時,首先將S0置為高電平,將S1置為低電平,同時根據(jù)FULL和EM-PTY的狀態(tài)確定接下來的S0和S1的狀態(tài),進(jìn)而根據(jù)以上邏輯關(guān)系得到TX_SOF_N,TX_EOF_N,TX_SRC_RDY_N等邏輯信號,并且根據(jù)數(shù)據(jù)X_DST_RDY_N和TX_SRC_RDY_N生成FIFO的讀使能。由以上邏輯可以看出,只有在FULL為1,EMPTY為0時,F(xiàn)IFO的讀使能才能被打開。TX_SOF_N為數(shù)據(jù)包的幀頭標(biāo)志,TX_EOF_N為數(shù)據(jù)包的幀尾標(biāo)志,TX_STC_RDY_N為低時代表數(shù)據(jù)有效,TX_DST_RDY_N為輸入信號,根據(jù)此輸入信號確定FIFO的讀寫時序。

對FIFO時序操作需要根據(jù)上述電路圖所產(chǎn)生。在上述電路圖中,有一個D觸發(fā)器,其RESET信號是復(fù)位信號,復(fù)位既是將觸發(fā)器輸出端口清零,即將S0置1,將S1置0。在之前的程序中誤將這里寫反,即RESET信號到來之后,將S0置0,S1置1。這樣導(dǎo)致的結(jié)果是在最開始輸入的一段數(shù)據(jù)丟失,之后的結(jié)果輸出正常。經(jīng)過仿真分析之后檢查出問題并已改正。

2.3 AURORA接收模塊

同樣在AURORA協(xié)議模塊中,要實現(xiàn)對數(shù)據(jù)的接收,只需在frame_check模塊中對接收的代碼加以修改,增加自己所需要的內(nèi)容,完成對數(shù)據(jù)的解碼提取,剔除冗余信息,并完成數(shù)據(jù)的緩存。

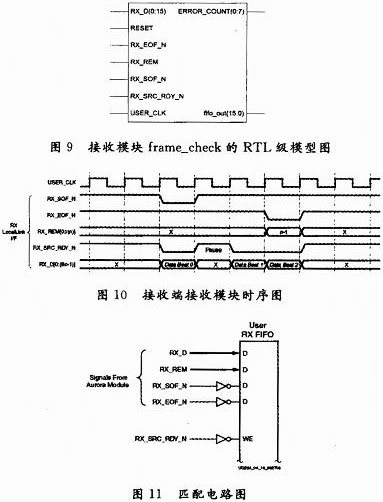

接收模塊frame_check的RTL級模型圖如圖9所示:其中,RX_D為接收端接收的緩存于FIFO的數(shù)據(jù),REsET為復(fù)位信號,RX_EOF_N為數(shù)據(jù)包幀尾的標(biāo)志,RX_SOF_N為數(shù)據(jù)包幀頭的標(biāo)志,TX_SRC_RDY_N為低時代表數(shù)據(jù)有效,USER_CLK為系統(tǒng)時鐘。fifo_out為數(shù)據(jù)緩存的輸出,ERROR _COUNT為系統(tǒng)檢錯輸出結(jié)果。因此在接收端接收模塊的時序圖如圖10所示。根據(jù)該時序圖可以確定接收時序,同樣,在AURORA協(xié)議末端,由于與下一級系統(tǒng)的速率可能不匹配,因此需要在接收末端加上一個FIFO做緩存,同樣其電路圖如圖11所示:根據(jù)RX_SRC_RDY_N生成FIFO的寫使能信號,該發(fā)送模塊設(shè)計完畢。

3 測試分析

3.1 功能測試

在基本功能測試中,主要測試光纖模塊傳輸是否正確。由于光纖模塊共有A,B,C,D四個通道,對每個通道都要進(jìn)行讀/寫測試。將通道A作為數(shù)據(jù)發(fā)送端,通道B作為數(shù)據(jù)接收端,應(yīng)用光纖將A,B兩端進(jìn)行聯(lián)通,然后將應(yīng)用程序數(shù)據(jù)寫入A通道FIFO中,當(dāng)FPGA接收到到數(shù)據(jù)后,將A通道數(shù)據(jù)通過光纖傳輸?shù)酵ǖ繠接收緩存中,然后通道B將數(shù)據(jù)發(fā)送到上位機(jī),從而形成一個環(huán)路。比較發(fā)送和接受端的數(shù)據(jù),可以驗證數(shù)據(jù)傳輸?shù)恼_性。同理可以將此方法應(yīng)用于四個通道中的任意兩個作為發(fā)送端和接收端,從而驗證并測試傳輸功能。

3.2 性能測試

性能主要對其傳輸速度和傳輸誤碼率進(jìn)行測試。就傳輸速度而言,主要由FPGA控制,在其內(nèi)部設(shè)置了兩個初始值為0的計數(shù)器,在PCI-Express開始傳輸數(shù)據(jù)時,F(xiàn)PGA開始計數(shù)讀/寫數(shù)據(jù)包和發(fā)送數(shù)據(jù)包的個數(shù),然后每隔一段時間將計數(shù)值寫入兩個計數(shù)寄存器中,并將原有值替換,為了精確速率,可以縮短計數(shù)時間,并多次測試取平均值,就可得到傳輸瞬時速度。經(jīng)測試:PCI-Express接口的傳輸速度在600MB/s,光纖傳輸在850MB/s,滿足設(shè)計要求。對于誤碼率的測試,主要使用誤碼分析軟件對其誤碼性能進(jìn)行測量,設(shè)計由上位機(jī)和PCI-Express接口,光纖通道組成數(shù)據(jù)傳輸環(huán)路,通過不同的指令和要求驗證傳輸正確性,當(dāng)數(shù)據(jù)包大小在4Kb,8Kb,16Kb,32Kb,測試數(shù)據(jù)長度分別為1000Kb,1000000Kb,100000000Kb時,錯誤率都為0b,誤碼率滿足設(shè)計要求。

4 結(jié)語

該設(shè)計系統(tǒng)以Virtex-5為核心構(gòu)建的平臺,對AURORA協(xié)議下串行傳輸系統(tǒng)進(jìn)行了設(shè)計與實現(xiàn)。通過對核心問題的解決,將計算機(jī)與外部擴(kuò)展很好的結(jié)合,達(dá)到信號傳輸?shù)母咚佟⒎€(wěn)定的目的。實驗證明,板卡設(shè)計的整體思路和核心方法的解決是完備的,并使得板卡的傳輸速率和穩(wěn)定性的到了較大的提高。