PSRR是電路抑制來(lái)自于電源噪聲能力的量化術(shù)語(yǔ)。它被定義為輸入端到輸出端的增益與電源到輸出端增益的比值,即

放大器電路電源抑制比的方法" src="http://files.chinaaet.com/images/20110907/fc860af5-b3a8-43bc-a6c9-7f43398ddd8d.jpg" />

這里,A(s)=輸入端到輸出端的增益=Gm×Rout;Ap(s)=電源到輸出端的增益=GMp×Rout。因此

![]()

這里,Gm為輸入信號(hào)跨導(dǎo);GMp為電源跨導(dǎo)。

1 改善PSRR的方法

為減小電源波動(dòng)對(duì)輸出端的影響,Gm必須增加而GMp必須減小。理想情況下,要完全排除電源波動(dòng)的影響,就要使Gm無(wú)限大,而GMp為0。文中介紹了共源共柵技術(shù),負(fù)反饋技術(shù)和采用附加電路。3種改善放大器電路PSRR的方法,并進(jìn)行了仿真驗(yàn)證。

通過(guò)從VDD到輸出端能夠反方向影響電源波動(dòng)的負(fù)增益改善PSRR,從而反映到放大電路的輸出端。共源放大器為應(yīng)用這一技術(shù)提供了支撐,結(jié)果已被證實(shí)。

2 共源共柵技術(shù)

2.1 簡(jiǎn)介

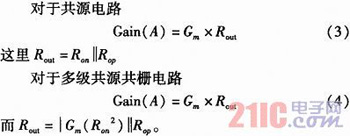

共源共柵技術(shù),盡管增加了放大器的輸出阻抗Rout,卻也極大地增加了放大器電路的增益。然而,從電源VDD到輸出端的增益仍然為1,與共源放大器相同。這樣,共源共柵技術(shù)改善了PSRR,由于它增加了輸入端到輸出端的增益,而保持電源到輸出端的增益為常數(shù)。

然而,和共源放大器相比,共源共柵也帶來(lái)了輸出擺幅和3 dB頻率點(diǎn)減小的不足。輸出擺幅減小是由于Vd輸出擺幅值要求較低。由于輸出能力增加,輸出端的頻率點(diǎn)左移而導(dǎo)致3dB頻率的減小。

2.2 電路

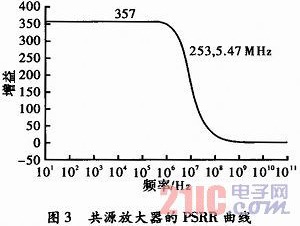

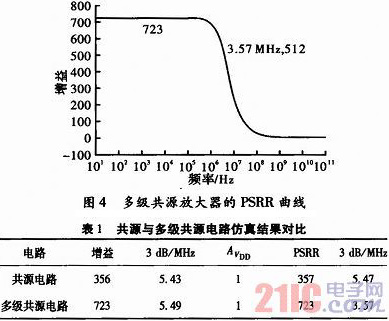

共源電路如圖1所示,它由一個(gè)PMOS管作為負(fù)載,以負(fù)載MOS管的偏置電路來(lái)估計(jì)放大器的PSRR。一個(gè)30μA的電流源被用做放大器的偏置。這個(gè)共源放大器的增益可以仿真到3dB頻率為5.43MHz8寸的356。由于電源端的增益AVDD為1,因此PSRR仍然為356。

多級(jí)共源放大器如圖2所示,它包括共源共柵NMOS晶體管M1和M2。這些晶體管的偏置電壓由鏡像電流源產(chǎn)生,并由M1分流。30μA的電流源被用來(lái)匹配共源放大器的偏置。盡管負(fù)載器件只包含單級(jí)MOS,沒(méi)有級(jí)聯(lián),但放大器的增益為722,是原來(lái)的2倍。然而,由于輸出阻抗增加,3dB點(diǎn)的頻率減小到3.57MHz。

2.3 仿真結(jié)果及輸出曲線

在共源電路里,可看到AVDD=1。這意味著波動(dòng)從電源VDD無(wú)衰減的傳遞到輸出端,由此發(fā)現(xiàn)PSRR=放大器的增益,因而為了增加電路的PSRR,這一技術(shù)更趨向于增加電路的增益。然而,該方法的主要不足在于其低的輸出擺幅,其應(yīng)用受到了頻率較低的限制,在高頻時(shí)PSRR較低。

3 負(fù)反饋技術(shù)

3.1 簡(jiǎn)介

由于負(fù)反饋保證了輸出端電壓跟隨輸入端電壓,穩(wěn)定了電路。且抑制了來(lái)自像電源等其它節(jié)點(diǎn)的干擾,并給出了較低的電源到輸出端的增益,因而改善了整個(gè)電路的PSRR。

3.2 電路

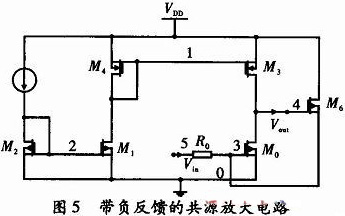

為構(gòu)建負(fù)反饋方法改善PSRR,對(duì)一種帶有負(fù)反饋的共源放大電路進(jìn)行了仿真,并與圖1中仿真的不帶負(fù)反饋的共源放大器進(jìn)行了比較。負(fù)反饋的電路如圖5所示,輸出電壓被采樣并控制M6,由M6的電流通過(guò)R0轉(zhuǎn)換為電壓,輸出電流及M0的輸入電流混合構(gòu)成。負(fù)載器件是PMOS管,其偏置電壓由一鏡像電路產(chǎn)生。在設(shè)計(jì)過(guò)程中,其電阻值是關(guān)鍵,因?yàn)樗鼪Q定著增益和PSRR值之間的平衡。電阻值過(guò)大會(huì)損失增益。

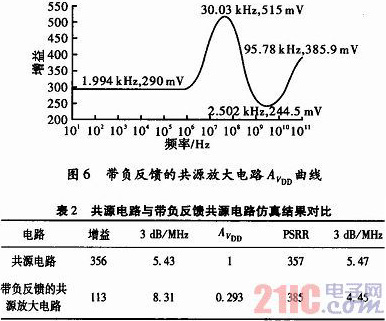

3.3 仿真結(jié)果及輸出曲線

在使用負(fù)反饋的電路中,AVDD值已減小到0.293。最后PSRR得已改善。負(fù)反饋把輸出電壓強(qiáng)加于輸入電壓,從而穩(wěn)定了電路。因此,它能抑制任何從其他節(jié)點(diǎn)像電源等的波動(dòng),即使只有很低的電源到輸出節(jié)點(diǎn)的增益值。因此使用其它方法像共源共射電路、增益提升等來(lái)增加這一電路的增益,應(yīng)用相同的反饋電路將極大地隨增益而改善電路的PSRR。

4 附加電路方法

4.1 簡(jiǎn)介

附加電路是為提供消除在正常電路中電源對(duì)輸出的影響,而搭建的從VDD到輸出的負(fù)增益通道作為設(shè)計(jì)目標(biāo)。由于負(fù)增益消除了VDD對(duì)輸出節(jié)點(diǎn)的影響,改善PSRR值的GMp減小了。

4.2 電路

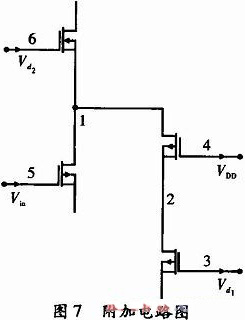

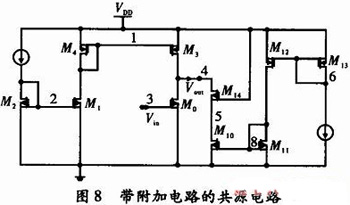

帶附加電路的共源電路如圖7和圖8所示,消除了使用工作以線性范圍內(nèi)的共源放大器,從VDD到輸出節(jié)點(diǎn)電源波動(dòng)的影響。

由于共源放大器為反相輸出,由M14放大后的VDD波動(dòng),明顯影響了經(jīng)過(guò)輸出節(jié)點(diǎn)晶體管M3的VDD波動(dòng)。附加電路法使增益和PSRR值達(dá)到了平衡。隨著增益的增加,PSRR值則減小。

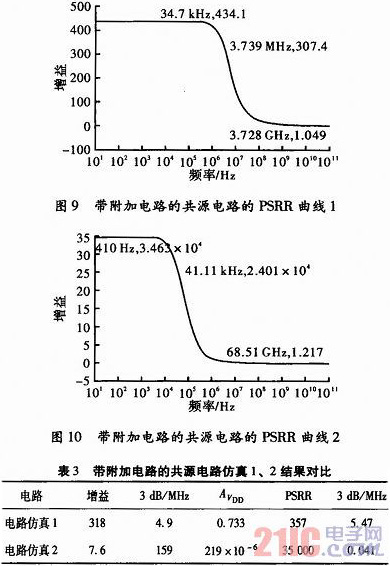

給出了兩種電路仿真如圖9和圖10所示,其中第一個(gè)工作在高增益下,相應(yīng)的PSRR較低。M14有電源電壓VDD提供門(mén)限電壓,使其有較高的Vgs值,導(dǎo)致其工作在線性區(qū)域。輸入晶體管M0工作在很高R0和跨導(dǎo)Gm的飽和區(qū)。因而M14也被驅(qū)動(dòng)工作在飽和區(qū),而增加了它的R0和Gm值,盡管它工作在線性區(qū)。結(jié)果發(fā)現(xiàn)此電路有很高的整體增益和AVDD值以及很低的PSRR。

在第2個(gè)仿真里,輸入晶體管M0工作在飽和區(qū),卻在線性區(qū)的邊緣。因此,晶體管M14和M10工作在較深的線性區(qū),減少M(fèi)14消耗的等效電阻Ra。結(jié)果,放大器的增益有所下降,同樣AVDD的值也會(huì)下降。最后,電路的PSRR徹底改善了整個(gè)放大器的增益,且能夠在第二級(jí)放大器中得到改善,并維持較高的PSRR值。

4.3 仿真結(jié)果及輸出曲線

通過(guò)使用消除電源波動(dòng)影響的附加電路,改善了PSRR。但由于輸出阻抗上附加電路的影響,整個(gè)電路的增益依然有待于改變。從上述結(jié)果看,整個(gè)電路將獲得一個(gè)增益與PSRR的平衡。

然而,這一電路的3dB頻率點(diǎn)與使用負(fù)反饋技術(shù)相比較低,盡管附加的MOSFET增加了輸出節(jié)點(diǎn)的負(fù)載電容,極點(diǎn)左移而3dB頻率變低。低增益和高PSRR放大器,能通過(guò)級(jí)連達(dá)到較高的增益。

5 結(jié)束語(yǔ)

盡管共源共柵技術(shù)同比率改善了電路的增益和PSRR,但它卻隨之帶來(lái)較低的輸出擺幅和3dB頻率點(diǎn)及較高的輸出阻抗,且不適于放大器的級(jí)聯(lián)和較高工作頻率等需求的應(yīng)用中。負(fù)反饋技術(shù)在改善放大器PSRR的同時(shí)又穩(wěn)定了輸出。盡管負(fù)反饋技術(shù)減少了從電源到輸出節(jié)點(diǎn)的增益,如AVDD,并且增益了PSRR。但增益是按比例減少,B值能夠被合理的調(diào)整以達(dá)到增益要求。這一技術(shù)對(duì)工作在高頻中的電路有效。附加電路則是能夠給出最大PSRR值的技術(shù),其結(jié)論能夠從3種技術(shù)的仿真數(shù)據(jù)輸出表里看出,并能維持較高的增益值。但它也有減小電路3dB頻率點(diǎn)的不足,因?yàn)樵谳敵龆艘M(jìn)了附加電容。因此,如表3中的電路2可以看到,這一電路能夠達(dá)到極高的PSRR值,卻是以很低的增益為代價(jià)。因此,該電路在設(shè)計(jì)含級(jí)聯(lián)放大器電路的設(shè)計(jì)中有重要作用,這里增益可通過(guò)級(jí)聯(lián)解決。附加電路能夠滿足電源波動(dòng)穩(wěn)定性的需求。