關(guān)鍵字:FPGA 1553B總線

MIL-STD-1553 總線是美國(guó)20 世紀(jì)80 年代制定的第一個(gè)軍用數(shù)據(jù)總線標(biāo)準(zhǔn), 它是一種串行的數(shù)據(jù)總線。

該總線標(biāo)準(zhǔn)自制定后廣泛應(yīng)用于軍用飛機(jī)、車(chē)輛、船舶中, 并鑒于其高可靠性和靈活性, 逐漸應(yīng)用在許多其他機(jī)動(dòng)平臺(tái)上。

1553B 是一種時(shí)分制指令/響應(yīng)式多路傳輸數(shù)據(jù)總線, 總線上的所有消息傳輸都由總線控制器發(fā)起, 遠(yuǎn)程終端對(duì)發(fā)出的指令應(yīng)給予回答( 響應(yīng)) 并執(zhí)行相關(guān)操作。

這種方式非常適合集中控制的分布式處理系統(tǒng)。1553B總線通信系統(tǒng)是由總線控制器、遠(yuǎn)程終端、總線監(jiān)控器三部分組成。一個(gè)通信總線上最多可以掛32 個(gè)遠(yuǎn)程終端, 傳輸介質(zhì)采用屏蔽雙絞線, 對(duì)噪聲等干擾有很好的抑制能力。1553B 總線的數(shù)據(jù)傳輸率為1 Mb/s ,在一次消息傳輸中最多可以傳送32 個(gè)字, 所有單次傳輸?shù)臅r(shí)間較短, 具有很好的實(shí)時(shí)性。

在MIL-STD-1553 總線通信系統(tǒng)中, 總線接口板是系統(tǒng)的關(guān)鍵部分, 其中核心部分的接口電路是總線應(yīng)用中的主要制約因素。在1553B 總線得到廣泛應(yīng)用的今天, 國(guó)內(nèi)應(yīng)用1553B 總線協(xié)議的通信模塊的解決方案多采取基于進(jìn)口1553B 總線協(xié)議芯片來(lái)開(kāi)展相關(guān)設(shè)計(jì), 如UT 公司的UTl553B 協(xié)議芯片、DDC 公司的高級(jí)協(xié)議處理芯片BU-61580 等, 雖然這些芯片能夠完成協(xié)議功能, 但價(jià)格昂貴、靈活性差, 這些弱點(diǎn)在一定程度上限制了設(shè)計(jì)能力, 因此提出一種新的基于嵌入式方法實(shí)現(xiàn)的1553B 數(shù)據(jù)總線接口邏輯。

1 系統(tǒng)總體設(shè)計(jì)方案

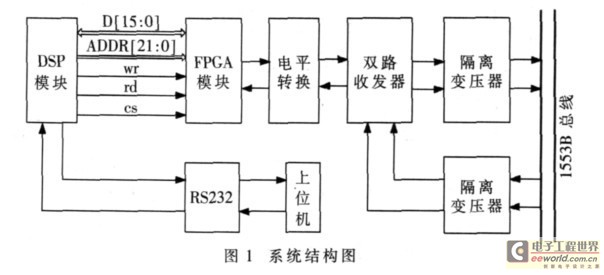

本文采用Xilinx 公司的FPGA 芯片作為協(xié)議處理核心器件, 選用TI 公司的TMS320C5510 作為主處理器負(fù)責(zé)接收FPGA 處理過(guò)的數(shù)據(jù)和調(diào)度FPGA 的具體操作。

總體方案的系統(tǒng)結(jié)構(gòu)如圖1 所示。

1.1 模擬收發(fā)部分電路設(shè)計(jì)

由于1553B 總線上傳輸?shù)氖请p極性的差分信號(hào), 主處理器不能直接接收來(lái)自總線上的數(shù)據(jù), 所以需要信號(hào)調(diào)制解調(diào)及電平轉(zhuǎn)換電路。

電平轉(zhuǎn)換部分一方面將總線上傳輸?shù)碾娖叫盘?hào)轉(zhuǎn)換成標(biāo)準(zhǔn)的CMOS 電平供處理器使用, 另一方面將處理器發(fā)出的CMOS 信號(hào)變成總線標(biāo)準(zhǔn)進(jìn)行傳輸。模擬收發(fā)器部分簡(jiǎn)單地說(shuō)就是將單極性曼徹斯特編碼和雙極性曼徹斯特編碼相互轉(zhuǎn)換。本文采用HOLT 公司的HI -1567PSI , 它是一款專(zhuān)門(mén)為MIL-STD-1553 開(kāi)發(fā)的模擬收發(fā)器, 供電電壓為3.3 V, 通過(guò)隔離變壓器連接到總線上。HI-1567PSI 是雙通道收發(fā)器結(jié)構(gòu), 因此要有兩個(gè)隔離變壓器與其相連接。

1.2 總線接口的數(shù)字通信部分

數(shù)字通信部分是1553B 總線接口模塊的核心, 完成協(xié)議數(shù)據(jù)的收發(fā)處理, 由可編程邏輯器件Virtex 系列芯片和DSP 芯片組成。FPGA 芯片在模塊中起到1553B 通道的作用, 接收總線上送來(lái)的數(shù)據(jù)并根據(jù)協(xié)議進(jìn)行處理之后送給處理器。FPGA 模塊中開(kāi)辟了足夠空間的FIFO存儲(chǔ)處理后的數(shù)據(jù), 當(dāng)達(dá)到一定數(shù)量后, 主處理器采用中斷的方式讀取FIFO 中的數(shù)據(jù)。在本文的設(shè)計(jì)中, 為了便于觀察實(shí)驗(yàn)結(jié)果, 將DSP 接收到的數(shù)據(jù)送到串口上進(jìn)行顯示。同樣地,DSP 將要發(fā)送的數(shù)據(jù)送到FPGA 開(kāi)辟的另一個(gè)FIFO 中, 當(dāng)每個(gè)數(shù)據(jù)編碼結(jié)束后通過(guò)狀態(tài)機(jī)程序產(chǎn)生FIFO 信號(hào)的時(shí)鐘讀取下一個(gè)數(shù)據(jù)進(jìn)行編碼,所以這里的FIFO 采用的是異步的工作方式。

2 核心模塊功能分析

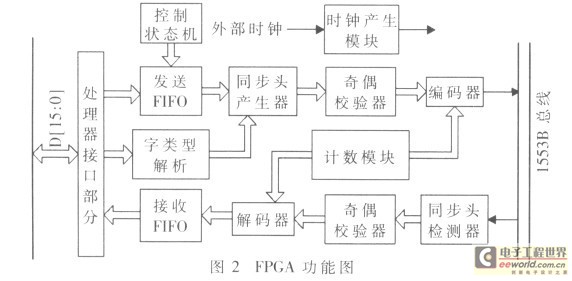

總線接口模塊最主要的部分是FPGA 實(shí)現(xiàn)的功能,其總體功能如圖2 所示。

FPGA 中最重要的部分是發(fā)送器和接收器, 現(xiàn)將這兩部分的工作過(guò)程做簡(jiǎn)要分析。

2.1 數(shù)字發(fā)送器

(1)DSP 將要發(fā)送的數(shù)據(jù)依次送到發(fā)送FIFO 中進(jìn)行存儲(chǔ), 硬件將根據(jù)狀態(tài)機(jī)運(yùn)行情況產(chǎn)生FIFO 讀時(shí)鐘讀取數(shù)據(jù)并送到同步頭產(chǎn)生器。

(2)根據(jù)要發(fā)送的是狀態(tài)/命令字或數(shù)據(jù)字在同步頭產(chǎn)生器中加上相應(yīng)的同步頭, 若是狀態(tài)/命令字則在有效數(shù)據(jù)前加上3 個(gè)二進(jìn)制位, 先正后負(fù), 正負(fù)電平各占1.5 bit , 數(shù)據(jù)字則相反。

(3) 奇偶校驗(yàn)器通過(guò)將有效數(shù)據(jù)位的各位進(jìn)行異或即可實(shí)現(xiàn)。

(4 ) 硬件將經(jīng)過(guò)奇偶校驗(yàn)器的數(shù)據(jù)送到曼徹斯特編碼器進(jìn)行編碼, 編碼器的實(shí)現(xiàn)相對(duì)較簡(jiǎn)單。編碼時(shí)鐘采用2 MHz , 有效數(shù)據(jù)位和奇偶校驗(yàn)位都采用曼徹斯特碼的形式發(fā)送, 加上同步頭共40 bit 二進(jìn)制位, 使用2 MHz的時(shí)鐘發(fā)送到1553B 數(shù)據(jù)總線上。

在數(shù)字發(fā)送部分控制狀態(tài)機(jī)是保證時(shí)序的關(guān)鍵所在, 狀態(tài)機(jī)不僅控制發(fā)送FIFO 的時(shí)鐘, 同時(shí)也有效地輸出編碼的觸發(fā)信號(hào)。狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)移如圖3 所示。

2.2 數(shù)字接收器

(1)FPGA 將經(jīng)過(guò)模擬電路后的單極性曼徹斯特碼送到同步頭檢測(cè)器, 提取同步頭后進(jìn)行奇偶校驗(yàn), 然后再送到解碼器。

(2) 解碼器采用8 MHz 的時(shí)鐘進(jìn)行采樣, 由于曼徹斯特編碼在時(shí)鐘的中間時(shí)刻有電平的跳變, 所以在采樣到跳變沿的下一個(gè)時(shí)鐘將采樣到的數(shù)據(jù)取反就得到二進(jìn)制碼。同時(shí), 當(dāng)計(jì)數(shù)器計(jì)數(shù)到132 時(shí)對(duì)一個(gè)有效數(shù)據(jù)字解碼結(jié)束產(chǎn)生使能信號(hào)停止采樣, 將17 bit 二進(jìn)制數(shù)放到移位寄存器中實(shí)現(xiàn)串并轉(zhuǎn)換。

(3) 解碼器在解碼完一個(gè)數(shù)據(jù)后會(huì)產(chǎn)生接收FIFO的時(shí)鐘信號(hào), 將數(shù)據(jù)送到接收FIFO 中, 當(dāng)FIFO 中達(dá)到可編程滿(mǎn)設(shè)定的數(shù)據(jù)后便產(chǎn)生中斷信號(hào), 通知DSP 將數(shù)據(jù)讀走。

3 功能仿真及試驗(yàn)結(jié)果分析

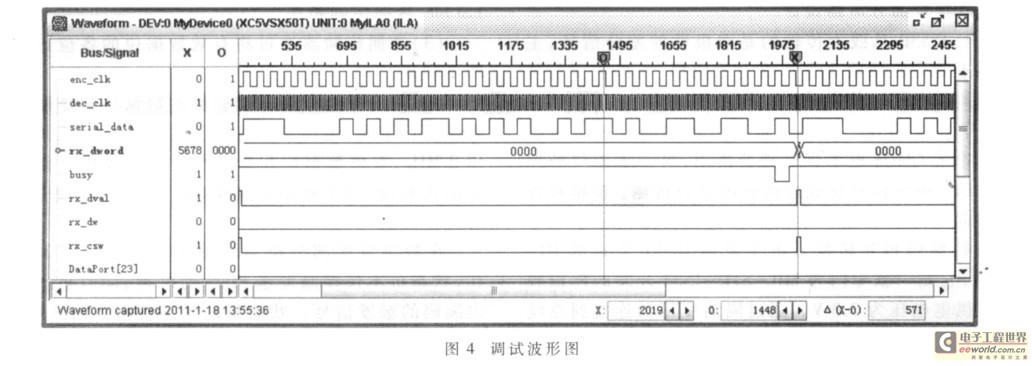

在研究分析了1553B 總線接口模塊的功能及系統(tǒng)設(shè)計(jì)后, 在實(shí)驗(yàn)室經(jīng)過(guò)PCB 設(shè)計(jì)投產(chǎn)了兩塊板卡, 搭建了實(shí)驗(yàn)平臺(tái)并進(jìn)行功能驗(yàn)證。由于實(shí)驗(yàn)室條件有限,功能驗(yàn)證的設(shè)計(jì)流程是將發(fā)送模塊DSP 發(fā)送的數(shù)據(jù)經(jīng)過(guò)FPGA 處理, 得到曼徹斯特編碼, 并經(jīng)過(guò)模擬收發(fā)器、耦合變壓器后連接到接收模塊的輸入端, 信號(hào)經(jīng)過(guò)模擬電路部分送到FPGA 解碼后送給DSP 處理。

在總線接口模塊中, 曼徹斯特編解碼是實(shí)現(xiàn)功能的核心部分, 所以編碼數(shù)據(jù)和解碼數(shù)據(jù)是進(jìn)行功能驗(yàn)證時(shí)觀察的重點(diǎn)。為了觀察曼徹斯特編解碼是否正確, 這里采用Xilinx 的Chip Scope 邏輯分析儀觀察數(shù)據(jù),serial_data 是發(fā)送模塊經(jīng)過(guò)編碼部分處理后的串行數(shù)據(jù),rx_dword 是接收模塊中經(jīng)過(guò)解碼部分得到的16 bit 數(shù)據(jù), 對(duì)比這兩個(gè)數(shù)據(jù)的波形是否滿(mǎn)足曼徹斯特編碼標(biāo)準(zhǔn)即可驗(yàn)證設(shè)計(jì)的準(zhǔn)確性, 用Chip Scope 捕捉到的波形如圖4 所示。

從上面的波形圖中可以看到, busy 信號(hào)在編碼的過(guò)程中一直為高電平, 在編碼結(jié)束后的一個(gè)編碼時(shí)鐘周期內(nèi)為低電平。rx_dval 信號(hào)在解碼結(jié)束的一個(gè)解碼時(shí)鐘周期內(nèi)為高電平, 說(shuō)明此時(shí)解碼結(jié)束, 接收到的數(shù)據(jù)rx_dword 為5 678,對(duì)比發(fā)送的數(shù)據(jù)和編碼數(shù)據(jù)serial_data,說(shuō)明編解碼均正確。

同時(shí), 為了觀察DSP 發(fā)送的數(shù)據(jù)與接收模塊DSP 接收的數(shù)據(jù)是否正確, 提高測(cè)試數(shù)據(jù)的直觀性, 在這里加上串口調(diào)試助手, 通過(guò)RS232 總線傳輸接收數(shù)據(jù), 于PC機(jī)平臺(tái)上運(yùn)行串口調(diào)試助手觀察接收數(shù)據(jù)。

在分析了1553B 總線接口模塊的功能后介紹了總線接口部分的FPGA 系統(tǒng)設(shè)計(jì), 在搭建的平臺(tái)上進(jìn)行了功能驗(yàn)證, 實(shí)驗(yàn)過(guò)程中獲得的數(shù)據(jù)表明了論文中設(shè)計(jì)的接口模塊的功能達(dá)到了預(yù)期目標(biāo)要求。