王文萱,翟正軍

(西北工業(yè)大學(xué) 計算機學(xué)院,陜西 西安 710129)

摘要:1553B總線在航空、航天、艦船等嵌入式高可靠實時通信領(lǐng)域占有重要地位。分析了1553B總線終端的組成,歸納比較了DDC公司研制的多款1553B總線處理器的發(fā)展變化的特征,應(yīng)用該公司集成度最高的1553B總線處理器,設(shè)計了小型化的1553B總線終端,與采用集成度較低的1553B處理器完成的設(shè)計方案進行了比較。結(jié)果表明,所設(shè)計的終端在體積、功耗、重量方面降幅均超過60%。

關(guān)鍵詞: 1553B總線;總線終端;通信處理器

0引言

數(shù)字式時分制指令響應(yīng)型多路傳輸總線1553B標(biāo)準(zhǔn)最初是由美國為研制聯(lián)合式航空電子系統(tǒng)制定的通信標(biāo)準(zhǔn)。由于1553B總線在航電系統(tǒng)上的應(yīng)用大大提高了飛機的性能,因而逐步擴展到艦船、航天等高可靠通信領(lǐng)域。雖然1553B總線已發(fā)展應(yīng)用了30年,但由于1553B總線具有集中控制簡單、實時響應(yīng)、容錯可靠、便于維護、技術(shù)成熟等優(yōu)勢,因此在航空、航天、艦船等嵌入式高可靠實時領(lǐng)域1553B總線依然占有重要的地位。以最新型的歐洲寬體客機A350XWB為例,在機載局域網(wǎng)中采用了1553B總線實現(xiàn)聯(lián)網(wǎng)通信。

嵌入式高可靠實時系統(tǒng)功能與性能發(fā)展的同時,對系統(tǒng)的體積、功耗、重量等要求也愈來愈高,在基于1553B總線互聯(lián)的系統(tǒng)中,每個設(shè)備都需要1553B終端才能接入到總線中,因此1553B總線終端在系統(tǒng)中占有相當(dāng)?shù)谋戎亍T跐M足系統(tǒng)通信要求下,降低1553B總線終端的設(shè)計復(fù)雜度,減少體積、功耗、重量,成為1553B終端設(shè)計人員的一項重要的追求目標(biāo)。

美國數(shù)字設(shè)備公司(DDC)[1]在1553B總線器件研發(fā)、制造及應(yīng)用方面占有重要的地位,本文以其不斷推新發(fā)展的1553B總線處理器芯片為研究對象,分析歸納了DDC公司將原來與1553B終端實現(xiàn)相關(guān)的外圍器件不斷集成到1553B總線通信處理器中,而且不斷擴展1553B總線通信處理器內(nèi)部可編程能力的趨勢,使讀者了解1553B總線通信處理器功能不斷增強、集成度不斷提高的特點,為設(shè)計人員選擇合適的1553B總線通信處理器提供參考,以滿足系統(tǒng)1553B總線功能要求的同時,也能滿足對1553B總線終端的體積、功耗、重量的指標(biāo)約束條件。

11553B總線終端構(gòu)成

1553B總線傳輸速率為1 Mb/s,傳輸媒介為屏蔽雙絞線,可接入32個終端,終端共有三種類型:總線控制器(Bus Controller,BC)、遠程終端(Remote Terminal,RT)和總線監(jiān)視器(Bus Monitor,BM)。BC是總線上唯一能組織數(shù)據(jù)消息傳輸?shù)慕K端;RT是接受總線上BC控制,完成消息發(fā)送或接收的終端;BM是接收總線上消息并能有選擇記錄的終端,其僅“監(jiān)控”總線上信息傳輸?shù)粎⑴c總線的通信。在嵌入式高可靠實時系統(tǒng)中,1553B總線為雙余度拓撲結(jié)構(gòu),所有1553B總線終端設(shè)備通過變壓器耦合方式掛接在總線網(wǎng)絡(luò)上[2]。

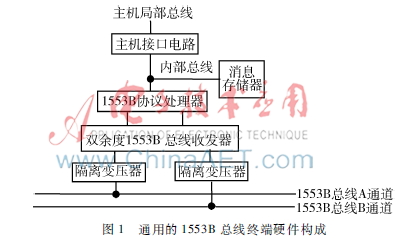

采用變壓器耦合方式的1553B總線終端硬件包括:主機接口電路、消息存儲器、1553B協(xié)議處理器、雙余度總線收發(fā)器和隔離變壓器。通用的1553B總線終端硬件構(gòu)成如圖1所示。

主機接口電路、實現(xiàn)主機地址、數(shù)據(jù)及控制總線到終端內(nèi)部總線的緩沖隔離及控制。消息存儲器支持主機與終端內(nèi)部1553B協(xié)議處理器對1553B總線消息數(shù)據(jù)的存儲、讀寫訪問,需要設(shè)計消息存儲器共享互斥訪問控制電路,以達到兩者可正確訪問。

1553B協(xié)議處理器按照1553B協(xié)議要求,首先完成1553B的ManchesterⅡ碼編譯碼、數(shù)據(jù)串并轉(zhuǎn)換與并串轉(zhuǎn)換、數(shù)據(jù)字同步頭的產(chǎn)生與檢測、奇校驗;其次根據(jù)主機規(guī)定,作為BC、RT或BM完成總線傳輸中的任務(wù)。作為BC,組織消息的發(fā)送與正確性判斷;作為RT,完成對指令字的識別、狀態(tài)字的自動響應(yīng);作為BM,完成對所有或部分要求監(jiān)控的消息監(jiān)控并記錄。1553B協(xié)議處理器是終端的控制核心,不僅要訪問消息存儲器完成1553B消息數(shù)據(jù)的收發(fā)及相應(yīng)狀態(tài)的修改,而且要與雙余度1553B總線收發(fā)器連接,將串行數(shù)據(jù)發(fā)送到發(fā)送器或從接收器接收串行數(shù)據(jù),還要提供主機可編程接口能力,由主機控制終端的角色、運行或讀取終端的實時狀態(tài),在主機通信軟件管理下完成1553B總線傳輸任務(wù)。雙余度1553B總線收發(fā)器能夠?qū)TL電平的串行Manchester碼與雙極性的Manchester碼相互轉(zhuǎn)化。兩路隔離變壓器,源端與雙余度1553B總線收發(fā)器連接,次端與1553B總線的兩條主電纜耦合器分別相連。

21553B通信處理器的變化分析與比較

從上面1553B總線終端構(gòu)成可見,為完成1553B總線通信任務(wù),需要至少五部分功能單元電路。

在2000年前,1553B總線生產(chǎn)廠家如UTMC、NHI等公司的1553B協(xié)議處理器、總線收發(fā)器、變壓器等均是獨立的器件,因此設(shè)計1553B總線終端需要十多個元器件,硬件模塊體積大、重量重、功耗大。

DDC公司首先認識到集成的必要性和發(fā)展趨勢,于1995年推出了集成度大幅度提高的1553B先進通信引擎(ACE)器件[3],是高集成度的1553B總線通信處理器。 ACE單一器件包含了子系統(tǒng)(設(shè)備)主機接口隔離電路、消息存儲器、1553B協(xié)議處理器、雙余度總線收發(fā)器,實現(xiàn)的主要功能包括:

(1)BC/RT/BM協(xié)議一體化設(shè)計,由軟件配置工作角色;

(2)主處理器接口,靈活多樣,支持8/16 bit模式,可零等待或插入等待;

(3)消息存儲器,64 KB RAM,包含主機與內(nèi)部協(xié)議訪問的互斥訪問控制;

(4)內(nèi)置雙余度總線收發(fā)器,單5 V供電;

(5)增強BC功能的特征:支持自動重試、可編程間隔時間、幀自動重復(fù)、可編程響應(yīng)超時時間;

(6)增強RT功能的特征:可編程命令非法化表,可選擇單消息緩沖、雙緩沖、環(huán)形緩沖和全局環(huán)形緩沖,獨立的方式命令中斷,可根據(jù)子地址進行忙位編程;

(7)增強BM功能的特征:選擇消息監(jiān)控特征,提供可編程觸發(fā)選項。

隨著半導(dǎo)體微電子工藝水平的發(fā)展和提高,在對1553B終端設(shè)計要求不斷提高的外界需求推動下, 以ACE為基礎(chǔ),通過集成外部器件提高集成度、改變封裝縮小體積、增強內(nèi)部新的功能擴展通用性等措施,DDC公司在1999年、2004年、2011年和2013年分別推出了MiniACE、MicroACE、TotalACE、TotalACEXtreme四款產(chǎn)品。下面分別說明這四款典型處理器的主要特點。

(1)MiniACE將ACE的DIP封裝改為“Flat Pack”封裝,體積壓縮為25.4 mm×25.4 mm×3.3 mm。相比ACE僅有的CPU局部總線接口,擴展提供了一種PCI總線的接口,為1553B終端作為PCI總線的從設(shè)備提供了無縫連接。但需要外接兩個隔離變壓器。(2)MicroACE在MiniACE基礎(chǔ)上,不僅增強了BC的編程能力,包括十余種總線表判定、分支、循環(huán)操作碼等,方便了用戶對總線的控制,而且改為BGA封裝,體積壓縮到20.7 mm×20.7 mm×3.3 mm。提供CPU局部總線接口或PCI總線接口。需要外接兩個隔離變壓器。(3)TotalACE在MicroACE之上,內(nèi)部集成了兩個隔離變壓器,是BGA封裝,體積為27.9 mm×15.2 mm×4.7 mm,也提供CPU局部總線接口或PCI總線接口。不需要外接兩個隔離變壓器。(4)TotalACEXtreme在TotalACE基礎(chǔ)上,增強了能同時做多個RT的功能。采用更小的BGA封裝,體積縮小為16 mm×16 mm×4.7 mm;提供CPU局部總線接口或PCI總線接口。不需要外接兩個隔離變壓器。

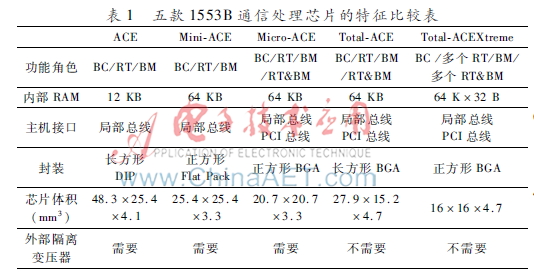

總結(jié)DDC公司以上五款1553B通信處理芯片的特征,比較如表1所示。

31553B總線終端設(shè)計

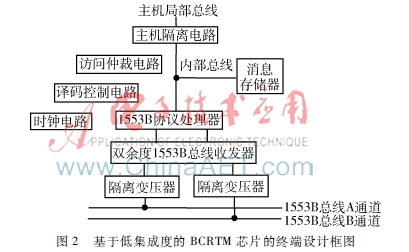

采用UTMC公司低集成度1553B協(xié)議處理芯片BCRTM為核心器件[45],需要增加外部存儲器、雙余度收發(fā)器、兩個隔離變壓器、主機接口隔離電路、仲裁電路、譯碼電路、時鐘電路等,需要至少10多個功能器件,才能實現(xiàn)一個1553B總線終端,如圖2所示。

圖2基于低集成度的BCRTM芯片的終端設(shè)計框圖

而采用最新的Total-ACEXtreme高集成度芯片[6],因其內(nèi)部集成了絕大多數(shù)電路,只需要再增加時鐘、簡單的主機接口訪問譯碼電路即可構(gòu)建一個比UT1553B BCRTM方案功能更全(支持多個RT同時工作、RT&BM模式等功能)的1553B總線終端,如圖3所示。

圖3基于高集成度TotalACEXtreme的終端設(shè)計框圖對比采用集成度較低的UT1553B BCRTM芯片與采用集成度最高的TotalACEXtreme芯片構(gòu)建1553B總線終端的兩種設(shè)計方案,后者占用電路板的面積節(jié)省了70%,重量減輕約60%,功耗降低約60%,因而大大降低了1553B總線終端的體積、功耗、重量,為系統(tǒng)設(shè)計節(jié)省了寶貴的資源。

4結(jié)論

本文介紹了1553B總線終端的功能單元構(gòu)成,通過分析DDC公司推出的五款1553B總線處理器的技術(shù)特征和發(fā)展趨勢,說明隨著集成電路水平的提高,1553B總線通信處理器集成的功能電路數(shù)量不斷增加、完成的功能愈來愈強大、體積越來越小;同時與主設(shè)備的接口趨向簡單化、服務(wù)趨向透明化,從而為1553B設(shè)計人員降低1553B總線終端硬件設(shè)計復(fù)雜度,減少體積、功耗與重量的目標(biāo)奠定了基礎(chǔ)。

參考文獻

[1] MILSTD1553B Designer′s Guide[Z].Data Device Corporation.

[2] 張浩.嵌入式1553B總線通信卡的設(shè)計與研究[D].南京:南京理工大學(xué),2008.

[3] BU65170/61580 Advanced Communication Engine (ACE) Data Sheet[Z]. Data Device Corporation.

[4] UT1553B BCRTM manual[Z]. United Technology MicroElectrical Corporation.

[5] 劉士全,黃正,蔡潔明,等.1553B總線應(yīng)用競爭訪問時序分析[J].微型機與應(yīng)用,2015,34(1):6971.

[6] TotalAceXtremeTM BU67301B Data Sheet[Z]. Data Device Corporation.