潘濱,周昕杰,羅靜

(中國電子科技集團(tuán)公司第五十八研究所, 江蘇 無錫 214062)

摘要:研究設(shè)計(jì)了一種多節(jié)點(diǎn)的1553B總線協(xié)議處理器,可以模擬整套1553B總線系統(tǒng),既可以作為測(cè)試設(shè)備,也可作為總線上的多個(gè)節(jié)點(diǎn)在實(shí)際應(yīng)用中使用。針對(duì)總線協(xié)議處理器邏輯與存儲(chǔ)資源占用高、難以單片實(shí)現(xiàn)的問題,提出了多核MIMD架構(gòu)的實(shí)現(xiàn)思路,有效地降低了邏輯資源的使用量,使其可以在單片FPGA上實(shí)現(xiàn)。基于軟硬件融合的理念,通過自定義專用指令集增加指令并行度來提高指令執(zhí)行的效率,增強(qiáng)了系統(tǒng)的實(shí)時(shí)性,使其可以在低頻時(shí)鐘下運(yùn)行,從而降低了系統(tǒng)的功耗。

關(guān)鍵詞:1553B總線;多核;MIMD;FPGA

0引言

1553B總線是一種廣泛應(yīng)用的軍用總線,它具有異步操作、時(shí)鐘自對(duì)準(zhǔn)、數(shù)據(jù)傳輸可靠性高等優(yōu)點(diǎn)[1]。目前,國內(nèi)科研院所已經(jīng)完成了總線協(xié)議處理器的國產(chǎn)化,成功研制了多款單節(jié)點(diǎn)總線協(xié)議處理器。但在用于部分特殊應(yīng)用和總線測(cè)試系統(tǒng)的多節(jié)點(diǎn)協(xié)議處理器方面,國內(nèi)尚未有相關(guān)的研究文獻(xiàn)。這一方面由于相比單節(jié)點(diǎn)處理器,多節(jié)點(diǎn)處理器需求量不大;另一方面由于多節(jié)點(diǎn)處理器需要的邏輯與存儲(chǔ)資源遠(yuǎn)高于單節(jié)點(diǎn)處理器,實(shí)現(xiàn)難度很大,國外同類產(chǎn)品也多是以較大規(guī)模的板卡形式實(shí)現(xiàn),而未能將其集成到單片中[2]。

隨著集成電路國產(chǎn)化的范圍日益擴(kuò)大,研制一種單片/單板實(shí)現(xiàn)的多節(jié)點(diǎn)協(xié)議處理器是必然要求。本文將以一種多核MIMD(多指令多數(shù)據(jù))的架構(gòu)在單片F(xiàn)PGA上實(shí)現(xiàn)多節(jié)點(diǎn)總線協(xié)議處理器,這一設(shè)計(jì)思路也可以轉(zhuǎn)換到ASIC設(shè)計(jì)上。

1總體思路

研究以DDC公司的BU61580型總線協(xié)議處理器作為參考范本,功能上實(shí)現(xiàn)1個(gè)總線控制器、31個(gè)總線終端、1個(gè)總線監(jiān)視器。設(shè)計(jì)為在外部接口時(shí)序上與BU61580兼容,以方便現(xiàn)有軟件的移植。

1553B總線協(xié)議處理器可以分為邏輯和存儲(chǔ)兩大核心部分[3]。1553B總線的設(shè)計(jì)緊貼應(yīng)用,功能繁雜,邏輯資源使用量較大。同時(shí),總線上每個(gè)節(jié)點(diǎn)至少4 K字的存儲(chǔ)容量需要大量的存儲(chǔ)資源。若采用單節(jié)點(diǎn)協(xié)議處理器復(fù)制32份的方式來實(shí)現(xiàn),勢(shì)必耗費(fèi)大量資源。這就要求設(shè)計(jì)一種高效簡潔的架構(gòu),最大程度地復(fù)用相似邏輯來減少資源占用。

通過分析總線的事務(wù)和總線各節(jié)點(diǎn)的行為模型,發(fā)現(xiàn)這樣兩個(gè)特性:(1)相比于協(xié)議處理器的速度,總線上的數(shù)據(jù)傳輸速率是很慢的,即使依次處理各節(jié)點(diǎn),也不會(huì)影響總線事務(wù)的正常運(yùn)行;(2)不同的節(jié)點(diǎn),在對(duì)總線事務(wù)的處理上,處理的過程基本是相同的,區(qū)別僅在于配置寄存器的不同配置值而產(chǎn)生的細(xì)小差異。若采用微控制器來執(zhí)行指令實(shí)現(xiàn)總線上的事務(wù)處理功能,就可以復(fù)用大部分的邏輯資源,而對(duì)于每個(gè)節(jié)點(diǎn)的不同配置而產(chǎn)生的細(xì)節(jié)差異,可以用SFR(特殊功能寄存器)的方式實(shí)現(xiàn)[4]。這樣,既達(dá)到了壓縮邏輯規(guī)模的目的,又保證了不同節(jié)點(diǎn)獨(dú)立配置的能力。

2架構(gòu)設(shè)計(jì)

在架構(gòu)設(shè)計(jì)中,重點(diǎn)關(guān)注簡潔性和實(shí)時(shí)性。簡潔的架構(gòu)能夠減少資源的使用量,提高代碼的可維護(hù)性。實(shí)時(shí)性能夠盡可能高效快速地完成總線事務(wù),從而實(shí)現(xiàn)更高的性能。

2.1MIMD指令集設(shè)計(jì)

首先考慮微控制器核的指令集的設(shè)計(jì)。將原本并行運(yùn)行的硬邏輯功能改為串行執(zhí)行的指令,一個(gè)重要的問題就是保證系統(tǒng)的實(shí)時(shí)性。

一種思路是采用常規(guī)指令集并使用流水線實(shí)現(xiàn)微控制器,這樣在一個(gè)周期內(nèi)能夠執(zhí)行更多的指令。但這只是提高了指令執(zhí)行的速度,并不能改變串行的本質(zhì),而且在協(xié)議處理器中,微控制器不應(yīng)該是最復(fù)雜的部分,調(diào)試工作的重點(diǎn)應(yīng)該放在與協(xié)議密切相關(guān)的具體功能模塊上,流水線的控制邏輯復(fù)雜,容易引入bug干擾其他模塊的調(diào)試,這會(huì)給設(shè)計(jì)工作帶來很大不便。

另一個(gè)思路是采用MIMD(多指令多數(shù)據(jù))架構(gòu)。在每個(gè)周期內(nèi),同時(shí)執(zhí)行多條指令,處理多個(gè)數(shù)據(jù),這是在事務(wù)層面的并行化,通過分配指令位域,在一條指令中實(shí)現(xiàn)多個(gè)不同的功能,可以大大提高指令執(zhí)行的效率,增強(qiáng)系統(tǒng)的性能。

將32 bit寬度的指令分為4個(gè)位域,分別是通用指令I(lǐng)NS、特殊功能寄存器指令SFRINS、擴(kuò)展指令EXT和條件判斷碼COND。通用指令是微控制器的指令,完成總線事務(wù)的基本操作;特殊功能寄存器指令針對(duì)總線協(xié)議處理器中的寄存器設(shè)計(jì),實(shí)現(xiàn)與總線事務(wù)處理流程無關(guān)但與處理細(xì)節(jié)相關(guān)的功能;擴(kuò)展指令用于實(shí)現(xiàn)地址的重映射和設(shè)備的選擇;將需要多步邏輯運(yùn)算才能得到結(jié)果的條件判斷通過硬邏輯實(shí)現(xiàn),供程序根據(jù)條件是否成立來選擇是否執(zhí)行該條指令。圖1給出了指令編碼的位域定義。

根據(jù)編碼原則,定制了一套專用指令集,能夠最好地適用于總線事務(wù)的處理。這套指令集可以在一個(gè)周期內(nèi)實(shí)現(xiàn)常規(guī)指令多個(gè)周期才能完成的功能,大大地提高了實(shí)時(shí)性。為便于軟件設(shè)計(jì)與調(diào)試,使用Perl語言編寫了該指令集的匯編器。

2.2硬件模塊運(yùn)行機(jī)制

硬件采用Verilog HDL設(shè)計(jì)實(shí)現(xiàn),在設(shè)計(jì)中注重了代碼的模塊化和可升級(jí)化。秉承高內(nèi)聚、低耦合的原則,將可以獨(dú)立出來的功能都盡可能獨(dú)立設(shè)計(jì)為一個(gè)模塊,這樣既有益于設(shè)計(jì)過程中的調(diào)試,也方便日后的維護(hù)與升級(jí)。圖2展示了多節(jié)點(diǎn)總線協(xié)議控制器的基本架構(gòu)框圖。

控制器由BC_ACE、RT_ACE、BM_ACE、BUS_INTF和CTRL_INTF共五個(gè)模塊組成。BC_ACE、RT_ACE、BM_ACE分別實(shí)現(xiàn)BC(總線控制器)、RT(遠(yuǎn)程終端)、BM(總線監(jiān)視器)的功能,BUS_INTF實(shí)現(xiàn)了三個(gè)協(xié)議處理模塊與1553B總線之間的接口,CTRL_INTF實(shí)現(xiàn)了多節(jié)點(diǎn)總線協(xié)議控制器和上位機(jī)之間的接口。

下面詳細(xì)介紹各模塊的運(yùn)行機(jī)制。

BC_ACE包含微控制器、指令存儲(chǔ)器、通用寄存器、特殊功能寄存器組和數(shù)據(jù)存儲(chǔ)器。微控制器從指令存儲(chǔ)器中讀取指令并執(zhí)行,完成SFR的配置與更新、數(shù)據(jù)存儲(chǔ)器的訪問等任務(wù)。同時(shí),微控制器將SFRINS發(fā)送到特殊功能寄存器組中,由SFR內(nèi)部邏輯完成總線數(shù)據(jù)收發(fā)和部分寄存器值的更新。

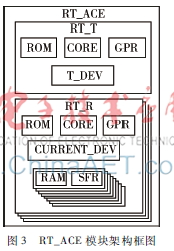

RT_ACE包含四個(gè)RT_R模塊和一個(gè)RT_T模塊,RT_R模塊負(fù)責(zé)響應(yīng)接收指令,RT_T模塊負(fù)責(zé)響應(yīng)發(fā)送指令。RT_ACE模塊的功能框圖如圖3所示。

RT_T模塊包含微控制器、通用寄存器和指令存儲(chǔ)器。模塊中定義了T_DEV信號(hào)來選擇發(fā)送的RT設(shè)備,指向?qū)?yīng)的SFR和數(shù)據(jù)存儲(chǔ)器。當(dāng)接收到RT發(fā)送命令時(shí),微控制器使用擴(kuò)展指令選定發(fā)送RT,然后使用其SFR和數(shù)據(jù)存儲(chǔ)器完成發(fā)送操作;當(dāng)接收到RT接收命令時(shí),RT_T模塊不工作。

RT_R模塊包含微控制器、通用寄存器、指令存儲(chǔ)器、8組特殊功能寄存器和8組數(shù)據(jù)存儲(chǔ)器,每個(gè)RT_R模塊可以實(shí)現(xiàn)8個(gè)RT,4個(gè)RT_R模塊可以實(shí)現(xiàn)32個(gè)RT(僅出現(xiàn)在禁用廣播命令的情況下)。模塊中定義了CURRENT_DEV信號(hào)來選擇當(dāng)前的設(shè)備,指向?qū)?yīng)的SFR和數(shù)據(jù)存儲(chǔ)器。在接收到非廣播接收命令時(shí),微控制器使用擴(kuò)展指令選擇命令字指定的RT;在接收到廣播接收命令時(shí),首先選擇第1個(gè)可用RT,在該RT處理完畢后,使用擴(kuò)展指令選擇下一個(gè)可用的RT繼續(xù)處理,直到全部可用RT處理完畢。在接收到發(fā)送命令時(shí),RT_R模塊不工作。

BM_ACE包含微控制器、指令存儲(chǔ)器、通用寄存器、特殊功能寄存器和數(shù)據(jù)存儲(chǔ)器。其運(yùn)行機(jī)制類似于BC_ACE模塊,這里不再贅述。

BUS_INTF作為收發(fā)器,是各總線終端與總線之間的接口,用來完成Manchester碼的編解碼和碼字正確性檢測(cè)工作。它包含一個(gè)32×16 bit的發(fā)送緩存、一個(gè)編碼器、兩套解碼器和一個(gè)編解碼狀態(tài)監(jiān)視器。發(fā)送緩存暫存各處理器請(qǐng)求發(fā)送的數(shù)據(jù),編碼器完成Manchester碼的生成,兩套解碼器分別負(fù)責(zé)A/B通道的解碼,狀態(tài)監(jiān)視器實(shí)現(xiàn)總線狀態(tài)的檢測(cè)和loopback(環(huán)回自測(cè))功能。

CTRL_INTF實(shí)現(xiàn)了上位機(jī)和協(xié)議控制器之間的通信功能。上位機(jī)通過板上的USB協(xié)議處理芯片與CTRL_INTF模塊的通信來配置協(xié)議控制器中各個(gè)節(jié)點(diǎn),并且可以在協(xié)議控制器工作過程中讀寫各節(jié)點(diǎn)的SFR和存儲(chǔ)器數(shù)據(jù)。

2.3軟件設(shè)計(jì)

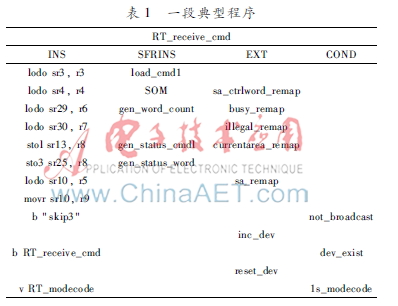

軟件設(shè)計(jì)是本設(shè)計(jì)中較為重要的部分,它直接影響到功能的正確性和運(yùn)行的實(shí)時(shí)性。設(shè)計(jì)中共有4段程序,分別是BC、RT_R、RT_T和BM的程序。出于效率的考慮,程序盡可能實(shí)現(xiàn)并行化操作,充分發(fā)揮MIMD的優(yōu)勢(shì),讓圖5仿真測(cè)試典型波形指令的每一個(gè)碼域都能在指令中充分應(yīng)用,從而最高效地完成所需要的功能。表1給出了一段典型的程序,可以看出,一條指令中有多個(gè)域,可以分別實(shí)現(xiàn)不同的功能,共同完成RT處理接收命令的過程。

3仿真驗(yàn)證與綜合

3.1仿真

采用VCS作為仿真工具進(jìn)行仿真,為提高仿真效率,使用System Verilog搭建了測(cè)試平臺(tái)。測(cè)試平臺(tái)使用隨機(jī)種子帶約束地隨機(jī)產(chǎn)生一定數(shù)量的總線事務(wù),根據(jù)事務(wù)內(nèi)容,通過CTRL_INTF模塊來配置初始化各總線終端,完成總線系統(tǒng)的初始化,隨后啟動(dòng)總線進(jìn)入工作狀態(tài)。在總線事務(wù)啟動(dòng)后,測(cè)試平臺(tái)的結(jié)果比較器開始監(jiān)測(cè)總線事務(wù),并使用內(nèi)建mailbox對(duì)比DUT的結(jié)果和預(yù)期的結(jié)果,從而判斷各終端的功能是否正確[5]。圖4顯示了測(cè)試平臺(tái)的架構(gòu)。

經(jīng)過大量的測(cè)試驗(yàn)證,結(jié)果表明設(shè)計(jì)滿足1553B總線標(biāo)準(zhǔn)的要求,能夠模擬整套1553B總線系統(tǒng)。

圖5顯示了仿真中BC到RT的廣播數(shù)據(jù)傳輸過程。BC運(yùn)行指令將消息發(fā)送到總線上,RT協(xié)議處理器接收到命令后依次選擇各RT節(jié)點(diǎn)處理該消息。

3.2綜合

目標(biāo)FPGA是Altera的EP3C80F474C8,這款FPGA存儲(chǔ)資源充裕但性能并不高。這樣選型主要是因?yàn)槎喙?jié)點(diǎn)協(xié)議處理器需要33×4K×16 bit的存儲(chǔ)資源(1個(gè)BC,31個(gè)RT,1個(gè)BM),而采用的多核MIMD架構(gòu)對(duì)速度和邏輯資源的要求不高,因此出于成本方面的考慮,選擇了這樣一款器件[6]。設(shè)計(jì)使用的時(shí)鐘頻率為16 MHz,在Quartus II 13.0中綜合結(jié)果如圖6所示。

圖6綜合報(bào)告實(shí)驗(yàn)表明,在該型號(hào)的FPGA上復(fù)制32份單節(jié)點(diǎn)協(xié)議處理器實(shí)現(xiàn)多節(jié)點(diǎn)處理器,所需的邏輯資源超出FPGA所能提供資源的一倍以上。從綜合報(bào)告中可以看出,采用多核MIMD系統(tǒng)大大降低了邏輯資源的占用,邏輯資源僅使用了可用資源的70%左右,在FPGA中仍有可觀的剩余邏輯資源。

4結(jié)論

研究提出了一種采用多核MIMD架構(gòu)實(shí)現(xiàn)多節(jié)點(diǎn)1553B總線協(xié)議處理器的方法,功能符合1553B總線標(biāo)準(zhǔn)的要求,并特別注意了邏輯資源的節(jié)約與復(fù)用,使設(shè)計(jì)邏輯規(guī)模可以在單片F(xiàn)PGA中實(shí)現(xiàn)。在后續(xù)的工作中,將進(jìn)一步優(yōu)化設(shè)計(jì),并開發(fā)測(cè)試板和PC上的測(cè)試應(yīng)用軟件[7],使整個(gè)系統(tǒng)作為完整的產(chǎn)品提供給用戶使用。

參考文獻(xiàn)

[1] 董大偉,周宇江,郭楹. 軍用總線發(fā)展趨勢(shì)研究[J]. 電子技術(shù)應(yīng)用,2015,41(7):710.

[2] Alta Data Technologies. MultiChannel 1553 Interface for PCI Systems[R]. 2011.

[3] Data Device Corporation. AceXtreme 1553/429 USB Avionics Device[R]. 2010.

[4] Data Device Corporation. ACE/MINIACE Series BC/RT/MT Intergrated 1553 Terminal User’s Guide[R]. 2010.

[5] Data Device Corporation. MILSTD1553 Designer’s Guide Sixth Edition[R]. 2003.

[6] 張春,麥宋平,趙益新. System Verilog驗(yàn)證測(cè)試平臺(tái)編寫指南[M].北京:科學(xué)出版社, 2009.

[7] 黃正,王健軍,劉士全,嚴(yán)華鑫. 基于NIOS II的1553B總線測(cè)試系統(tǒng)設(shè)計(jì)[J]. 微型機(jī)與應(yīng)用, 2015,34(18):98100.