0 引言

動(dòng)態(tài)測試技術(shù)是以捕捉和處理各種動(dòng)態(tài)信息為目的的一門綜合技術(shù),它在當(dāng)代科學(xué)技術(shù)中地位十分重要,在航天航空、儀器儀表、交通運(yùn)輸、軍事、醫(yī)療等研究中均應(yīng)用廣泛。常用的測試方法有遙測與存儲(chǔ)測試,與無線電遙測儀相比,存儲(chǔ)測試儀結(jié)構(gòu)更為簡單、無需發(fā)送天線、體積小、功耗低。存儲(chǔ)測試技術(shù)是對(duì)被測對(duì)象沒有影響或影響在允許范圍的條件下,在被測體內(nèi)放置微型數(shù)據(jù)采集存儲(chǔ)測試儀,現(xiàn)場實(shí)時(shí)完成信號(hào)的快速采集和存儲(chǔ),事后回收,由計(jì)算機(jī)處理和再現(xiàn)測試信息同時(shí)保證測試儀器完好的一種動(dòng)態(tài)測試技術(shù)。由于存儲(chǔ)測試對(duì)測試結(jié)果影響較小,測試數(shù)據(jù)準(zhǔn)確可靠,已經(jīng)漸漸成為測試動(dòng)態(tài)參數(shù)的重要手段。

1 系統(tǒng)整體設(shè)計(jì)

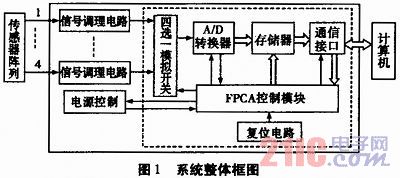

測試信號(hào)通過傳感器輸入測試電路中進(jìn)行處理并存儲(chǔ),隨后通過接口電路輸入到計(jì)算機(jī)中。測試參數(shù)限于一定范圍,測試通道數(shù)為4通道,最大采樣頻率為1MHz,最大存儲(chǔ)容量為512kW。本設(shè)計(jì)選用Altera公司推出的CycloneⅡ系列的EP2C5T144I8芯片。該芯片具有4608個(gè)邏輯單元,26塊M4K RAM塊,13個(gè)嵌入式乘法器,2個(gè)鎖相環(huán),用戶I/O引腳數(shù)目有89,可以滿足設(shè)計(jì)要求,并且有一定余量,方便以后功能的擴(kuò)展。AD轉(zhuǎn)換器選用AD公司推出的AD7492,而存儲(chǔ)器選用NanoAmp公司推出的N08L163WC2A,容量為512k×16bit。系統(tǒng)的整體框圖如圖1。

FPGA控制模塊實(shí)現(xiàn)對(duì)整個(gè)系統(tǒng)的邏輯控制,主要包括:AD控制、存儲(chǔ)器的讀寫、時(shí)鐘產(chǎn)生、負(fù)延遲計(jì)數(shù)及觸發(fā)模塊等。其中時(shí)鐘模塊為系統(tǒng)各芯片提供工作時(shí)鐘,并產(chǎn)生適合不同環(huán)境的采樣時(shí)鐘信號(hào)。負(fù)延遲模塊是為確保記錄信號(hào)的完整性,不致于把觸發(fā)信號(hào)以前的數(shù)據(jù)丟失。本設(shè)計(jì)負(fù)延遲為8 kW,負(fù)延遲計(jì)數(shù)器記滿(512-8)kW后停止計(jì)數(shù),采樣結(jié)束。觸發(fā)模塊主要是對(duì)系統(tǒng)由一個(gè)環(huán)境進(jìn)入另一個(gè)環(huán)境的方式進(jìn)行控制。觸發(fā)方式包括外觸發(fā)、計(jì)數(shù)觸發(fā)、比較觸發(fā)。計(jì)數(shù)觸發(fā)是對(duì)采樣點(diǎn)數(shù)進(jìn)行計(jì)數(shù),采樣點(diǎn)數(shù)等于預(yù)設(shè)的計(jì)數(shù)點(diǎn)數(shù)時(shí),就會(huì)產(chǎn)生觸發(fā)信號(hào)。比較觸發(fā)是采樣值與預(yù)設(shè)值作比較,當(dāng)采樣值大于或小于預(yù)設(shè)值時(shí)就會(huì)產(chǎn)生觸發(fā)信號(hào)。

2 采樣策略的研究

2.1 變頻采樣的狀態(tài)設(shè)計(jì)

在一些測試中,例如彈丸在全彈道運(yùn)動(dòng)過程中的加速度變化、石油開采過程中射孔時(shí)的壓力變化,被測信號(hào)的頻率變化很大,因此僅由信號(hào)的最高上限截止頻率確定采樣頻率是不合理的,信號(hào)的采樣頻率應(yīng)該是可變的。因此,需要對(duì)被測信號(hào)進(jìn)行采樣規(guī)律設(shè)計(jì),即設(shè)計(jì)一定的采樣策略,綜合考慮模糊誤差、測量時(shí)間、存儲(chǔ)容量等因素,從而達(dá)到最優(yōu)的測試效果。張文棟教授結(jié)合存儲(chǔ)測試?yán)碚撆c應(yīng)用對(duì)動(dòng)態(tài)測試的信號(hào)存儲(chǔ)過程提出了四種采樣策略,包括均勻采樣策略、自動(dòng)分段均勻采樣策略、編程分段自適應(yīng)均勻采樣策略以及自適應(yīng)采樣策略,這四種采樣策略均適合瞬態(tài)速變信號(hào)的存儲(chǔ)記錄。

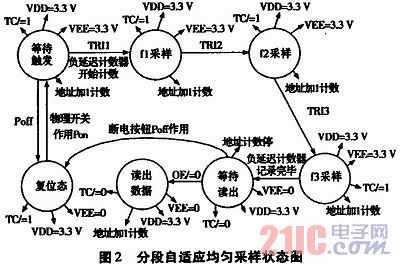

根據(jù)被測信號(hào)頻率變化很大的特點(diǎn),設(shè)計(jì)如圖2所示的狀態(tài)圖,實(shí)現(xiàn)對(duì)此類信號(hào)的變頻采樣。測試系統(tǒng)分環(huán)境對(duì)信號(hào)采樣記錄,每個(gè)環(huán)境的采樣頻率可以在采樣前進(jìn)行設(shè)置,本系統(tǒng)設(shè)計(jì)為三個(gè)環(huán)境,即采樣頻率最多變化三次。

在存儲(chǔ)測試開始之前,通過軟件編程將采集存儲(chǔ)過程分為幾個(gè)階段,根據(jù)被測信號(hào)的變化,每一個(gè)階段的采樣頻率、存儲(chǔ)點(diǎn)數(shù)、采樣開始時(shí)間會(huì)作自適應(yīng)的調(diào)整。首先接通電源使電路處于復(fù)位態(tài),此時(shí)數(shù)字電源VDD為通電、模擬電源VEE為斷電狀態(tài),系統(tǒng)中只有FPGA控制模塊工作;然后對(duì)電路編程設(shè)定各個(gè)環(huán)境的采樣頻率,給電路上電,電路進(jìn)入等待觸發(fā)態(tài),此時(shí)VDD、VEE通電,存儲(chǔ)器、AD轉(zhuǎn)換器啟動(dòng),開始采樣,地址計(jì)數(shù)器開始工作;觸發(fā)信號(hào)TRI1到來后,進(jìn)入f1采樣態(tài),系統(tǒng)按編程設(shè)定的采樣頻率f1開始采樣,負(fù)延遲計(jì)數(shù)器開始工作;2環(huán)境觸發(fā)后,系統(tǒng)按照設(shè)定的采樣頻率f2進(jìn)行采樣,此時(shí)處于f2采樣態(tài);3環(huán)境觸發(fā)后,系統(tǒng)按采樣頻率f3采樣,處于f3采樣態(tài);當(dāng)負(fù)延遲計(jì)數(shù)器計(jì)滿設(shè)定值時(shí),地址計(jì)數(shù)器和負(fù)延遲計(jì)數(shù)器均停止工作,VEE斷電,系統(tǒng)進(jìn)入等待讀出態(tài);在讀出數(shù)據(jù)態(tài),地址同步推進(jìn),直到讀完所有的數(shù)據(jù)。

2.2 變頻采樣的模塊設(shè)計(jì)

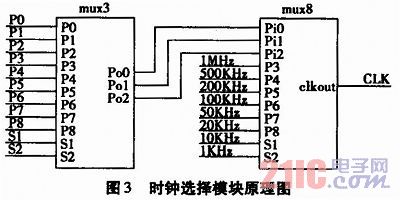

采樣頻率決定了采樣信號(hào)的質(zhì)量和數(shù)量,采樣頻率太高,會(huì)使采得的信號(hào)數(shù)量劇增,占用大量的存儲(chǔ)單元,采樣頻率太低的話,會(huì)使模擬信號(hào)的某些信息丟失,恢復(fù)出的信號(hào)會(huì)出現(xiàn)失真。為了達(dá)到最佳效果,必須根據(jù)信號(hào)的特點(diǎn)選擇合適的采樣頻率。圖3為設(shè)計(jì)的采樣時(shí)鐘選擇模塊。

設(shè)計(jì)可選采樣頻率有八種,如圖3中1 MHz~1 kHz,都是由FPGA的時(shí)鐘模塊分頻而來,可根據(jù)實(shí)際情況修改。S1、S2為環(huán)境選擇信號(hào);P0~P2、P3~P5、P6~P8三組信號(hào)分別是三個(gè)環(huán)境的采樣頻率控制字,在測試前根據(jù)環(huán)境采樣頻率的需要來編程設(shè)定;模塊mux8為8選1數(shù)據(jù)選擇器,根據(jù)輸入的三個(gè)控制字來選擇對(duì)應(yīng)的采樣頻率輸出。系統(tǒng)上電后,環(huán)境選擇信號(hào)S1、S2為“00”,模塊mux3將1環(huán)境的采樣頻率控制字P0、P1、P2輸入到模塊mux8中,系統(tǒng)自動(dòng)以1環(huán)境的采樣頻率進(jìn)行采樣;2環(huán)境的觸發(fā)信號(hào)到來時(shí),S1、S2由“00”跳變?yōu)?ldquo;10”,2環(huán)境的采樣頻率控制字P3~P5送到mux8中,以2環(huán)境的采樣頻率進(jìn)行采樣;當(dāng)3環(huán)境的觸發(fā)信號(hào)來臨,S1、S2由“10”跳變?yōu)?ldquo;11”,3環(huán)境的采樣頻率控制字P6~P8被選中,系統(tǒng)以3環(huán)境的采樣頻率采樣。

3 實(shí)驗(yàn)驗(yàn)證

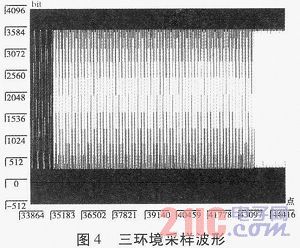

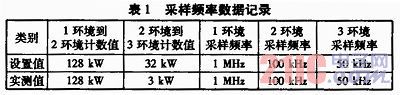

該實(shí)驗(yàn)對(duì)標(biāo)準(zhǔn)信號(hào)發(fā)生器輸出的正弦波信號(hào)進(jìn)行采集和存儲(chǔ),采樣策略選擇為三環(huán)境采樣,1環(huán)境采樣頻率為1 MHz,2環(huán)境為100 kHz,3環(huán)境為50 kHz,外觸發(fā)進(jìn)入1環(huán)境,計(jì)數(shù)觸發(fā)進(jìn)入2環(huán)境,計(jì)數(shù)值128 kW,計(jì)數(shù)觸發(fā)進(jìn)入3環(huán)境,計(jì)數(shù)值32 kW。系統(tǒng)采樣完畢后,連接到計(jì)算機(jī)通過上位機(jī)軟件讀取數(shù)據(jù),實(shí)驗(yàn)波形如圖4。

設(shè)置為計(jì)數(shù)128 kW進(jìn)入2環(huán)境,計(jì)數(shù)32 kW進(jìn)入3環(huán)境,而系統(tǒng)負(fù)延遲為8 kW,分為4個(gè)通道,因此1、2環(huán)境的分界點(diǎn)為(128+8)·1024/4=34816點(diǎn),2、3環(huán)境的分界點(diǎn)為(128+8+32)*1024/4=43008點(diǎn),實(shí)驗(yàn)波形與計(jì)算值相符。如表1所示:

通過上表可以看出,系統(tǒng)變頻采樣模塊的設(shè)計(jì)滿足系統(tǒng)的要求,并且系統(tǒng)是完全按照設(shè)定的采樣策略進(jìn)行采樣的。

4 結(jié)束語

介紹了一種用FPGA實(shí)現(xiàn)的動(dòng)態(tài)測試存儲(chǔ)測試系統(tǒng)。通過實(shí)驗(yàn)驗(yàn)證,表明系統(tǒng)能對(duì)信號(hào)進(jìn)行不失真采樣存儲(chǔ)。證實(shí)了所設(shè)計(jì)的采樣策略對(duì)多種變化規(guī)律的信號(hào)采集具有通用性,實(shí)現(xiàn)了對(duì)信號(hào)的變頻采樣,擴(kuò)展了系統(tǒng)的應(yīng)用范圍。