VXI總線是VMEbus eXtensions for Instrumentation 的縮寫。VXI主機(jī)箱有13個(gè)插槽,其中,零槽控制器為系統(tǒng)的管理者。VXI模塊根據(jù)其本身的性質(zhì)、特點(diǎn)和所支持的通信規(guī)程可以分為寄存器基、消息基、存儲(chǔ)器和擴(kuò)展模塊四種類型。每個(gè)模塊的地址空間有A16、A16/A24和A16/A32三種類型。

VXI總線測(cè)試平臺(tái)是儀器測(cè)量領(lǐng)域的前沿技術(shù),可以靈活地組建自動(dòng)測(cè)試系統(tǒng),其模塊化、靈活性強(qiáng)、即插即用、數(shù)字吞吐能力強(qiáng)的特點(diǎn)使VXI總線測(cè)試平臺(tái)的應(yīng)用越來越廣泛。

在自動(dòng)控制、智能檢測(cè)、數(shù)字系統(tǒng)故障診斷領(lǐng)域,經(jīng)常需要非周期性地產(chǎn)生任意編碼的數(shù)字序列,作為激勵(lì)信號(hào)源。基于VXI總線的任意數(shù)字信號(hào)發(fā)生器,是一個(gè)B尺寸、單槽、A16/D16、寄存器基模塊,它能夠產(chǎn)生任意編碼的數(shù)字信號(hào),8路數(shù)字信號(hào)均可獨(dú)立地任意編輯,輸出信號(hào)最小脈寬為25ns.采用Altera公司的FLEX系列的FPGA,可實(shí)現(xiàn)寄存器基接口電路和部分功能電路。用LabWindows/CVI軟件設(shè)計(jì)了虛擬儀器軟面板,界面友好,操作方便。

1 系統(tǒng)組成及工作原理

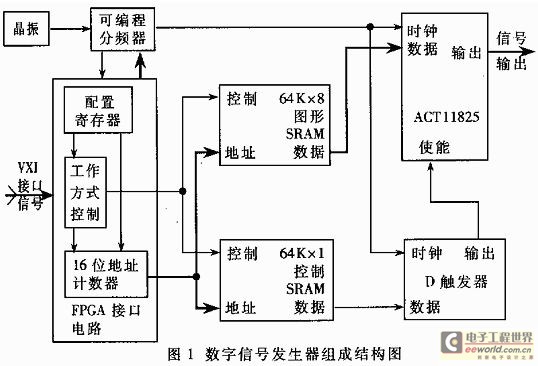

數(shù)字信號(hào)發(fā)生器采用VXI總線測(cè)試平臺(tái),有8路獨(dú)立的輸出信號(hào),均可預(yù)先存儲(chǔ)在容量為64K的靜態(tài)存儲(chǔ)器中,可以獨(dú)立地編輯各種輸出信號(hào);時(shí)鐘頻率最高可達(dá)40MHz;輸出信號(hào)支持高電平、低電平和高阻態(tài)三種狀態(tài);輸出電平兼容CMOS/TTL電平;輸出信號(hào)擺率不超過±5ns;采用可編程分頻器,實(shí)現(xiàn)對(duì)時(shí)鐘的任意分頻;輸出電平脈沖寬度可編程調(diào)節(jié)。系統(tǒng)的組成框圖如圖1所示。

在PC機(jī)上將編輯好的8路波形數(shù)據(jù)文件和1路三態(tài)控制數(shù)據(jù)文件分別裝載到64K×8的靜態(tài)存儲(chǔ)器和64K×4的靜態(tài)存儲(chǔ)器中。波形文件的裝載是通過VXI總線的地址譯碼選擇A1~A5中某一配置寄存器的地址,再結(jié)合寫操作來完成的。由于VXI總線每進(jìn)行一次寫操作,都會(huì)產(chǎn)生一個(gè)低電平有效的脈沖信號(hào)LATCH*,LATCH*信號(hào)將8路信號(hào)的8位編碼波形數(shù)據(jù)和1位三態(tài)控制數(shù)據(jù)存入寄存器,當(dāng)進(jìn)行下一個(gè)寫操作時(shí),完成下8位編碼波形數(shù)據(jù)和三態(tài)控制數(shù)據(jù)的裝載,直至所有的波形數(shù)據(jù)裝載完畢。波形數(shù)據(jù)文件的裝載在LabWindows/CVI所開發(fā)的驅(qū)動(dòng)程序作用下工作,當(dāng)系統(tǒng)加電或軟件復(fù)位時(shí),16位地址計(jì)數(shù)器的初始地置為0000H,在16位地址計(jì)數(shù)器的作用下,能夠?qū)崿F(xiàn)0000H~FFFFH或任一指定地址范圍的數(shù)據(jù)加載。

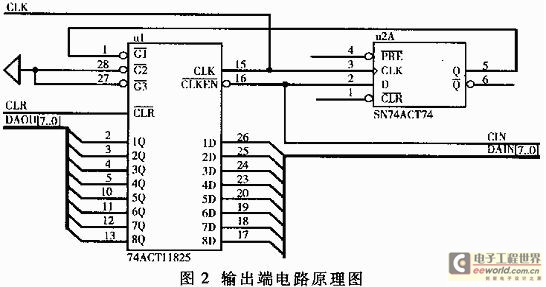

當(dāng)驅(qū)動(dòng)程序輸出波形文件時(shí),指定某一起始地址作為16位的地址計(jì)數(shù)器的當(dāng)努、當(dāng)發(fā)出允許輸出信號(hào)時(shí),由可編輯分頻器所分頻的時(shí)鐘信號(hào)同時(shí)加到16位地址計(jì)數(shù)器、輸出觸發(fā)器74ACT11825以及D觸發(fā)器SN74ACT74上,在時(shí)鐘信號(hào)的作用下,16位地址計(jì)數(shù)器開始計(jì)數(shù)。靜態(tài)存儲(chǔ)器采用的是CYPRESS公司的CY74194芯片,從地址有效到數(shù)據(jù)輸出的最小延遲時(shí)間為12ns,存儲(chǔ)器輸出的8路波形數(shù)據(jù)DAIN[70]和1路三態(tài)控制信號(hào)CIN作用在輸出芯片74ACT11825上,如圖2所示。當(dāng)三態(tài)控制存儲(chǔ)器輸出的信號(hào)為低電平時(shí),輸出的波形數(shù)據(jù)與靜態(tài)存儲(chǔ)器中選通的波形數(shù)據(jù);當(dāng)三態(tài)控制存儲(chǔ)器輸出的信號(hào)為高電平時(shí),則74ACT11825的時(shí)鐘允許信號(hào)線無效,此時(shí)的高電平信號(hào)經(jīng)過SN74ACT74觸發(fā)器的輸出端,作用在74ACT11825的輸出使能端上,使輸出信號(hào)為高阻態(tài)。

2 任意可編程分頻器的實(shí)現(xiàn)

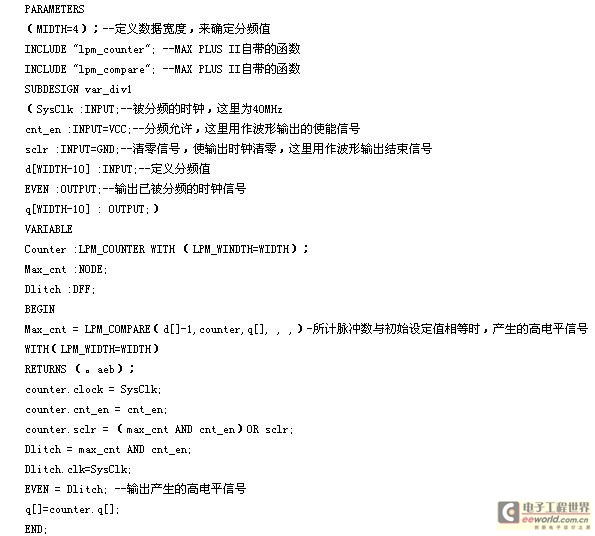

任意可編程分頻器是用來實(shí)現(xiàn)對(duì)40MHz時(shí)鐘信號(hào)的任意分頻,它實(shí)現(xiàn)的分頻值由輸入的初始值d[WIDTH-10]所決定。這里取WIDTH=10,則能實(shí)現(xiàn)2~1024的分頻。也可以根據(jù)電路的不同要求,選擇不同的WIDTH值,實(shí)現(xiàn)不同的分頻。由于采用ALTERA公司的可編程器件,用AHDL硬件語言描述的分頻器代碼如下:

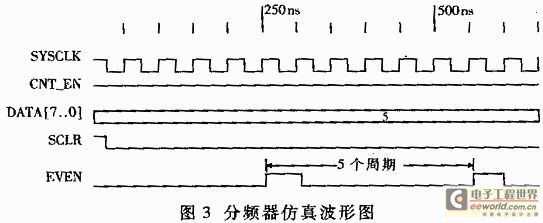

在MAX PLUS II軟件中進(jìn)行仿真,設(shè)定DATA[70]的值為5,即為5分頻,輸出波形EVEN如圖3所示。

3 VXI總線接口設(shè)計(jì)

采用Altera公司的FLEX系列的EPF10K20RC208-3的FPGA實(shí)現(xiàn)寄存器基接口芯片。由于該器件集成度高,可方便地改變邏輯,而且對(duì)邏輯設(shè)計(jì)可事先進(jìn)行功能模塊和定時(shí)模擬,因而使得接口設(shè)備更輕松,調(diào)試更方便。接口電路實(shí)現(xiàn)了如下功能:①內(nèi)部集成了VXI總線所需的寄存器,由地址信號(hào)A1~A5為各個(gè)寄存器譯碼分配地址,寄存器類型分別為ID寄存器、儀器類型寄存器、狀態(tài)/控制寄存器、控制寄存器。②數(shù)據(jù)總線驅(qū)動(dòng)器,其功能為將P1連接器上的16位數(shù)據(jù)線D0~D15送至模塊內(nèi)部數(shù)據(jù)總線DBD~DB15或反之。可用兩個(gè)8位三態(tài)雙向緩沖器組成。用READ控制數(shù)據(jù)傳遞方向,用DBEN*選能。③總線握手控制,其功能為利用P1連接器上的信號(hào)控制DS1*、DS0*、WRITE*和地址線譯碼輸出地址信號(hào)共同產(chǎn)生DBEN*、LATCH*和DTACK*信號(hào),LATCH*可用來參與選擇模塊內(nèi)需要寫數(shù)據(jù)的寄存器。DTACK*信號(hào)輸出到P1連接器上,使VXI總線系統(tǒng)能正常工作并按規(guī)定時(shí)序讀*寫數(shù)據(jù)。DBEN*用來控制模塊內(nèi)地址及數(shù)據(jù)的有效周期。用AHDL硬件描述語言實(shí)現(xiàn)讀狀態(tài)機(jī)、寫狀態(tài)機(jī)和中斷狀態(tài)機(jī),產(chǎn)生的DBEN*、LATCH*、DTACAK*信號(hào)應(yīng)符合VXI總線系統(tǒng)中數(shù)據(jù)讀/寫的時(shí)序規(guī)范。④譯碼16位VXI總線地址,具有16位數(shù)據(jù)線的傳送能力,采用LabWindows/CVI軟件,實(shí)現(xiàn)對(duì)某一地址的讀寫操作,完成波形數(shù)據(jù)文件的加載、控制波形文件的輸出、停止輸出等操作。