便攜設備訪問片外SDRAM的低功耗設計研究

摘要: 在基于DSP的嵌入式應用中,存儲器系統(tǒng)逐漸成為功耗的主要來源。例如Micron公司的MT48LC2Mx32B2-5芯片,在讀寫時功耗最大可以到達924 mW,而大部分DSP的內(nèi)核功耗遠遠小于這個數(shù)值。如TI的TMS320C55x系列的內(nèi)核功耗僅僅為0.05 mW/MIPS。所以說,優(yōu)化存儲系統(tǒng)的功耗是嵌入式DSP極其重要的設計目標。本文主要以訪問外部SDRAM為例來說明降低外部存儲系統(tǒng)功耗的設計方法。

Abstract:

Key words :

DSP有限的片內(nèi)存儲器容量往往使得設計人員感到捉襟見肘,特別是在數(shù)字圖像處理、語音處理等應用場合,需要有高速大容量存儲空間的強力支持。因此,需要外接存儲器來擴展DSP的存儲空間。

在基于DSP的嵌入式應用中,存儲器系統(tǒng)逐漸成為功耗的主要來源。例如Micron公司的MT48LC2Mx32B2-5芯片,在讀寫時功耗最大可以到達924 mW,而大部分DSP的內(nèi)核功耗遠遠小于這個數(shù)值。如TI的TMS320C55x系列的內(nèi)核功耗僅僅為0.05 mW/MIPS。所以說,優(yōu)化存儲系統(tǒng)的功耗是嵌入式DSP極其重要的設計目標。本文主要以訪問外部SDRAM為例來說明降低外部存儲系統(tǒng)功耗的設計方法。

1 SDRAM功耗來源

SDRAM內(nèi)部一般分為多個存儲體,通過行、列地址分時復用,系統(tǒng)地址總線對不同存儲體內(nèi)不同頁面的具體存儲單元進行尋址。SDRAM每個存儲體有2個狀態(tài),即激活狀態(tài)和關閉狀態(tài)。在一次讀寫訪問完畢后,維持存儲體激活狀態(tài)稱為開放的頁策略(open-page policy),頁面寄存器中保存已經(jīng)打開的行地址,直到它不得不被關閉,比如要執(zhí)行刷新命令等;訪問完畢后關閉存儲體稱為封閉的頁策略(close-page pol-icy)。

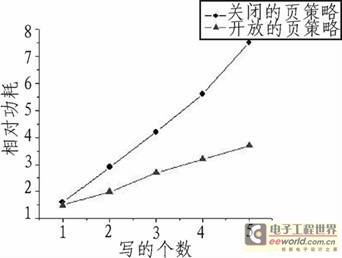

為了更好地決定選擇哪種策略,需要熟悉SDRAM功耗的特點。SDRAM的功耗主要有3個來源:激活關閉存儲體、讀寫和刷新。在大部分程序中,激活關閉存儲體引起的功耗占到訪存操作的總功耗的一半以上。圖1給出了對同一SDRAM行進行讀寫時,采用開放的頁策略和封閉的頁策略的功耗比較(假設激活關閉存儲體一次消耗功耗為1),經(jīng)計算可知,若連續(xù)的幾個讀寫操作在同一行,采用開放的頁策略可以節(jié)省功耗。

圖1 開放的頁策略和封閉的頁策略的功耗比較

根據(jù)上面對SDRAM功耗的特點的分析可知,盡量減少激活/關閉存儲體引起的附加功耗開銷,是優(yōu)化SDRAM存儲系統(tǒng)功耗的根本,另外不能忽視一直處于激活狀態(tài)的存儲體帶來的功耗。

2 訪問SDRAM的低功耗優(yōu)化設計方案

為更好的管理外部SDRAM,大部分嵌入式DSP片上集成和外部存儲器的接口EMIF(External Memory InteRFace),DSP的片內(nèi)設備通過EMIF訪問和管理存儲器。由EMIF將對同一行的讀寫盡量歸并到一起進行,減少激活/關閉存儲體引起的附加功耗開銷。圖2為基于總線監(jiān)測的讀寫歸并設計方案的框圖。

圖2 基于總線監(jiān)測的讀寫歸并設計方案的框圖

1)采用塊讀的方法取指令。加入簡化的指令Cache(I-Cache),將對SDRAM的讀程序讀操作按塊進行。只有在Cache錯過時,由Cache通過EMIF對SDRAM進行塊讀,每次讀16個字節(jié)。

2)加入寫后數(shù)據(jù)緩沖區(qū)(WPB,Write PoST Buffer),將數(shù)據(jù)總線上的請求發(fā)往WPB,由WPB對SDRAM進行塊寫、讀寫歸并。

3)動態(tài)監(jiān)測EMIF總線的利用率,塊讀和讀寫歸并時采用開放的頁策略,當總線利用率較低時,采用封閉的頁策略,當總線利用率很低時,將SDRAM進入休眠模式。

3 訪問SDRAM的低功耗設計

3.1 采用塊讀的I-Cache

對于程序總線的讀操作,根據(jù)程序的局部性原理,下一次要取得指令和當前要取指的指令在空間上很可能相鄰,因此對于讀程序采用塊讀的方法,每次讀一個塊,而不是一個字,并采用開放的頁策略,因此對同一行的讀寫操作不需要額外的激活/關閉操作,可以較快的完成。

當指令放在片外存儲器里時,可以將CPU最近使用的指令放在I-Cache中,鑒于改善整個系統(tǒng)的性能和低功耗設計的需求。DSP的I-Cache大小設計為8 KB,包括2塊存儲器,其結構相同,每一塊結構如下:

1)數(shù)據(jù)隊列,每個隊列包含256行,每行16個字節(jié)。當I-Cache錯過時,會采用最近最少使用算法(LRU)替換掉最長時間沒有使用的行。

2)行有效位隊列,每行有一個行有效位,一旦一行裝滿數(shù)據(jù)。就置位該行有效位。

3)標簽隊列,每一行有一個標簽域,表明該行的數(shù)據(jù)的起始地址。當一行填滿,相應的標簽將存到該行的標簽域中。

如果要取的指令字在I-Cache中(命中),I-Cache會直接將其送給DSP。如果要取的指令字不在I-Cache中(錯過),I-Cache會通過EMIF從外部存儲器接口讀取4個32 b的代碼塊。一旦這個指令字被讀到I-Cache中,就送給CPU。

3.2 寫后緩沖區(qū)的設計

數(shù)據(jù)在存儲器中的存放位置可能不像程序空間那么連續(xù),而且數(shù)據(jù)空間有讀寫,對數(shù)據(jù)空間讀寫SDRAM進行優(yōu)化的基本思想是,歸并對SDRAM同一行的讀寫操作。具體來說,包括歸并對同一行的多個讀操作、歸并對同一行的多個寫操作,歸并對同一行的多個讀寫操作3種情況,文獻提出了這種設計方法,其基本思想是:系統(tǒng)從預取緩沖區(qū)(FB,F(xiàn)etch Buffer)中取數(shù)據(jù);寫數(shù)據(jù)時,先寫到寫歸并緩沖區(qū)(WCB,Write Combine Buffer);對在FB或WCB中的同一行的讀寫請求進行歸并。但此設計方法是針對有一級Cache的通用微處理器系統(tǒng),過于復雜,實現(xiàn)代價過高,不適合于本文研究的沒有一級數(shù)據(jù)Cache的DSP,因此這里采用寫后緩沖區(qū)(Write Post Buffer)的方法,具體設計方法如下:

1)在EMIF中設立一個寫后緩沖區(qū),所有對SDRAM的讀寫請求均送到寫后緩沖區(qū),寫后緩沖區(qū)立即給CPU響應,CPU可以不用等待寫操作的結束而繼續(xù)執(zhí)行程序。

2)每當寫后緩沖區(qū)接受到一個新的寫請求后,首先判斷寫后寄存器中是否存在和該寫操作在SDRAM同一行的寫操作,若有,將這兩個寫操作歸并后同時向SDRAM進行寫。

3)當CPU讀數(shù)據(jù)時,首先檢查寫后緩沖區(qū),若存在要讀的數(shù)據(jù),直接從寫后緩沖區(qū)讀數(shù)據(jù);若不存在,則從寫后緩沖區(qū)中挑選和當前讀操作在同一行的寫操作歸并后,對SDRAM進行讀、寫操作。

設計寫后緩沖區(qū)不僅可以提高程序的執(zhí)行效率,還可以節(jié)省功耗。綜合考慮系統(tǒng)的性能與功耗要求,這里DSP寫后緩沖區(qū)設計為8 KB,采用和I-Cache類似的結構。

3.3 動態(tài)監(jiān)測總線利用率

SDRAM在所有的行都打開,等待讀寫操作時的功耗是所有行都關閉時的2倍多,因此SDRAM為了低功耗的需要,設計時都加入了休眠模式。當對同一行有大量的讀寫時,又需要采用開放的頁策略,維持這些行打開。考慮到SDRAM的這些特點,單獨采用開放的頁策略或封閉的頁策略是不合適的,需要結合運用。動態(tài)監(jiān)測EMIF總線的利用率,塊讀、塊寫和讀寫歸并時采用開放的頁策略,當總線利用率較低時,采用封閉的頁策略,當總線利用率很低時,將SDRAM進入休眠模式,需要時再澈活。

以MT48LC2M32P2為例進行功耗估算,假設前后兩次訪問命中同一行的概率是90%,當總線利用率(每個周期內(nèi)總線被平均利用的次數(shù))高于25%時。采用開放的頁策略比采用封閉的頁策略節(jié)省功耗,當總線利用率在25%~20%之間時,采用兩種策略差別不大,維持當前采用的策略,當總線利用率低于20%時,采用封閉的頁策略比采用開放的頁策略節(jié)省功耗,當總線利用率低于10%時,在采用封閉的頁策略的同時,每次訪問結束后都將SDRAM進入休眠模式,比單純采用封閉的頁策略更節(jié)約功耗。

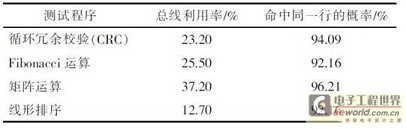

文獻統(tǒng)計了通用處理器中不同程序的總線的利用率,如表1所示。可見,對于不同的程序,總線利用率差別較大。根據(jù)當前總線的利用率來決定采用何種策略訪問SDRAM是比較合適的。

通用處理器中不同程序的總線的利用率

4 優(yōu)化后的EMIF的性能分析

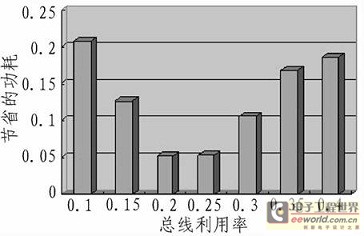

對采用的總線監(jiān)測的讀寫歸并方案進行計算,假設前后命中同一行的概率是90%,根據(jù)Micron數(shù)據(jù)手冊計算,歸并兩個寫操作功耗減少24%,對不同的總線利用率的計算結果如圖3所示。

圖3 基于總線監(jiān)測的讀寫歸并方案功耗計算

5 結束語

在基于DSP的嵌入式應用系統(tǒng)中,存儲系統(tǒng)的功耗占據(jù)系統(tǒng)功耗的大部分。當外部存儲器采用SDRAM時,降低SDRAM的換行訪問可以節(jié)約大量的功耗。本文設計的基于總線監(jiān)測的讀寫歸并方案,不僅降低了外部存儲系統(tǒng)的功耗,而且可以在一定程度上提高存儲系統(tǒng)的性能。加入的I-Cache可以使程序總線更快地讀指令,加入的寫后緩沖區(qū)(WPB)可以使CPU不用等待緩慢的外部寫操作的結束而直接繼續(xù)執(zhí)行指令。

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權禁止轉載。