SDRAM有一個同步接口,在響應(yīng)控制輸入前會等待一個時鐘信號,這樣就能和計算機的系統(tǒng)總線 同步。時鐘被用來驅(qū)動一個有限狀態(tài)機,對進入的指令進行管線(Pipeline)操作。

這使得SDRAM與沒有同步接口的異步DRAM相比,可以有一個更復(fù)雜的操作模式。

管線 意味著芯片可以在處理完之前的指令前,接受一個新的指令 。在一個寫入的管線 中,寫入命令在另一個指令執(zhí)行完之后可以立刻執(zhí)行,而不需要等待數(shù)據(jù)寫入存儲隊列的時間。

在一個讀取的流水線中,需要的數(shù)據(jù) 在讀取指令發(fā)出之后固定數(shù)量的時鐘頻率后到達,而這個等待的過程可以發(fā)出其它附加指令。這種延遲被稱為等待時間(Latency),在為計算機購買內(nèi)存時是一個很重要的參數(shù)。

SDRAM在計算機中被廣泛使用,從起初的SDRAM到之后一代的DDR(或稱DDR1),然后是DDR2 和DDR3 進入大眾市場,2015年開始DDR4進入消費市場。如UMI型號 UD408G5S1AF的一款8Gb 32位 DDR4 SDRAM,是一款支持使用在英特爾Arria 10 SoC FPGA以及Kintex Ultrascale FPGA中的存儲器。

32位 DDR4 SDRAM非常適合邊緣類計算,或?qū)CB面積有緊湊要求的深度學(xué)習(xí)計算設(shè)備。英尚微支持32位DDR4 SDRAM送樣及測試。

為什么要使用內(nèi)存控制器?

動態(tài)內(nèi)存的驅(qū)動比靜態(tài)內(nèi)存的驅(qū)動更加復(fù)雜…我們需要行,列和存儲體以及刷新周期來處理。但是由于SDRAM的高速性和低單位成本使其引人注目。

因此我們需要的是一種訪問SDRAM的方法,但是要易于使用靜態(tài)內(nèi)存。這就是創(chuàng)建內(nèi)存控制器的原因。它們充當(dāng)轉(zhuǎn)換層:一方面,它們?yōu)橛脩籼峁┝艘子谑褂玫膬?nèi)存接口,然后進行了繁瑣的工作來驅(qū)動真實的SDRAM信號。

SDRAM引腳

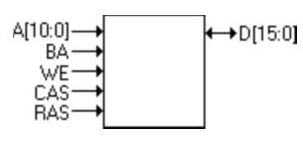

如果我們看一下SDRAM的引腳,那么會有一些新來者。

地址和數(shù)據(jù)總線仍然存在,但是地址總線只有11位(用于提供要打開的行,然后提供列地址)。BA引腳指定了存儲區(qū)(由于在我們的示例中只有2個存儲區(qū),因此我們僅需要一個引腳)。

WE,CAS和RAS一起用作命令引腳,因此我們可以向SDRAM發(fā)送8個不同的命令(命令包括“打開行”,“讀取”,“寫入”和“關(guān)閉行”)。使用了其他一些引腳(但未在圖片上顯示),例如時鐘,片選,字節(jié)使能…

請注意,在動態(tài)內(nèi)存中,“打開行”稱為激活,“關(guān)閉行”稱為預(yù)充電。

刷新

SDRAM是動態(tài)存儲器:由于每個存儲器位值(0或1)都保存在一個微小的電容器中,電荷隨時間衰減,因此需要定期刷新其內(nèi)容。

但是衰減率足夠低,只要定期對其進行讀取和重新寫入(“刷新”),制造商就可以保證不會丟失任何數(shù)據(jù)。

有兩種刷新機制

· FPGA將“自動刷新”命令發(fā)送到SDRAM。

只要確保它定期完成(SDRAM數(shù)據(jù)表會告訴您最小刷新頻率)。

· FPGA“經(jīng)常”訪問每一行。

打開一行會導(dǎo)致SDRAM中的“感測放大器”獲得該行所有電容器電荷的副本。然后,當(dāng)該行關(guān)閉時,較早檢測到的值將被復(fù)制回電容器中,從而刷新過程中的數(shù)據(jù)。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<