本文以OrCAD/PSpice 10.5為工具,對555定時(shí)器構(gòu)成的三種典型電路進(jìn)行仿真分析,得出了一些有價(jià)值的結(jié)論。

555定時(shí)器是一種將模擬功能與數(shù)字(邏輯)功能緊密結(jié)合在一起的中小規(guī)模單片集成電路。它功能多樣,應(yīng)用廣泛,只要外部配上幾個(gè)阻容元器件即可構(gòu)成單穩(wěn)態(tài)觸發(fā)器、施密特觸發(fā)器、多諧振蕩器等電路,是脈沖波形產(chǎn)生與變換的重要元器件,廣泛應(yīng)用于信號的產(chǎn)生與變換、控制與檢測、家用電器以及電子玩具等領(lǐng)域。

OrCAD/PSpice作為國際上著名的電子設(shè)計(jì)自動(dòng)化軟件之一,具有仿真速度快、精度高等優(yōu)點(diǎn),不僅可以用于電路分析和優(yōu)化設(shè)計(jì),與印制版設(shè)計(jì)軟件配合使用,還可實(shí)現(xiàn)電子設(shè)計(jì)自動(dòng)化,被公認(rèn)是通用電路模擬程序中最優(yōu)秀的軟件之一。例如:基于該軟件,Essakhi等人提出了一種微波整流天線的時(shí)域模型;Du等人提出了一種從三維時(shí)域場分析提取S參數(shù)的方法;Zhang等人仿真了E類功率放大器的特性,并進(jìn)行了實(shí)驗(yàn)證實(shí);Sakuta等人分析了低相位噪聲振蕩器的特性,并計(jì)算了有載Q值;Hayahara等人設(shè)計(jì)了△-∑A/D轉(zhuǎn)換器,并對其信噪比進(jìn)行了仿真;Brecl等人提出了一維、二維薄膜模型,并模擬了其接觸電阻。這些表明,軟件OrCAD/PSpice是現(xiàn)代電子電路設(shè)計(jì)的有利工具。

1 555定時(shí)器組成框圖及工作原理

555定時(shí)器的圖形符號及管腳圖如圖1所示,其中管腳1是公共端,管腳2為觸發(fā)端,管腳3為輸出端,管腳4為復(fù)位端,管腳5是控制電壓輸入端,管腳6為閾值端,管腳7是內(nèi)部三極管的放電端,管腳8是電源端。

555定時(shí)器的內(nèi)部電路方框圖如圖2所示,該集成電路由四部分組成:電阻分壓器、電壓比較器、基本RS觸發(fā)器、輸出緩沖器和放電三極管。

比較器的參考電壓由三只5 kΩ的電阻器構(gòu)成分壓,它們分別使高電平比較器A1同相比較端和低電平比較器A2的反相輸入端的參考電平為2Vcc/3和Vcc/3。A1和A2的輸出端控制RS觸發(fā)器狀態(tài)和放電管開關(guān)狀態(tài)。當(dāng)輸入信號輸入并超過2Vcc/3時(shí),觸發(fā)器復(fù)位,555的輸出端3腳輸出低電平,同時(shí)放電,開關(guān)管導(dǎo)通;當(dāng)輸入信號自2腳輸入并低于Vcc/3時(shí),觸發(fā)器置位,555的3腳輸出高電平,同時(shí)充電,開關(guān)管截止。

MR是復(fù)位端,當(dāng)其為0時(shí),555輸出低電平。平時(shí)該端開路或接Vcc。

CO是控制電壓端(5腳),平時(shí)輸出2Vcc/3作為比較器A1的參考電平,當(dāng)5腳外接一個(gè)輸入電壓,即改變了比較器的參考電平,從而實(shí)現(xiàn)對輸出的另一種控制,在不接外加電壓時(shí),通常接一個(gè)0.01μF的電容器到地,起濾波作用,以消除外來的干擾,以確保參考電平的穩(wěn)定。

T為放電管,當(dāng)T導(dǎo)通時(shí),將給接于腳7的電容器提供低阻放電電路。

2 單穩(wěn)態(tài)觸發(fā)器仿真分析

單穩(wěn)態(tài)觸發(fā)器廣泛用于脈沖整形、延時(shí)及定時(shí)電路中。單穩(wěn)態(tài)觸發(fā)器有一個(gè)穩(wěn)態(tài)和一個(gè)暫穩(wěn)態(tài),在無外來觸發(fā)脈沖作用時(shí),電路保持穩(wěn)態(tài)不變,而當(dāng)有外來觸發(fā)脈沖作用下,電路由穩(wěn)態(tài)翻轉(zhuǎn)到暫穩(wěn)態(tài),并輸出一個(gè)脈寬和幅值恒定的矩形脈沖,輸出的脈沖寬度TW等于暫穩(wěn)態(tài)的持續(xù)時(shí)間,而暫穩(wěn)態(tài)的持續(xù)時(shí)間取決于R2,C2,則:

![]()

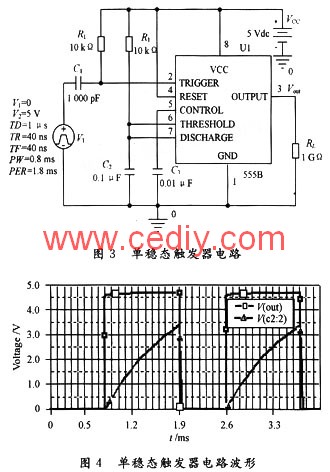

運(yùn)行OrCAD/CaptureCIS,利用Schematics繪制的由555定時(shí)器構(gòu)成的單穩(wěn)態(tài)觸發(fā)器電路見圖3,輸入信號Vi為脈沖電壓源(VPULSE),設(shè)置其參數(shù)如下:

值得注意的是,輸入信號VPULSE的重復(fù)周期必須大于輸出的脈沖寬度TW,輸入信號VPULSE的脈寬應(yīng)小于TW,才能保證每一個(gè)正倒置脈沖起作用。

利用OrCAD/PSpice 10.5的瞬態(tài)分析功能進(jìn)行仿真,瞬態(tài)分析(Time Domain Transient)是指在給定輸入激勵(lì)信號的作用下,計(jì)算電路輸出端的瞬態(tài)響應(yīng),其實(shí)質(zhì)就是計(jì)算時(shí)域響應(yīng)。設(shè)置瞬態(tài)分析參數(shù)從零時(shí)刻開始記錄數(shù)據(jù),到4 ms結(jié)束,最大步長為0.1 ms。進(jìn)行瞬態(tài)分析后,得到圖4所示的輸出電壓波形圖,其中類似于鋸齒波的是電容C2兩端的電壓,而方波則是555的輸出端Vout的電壓波形。

由圖4可見,電容C2存在自動(dòng)充放電過程。當(dāng)觸發(fā)脈沖到達(dá)時(shí),電源Vcc通過R2給電容C2充電,從0 V充電到約3.33 V之前,555定時(shí)器的輸出始終保持高電平,而一旦電容充電到3.33 V,555的輸出立即轉(zhuǎn)換為低電平,隨后電容C2開始從3.33 V迅速放電到0 V,此后又開始新的充放電過程。在555的輸出端Vout可以獲得周期性的矩形脈沖,而脈沖的寬度約為1.09 ms,與理論計(jì)算值1.1R2C2相近。并且輸出脈沖的寬度與輸入信號VPULSE的脈寬和幅度無關(guān)。

3 施密特觸發(fā)器仿真分析

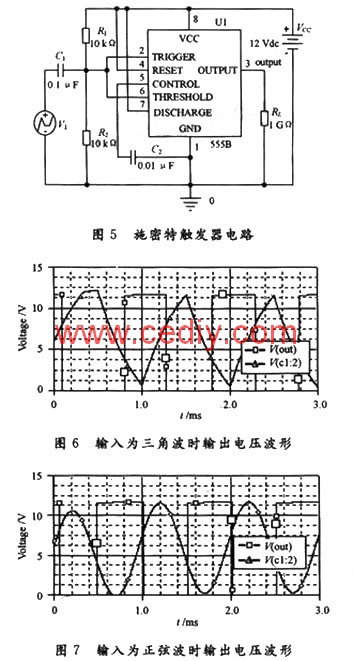

用555定時(shí)器構(gòu)成的施密特觸發(fā)器將閥值端和觸發(fā)端接在一起作為輸入端。運(yùn)行OrCAD/CaptureCIS,利用Schematics繪制的555定時(shí)器構(gòu)成的施密特觸發(fā)器電路如圖5所示。輸入信號Vi為三角波電壓源(VPWL),設(shè)置其參數(shù)為:

![]()

利用PSpice的瞬態(tài)分析功能進(jìn)行仿真,設(shè)置瞬態(tài)分析參數(shù)從零時(shí)刻開始記錄數(shù)據(jù),到3 ms結(jié)束,最大步長為1μs,得到555的輸出端Uout的電壓波形與輸入電壓波形如圖6所示。

由圖6可見,該電路能將輸入三角波轉(zhuǎn)換成方波輸出,當(dāng)輸入三角波電壓升高,輸出電平發(fā)生轉(zhuǎn)換時(shí)所對應(yīng)的門限電壓約為8 V,而當(dāng)輸入三角波電壓降低,輸出電平發(fā)生轉(zhuǎn)換時(shí)所對應(yīng)的門限電壓約為4 V,即上門限電壓與下門限電壓不同,輸入與輸出間具有遲滯特性。將輸入信號換成正弦信號后,得到輸入/輸出電壓的波形如圖7所示,依然表現(xiàn)出遲滯特性,且上門限電壓與下門限電壓仍分別為8 V和4 V,而這正是施密特觸發(fā)器電路的工作特性。仿真結(jié)果與理論計(jì)算結(jié)果的上門限電壓(2/3 Vcc)和下門限電壓(1/3 Vcc)相符。

4 多諧振蕩器仿真分析

多諧振蕩器是一種自激振蕩器,接通電源后不需要外加觸發(fā)信號便能自動(dòng)產(chǎn)生矩形脈沖。運(yùn)行OrCAD/Capture CIS,利用Schematics繪制的由555定時(shí)器構(gòu)成的多諧振蕩器電路如圖8所示。

電路由一個(gè)555B芯片、兩個(gè)電阻和兩個(gè)電容組成,通過電阻給電容C1充電、放電的過程來產(chǎn)生振蕩,從而輸出矩形脈沖。啟動(dòng)PSpice瞬態(tài)分析功能,觀察電容C1的端電壓和555的輸出端Vout的電壓,得到圖9所示的波形。由圖9中發(fā)現(xiàn)555定時(shí)器構(gòu)成的多諧振蕩器的輸出電壓Vout始終保持高電平,并沒有產(chǎn)生預(yù)期的振蕩。

4.1 OrCAD/PSpice中555多諧振蕩器不能起振的原因

分析可知,PSpice中555多諧振蕩器不能起振的原因在于起振源。實(shí)際振蕩電路之所以能自行起振是由于起振源的存在。實(shí)際振蕩電路的起振源主要由兩方面因素構(gòu)成:一是由振蕩電路晶體管內(nèi)部的噪聲和電路噪聲(電阻熱噪聲等)引起;二是由電路接通電源瞬間的沖擊電流引起。而直接利用PSpice對圖6電路進(jìn)行模擬仿真時(shí),PSpice會(huì)將電路中的555定時(shí)器、電阻、電容、電源等元件和電路的接通過程都理想化,即電路中不能產(chǎn)生任何噪聲和干擾。因此,沒有起振源,自然就不能產(chǎn)生振蕩。

4.2有效起振方法

經(jīng)查閱相關(guān)文獻(xiàn)[10],并經(jīng)多次實(shí)驗(yàn)驗(yàn)證,發(fā)現(xiàn)有多種方法可以使電路起振,現(xiàn)介紹其中兩種最簡單的方法供大家參考:

(1)給電容加初始值(IC值),本例中只將C1和C2的IC設(shè)為0。電容上的初始電壓,只是激發(fā)了振蕩電路的振蕩,沒有改變電路起振后的輸出波形,也沒有影響對振蕩電路起振特性的研究。

(2)在瞬態(tài)分析仿真設(shè)置(Simulstion Settings)中激活初始瞬態(tài)偏置點(diǎn)計(jì)算(Skip the Initial Transient Biaspoint Calculation)選項(xiàng),直接使用各元件的起始條件來作瞬態(tài)分析。

兩種方法都能順利使555多諧振蕩器發(fā)生起振,且持續(xù)地輸出脈沖波形。

4.3仿真結(jié)果與理論計(jì)算值比較

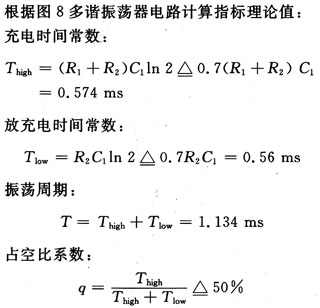

4.3.1計(jì)算指標(biāo)理論值

4.3.2 仿真值

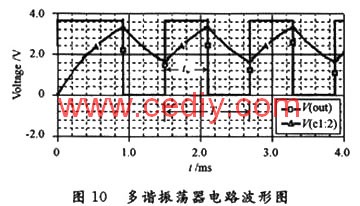

在OrCAD/PSpice中,采用前面提出的模擬振蕩電路的起振方法得到555振蕩電路輸出端的矩形脈沖電壓波形,如圖10所示。

由圖10可見,電源Vcc先通過R1,R2給C1充電,使電容C1從0 V充電到2Vcc/3,接著從2Vcc/3放電到Vcc/3,又再從Vcc/3充電到2Vcc/3,電容C1形成周期性的充放電過程,從而在555的輸出端Vout形成周期性的矩形脈沖波,構(gòu)成多諧振蕩器。由圖10所示,可得輸出矩形脈沖特性參數(shù):

仿真結(jié)果表明,輸出脈沖周期、占空比系數(shù)的仿真值與理論值基本相符。同時(shí)分析可知,其值只與電阻、電容值有關(guān),電容上的初始電壓,只是激發(fā)了振蕩電路的振蕩,并不會(huì)改變電路起振后的輸出波形,也不會(huì)影響對振蕩電路起振特性的研究。

5 結(jié) 語

利用OrCAD/PSpice 10.5對555定時(shí)器構(gòu)成的單穩(wěn)態(tài)觸發(fā)器、施密特觸發(fā)器和多諧振蕩器的特性進(jìn)行了仿真分析。同時(shí),針對仿真過程中多諧振蕩器不起振的問題進(jìn)行了討論,提出了振蕩電路的有效起振方法,仿真結(jié)果與理論計(jì)算值基本相符表明OrCAD/PSpice是電子線路設(shè)計(jì)人員必須掌握的基本工具之一。