數(shù)字預失真技術目前已經(jīng)在軟件實現(xiàn)上得到了初步的發(fā)展。目前一般的預失真技術采用軟件架構,使用數(shù)字信號處理器采集功放功率值,并分析其變化曲線,形成數(shù)據(jù)表格,并存儲。在以后的發(fā)射之前根據(jù)存儲的表格數(shù)據(jù)對發(fā)射功率進行預校正。該方法在實際工作中由于電磁環(huán)境變化、溫度變化、功放元器件老化、晶體頻率飄移等影響,使得預校正數(shù)據(jù)和真實校正數(shù)據(jù)存在較大的偏差,從而影響校正效果,甚至向反方向校正情況。軟件校正形成校正數(shù)據(jù)需要較長的時間,一般為幾十秒以上,使得實時校正難以實現(xiàn)。這樣使得軟件數(shù)字預失真技術的實用性降低,適用場合減少。

本文提出一種基于硬件的數(shù)字預失真校正系統(tǒng)的設計方法。采用TI公司的數(shù)字信號處理器DSP芯片C6727B和專用的數(shù)字預失真芯片GC5322實現(xiàn)預失真系統(tǒng)。文中重點介紹DSP和GC5322的軟硬件連接。硬件數(shù)字預失真系統(tǒng)由專用器件實現(xiàn)預失真處理,解決預失真的實時性問題;此外,進行預失真系統(tǒng)設計時,只需要實現(xiàn)對硬件芯片的配置,而無須編寫復雜的算法,簡化實現(xiàn)難度。

預失真技術和GC5322

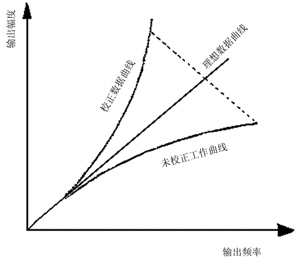

數(shù)字預失真(DPD,Digital Pre-Distortion)的工作原理就是預先產(chǎn)生非線性失真分量,去抵消功放中產(chǎn)生的非線性產(chǎn)物。一般的中頻預失真和射頻預失真,都是以發(fā)射系統(tǒng)最終輸出信號的三階交調(diào)功率比來衡量其性能指標。和模擬預失真以及前饋架構相比,數(shù)字預失真在提高效率、多載波應用、修正效果以及自適應方面具有很大的優(yōu)勢。對于零中頻架構的無線信號收發(fā)系統(tǒng),數(shù)字預失真在修正零中頻架構中的本振泄漏和鏡像抑制方面, 具有非常好的效果。功放預失真示意圖如圖1所示。

圖1 預失真示意圖

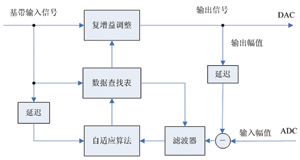

數(shù)字預失真系統(tǒng)的構成框圖如圖2所示。基帶輸入信號和存儲在數(shù)據(jù)查找表的預失真數(shù)據(jù)經(jīng)過復增益調(diào)整模塊處理,處理后的數(shù)據(jù)從DAC發(fā)送出去,完成預失真處理。同時,ADC開始采樣發(fā)射數(shù)據(jù),得到當前發(fā)射信號的功率值,經(jīng)過濾波器去抖動和噪聲后,送入自適應算法模塊,自適應算法模塊綜合基帶輸入信號和實際發(fā)射出去的信號,得到新的預失真數(shù)據(jù),并存儲到數(shù)據(jù)查找表中,從而完成實時的功放工作曲線校正。

圖2 數(shù)字預失真系統(tǒng)構成

從圖2中可以看出,預失真工作需要實時ADC采樣,并實時處理數(shù)據(jù)。工作量較大,由于一般的處理系統(tǒng)不能實時處理,只能在發(fā)射真實信號前,預先發(fā)射測試數(shù)據(jù),生成數(shù)據(jù)查找表,以后則以此表格數(shù)據(jù)修正功放工作曲線。顯然,這種方法很難實現(xiàn)實時處理,為了解決實時修正問題,TI公司推出GC5322預失真處理芯片。

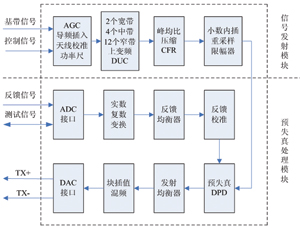

GC5322的內(nèi)部結(jié)構如圖3所示。信號發(fā)射模塊主要包括自動增益控制(AGC,Adaptive Gain Control)、導頻插入(Pilot Insertion)、功率尺(Power Meter)、峰均比壓縮(CFR,Crest Factor Reduction)、小數(shù)內(nèi)插重采樣(FFR,F(xiàn)ractional Farrow Re-sampler)以及限幅器(Circular Limiter)等模塊。發(fā)射模塊可以實現(xiàn)2個寬帶信號,例如2個10MHz帶寬的OFDMA信道;或者實現(xiàn)4個中帶信號,例如4個5MHz帶寬的WCDMA載波;或者實現(xiàn)12個窄帶信號,例如12個CDMA2000/TDSCDMA載波。

圖3 GC5322的內(nèi)部結(jié)構

預失真模塊是GC5322的最重要功能。該模塊的主要單元包括ADC/DAC接口、實數(shù)復數(shù)變換、帶反饋環(huán)的均衡器和校準器、預失真處理模塊、發(fā)射均衡器和混頻器等。

ADC轉(zhuǎn)換器采集功放輸出信號,轉(zhuǎn)換成數(shù)字信號并變換后成為反饋信號進入反饋環(huán)節(jié);反饋信號經(jīng)過一系列的下變頻處理,包括增益調(diào)整、頻率和相位歸一化處理等。其中還使用一個8階的反饋均衡器實現(xiàn)射頻到中頻的失真校正。

系統(tǒng)硬件結(jié)構

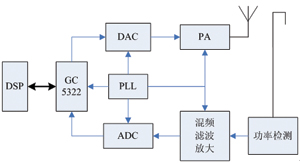

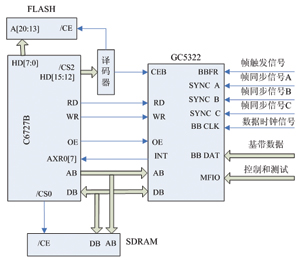

系統(tǒng)以數(shù)字信號處理器DSP芯片C6727B為核心單元,實現(xiàn)對整個過程的控制。C6727B是TI公司在C671x基礎上發(fā)展的浮點型DSP,其最高工作頻率達到350MHz。單個指令周期可以執(zhí)行6個浮點數(shù)據(jù)運算,最高達到2100MFLOPS;片內(nèi)具有256KB的RAM;片內(nèi)外設有EMIF、UHPI、音頻接口、dMAX、定時器以及IIC、SPI等接口。完全滿足對GC5322控制的要求。整個系統(tǒng)硬件結(jié)構如圖4所示。

圖4 系統(tǒng)硬件結(jié)構

圖4中,PLL模塊提供一個統(tǒng)一的時鐘信號到各個單元,尤其是GC5322、ADC、DAC以及功放和濾波放大電路需要統(tǒng)一的時鐘,否則系統(tǒng)預失真效果變差。C6727B和GC5322的連接是系統(tǒng)的重點,其硬件連接如圖5所示。

圖5 C6727B和GC5322的連接

圖5中使用C6727B的EMIF接口連接到GC5322的數(shù)據(jù)和地址總線,同時EMIF接口的總線還連接到系統(tǒng)中的SDRAM和FLASH存儲芯片。SDRAM是為了存儲DSP程序運行產(chǎn)生的中間變量;FLASH存儲程序,上電開始過程中由DSP讀取。此外,F(xiàn)LASH還可以存儲掉電不丟失的數(shù)據(jù),例如預失真校正數(shù)據(jù)。由于C6727B的EMIF接口只有兩個片選信號,其中CS0是專門用于SDRAM的選通信號,CS1統(tǒng)一給所有的異步外設,包括FLASH和GC5322。為此,使用譯碼電路完成多個異步外設的選擇,使用CPLD或者FPGA完成。GC5322的中斷信號必須連接到DSP,由于C6727B沒有專用的中斷信號,為此使用C6727B的音頻串口的AXR0[7]作為通用IO引腳,并配置成中斷信號。

系統(tǒng)軟件設計

系統(tǒng)軟件設計主要包括GC5322的初始化、DSP的初始化、EMIF接口設置、中斷使能、ADC/DAC設置等。系統(tǒng)初始化后,DSP判斷當前是否有數(shù)據(jù)需要發(fā)送,數(shù)據(jù)的讀寫通過判斷是否有掛起的中斷,該中斷由GC5322產(chǎn)生,一旦GC5322收到基帶數(shù)據(jù),將發(fā)出該中斷。無數(shù)據(jù)讀寫情況下,DSP將定期檢測GC5322的測試信號,以便確定GC5322在正常工作。也可以根據(jù)需要,將GC5322設置到低功耗狀態(tài)。

如果GC5322開始工作,則啟動ADC開始采樣,并控制時序?qū)DC采樣后數(shù)據(jù)傳輸?shù)紾C5322,GC5322根據(jù)設置進行預失真處理,從而校正DAC的輸出幅度,完成預失真處理。