VHDL是一種快速的電路設計工具,功能涵蓋 了電路描述、電路合成、電路仿真等三大電路設計工作。目前廣泛使用的軟件有Altera公司出品的MAX+PLUSII,Xinlinx公司的Foundation等。

VHDL語言中有兩種基本的語句命令:并行同 時語句命令以及順序語句命令。兩者之間最大的不同點是,并行同時語句命令就像是電路板的動作方 式,不論幾個命令,是一次且同時執(zhí)行,產(chǎn)生結果;順序語句命令類似一般的程序語言,如BASIC等的執(zhí)行方式,是一次一個命令,且依書寫方式由上而下地執(zhí)行。

并行同時語句命令主要有以下幾種表達方式: 直接設置語句(使用<=運算符)、條件式信號設置語句(When-Else)與選擇式信號設置語句(With-Select-When)等;

順序語句命令主要有以下幾種表達方式:Pro cess(過程)、If-Else(判斷比較)、Wait Until(等待)、Case-Is-When(描述選擇)等。

熟練而靈活地使用上述兩類命令,可以節(jié)省大 量的工作量,使程序簡單直觀、可讀性增強而且有利于提高程序的編譯執(zhí)行效率。

在數(shù)據(jù)通信過程中,同位器與同位檢查器常用 于數(shù)據(jù)糾錯。本文就以一個簡單偶同位產(chǎn)生器(Even Parity Bit Generator)真值表功能的實現(xiàn)方法來探討上述表達方式選擇問題,以及編程 過程中的注意事項。

2編程舉例

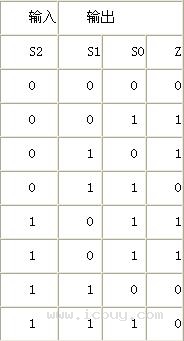

例:試設計VHDL程序完成如表1偶同位器的 真值表功能:

分析:由真值表可以看出,所要實現(xiàn)的是一個由三個數(shù)據(jù)位、一個同位位組成的偶同位產(chǎn)生器功 能。不難得出各位之間的簡單邏輯關系:P=S0S1S2 。但是本文的主要目的在于通過此例闡述如何靈活運用不同的基本表達式設置信號,因此 某些可能更加簡單的方法以及比較高級一點語句本文不予詳細討論。

解:(注:VHDL語言中使用“--”作為注釋符號)

library ieee; ①

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.

all;

ENTITY hf is --假設建立的芯片電路名稱以及保存后的文件名為“hf”;

Port(

s: in std_logic_vector(2 downto 0);

z: out std_logic --最后一個管腳定義命令后面,不可加分號;

);

end hf; --應該保證電路單元名稱與存盤的文件名一致,否則編譯時 出錯;

ARCHITECTURE a OF hf IS

Begin --以上是本例題解答過程中的公共部分,其后分別接各解法語句。

--******************************

--解法1:使用“hen -Else”表達方式②

z<=‘0’when (s="000") else --此語句只能將s的各個值分開寫,而不能寫成如下形式:

0’ when (s="011") else -- z<=‘0’

when (s="000" or s="011" or s="110" or s="111")

0’ when (s="110") else -- else ‘1’;

‘0’ when (s="111") else

‘1’ when (s="001") else

‘1’ when (s="001") else

‘1’ when (s="001") else

‘1’;

End a;

--解法2:使用揥ith -Select -When表達方式:

With s Select

z<=‘0’ when "000", --注意:除了最后一句的語句結束標志是分號外,其余各句均是逗號;

‘0’ when "011",

‘0’ when "110",

‘0’ when "111", -- when后選擇信號的值也只能分別列出,不可寫成組合條件形式。

‘1’ when others;

End a;

--解法3:使用“If-Else”表達方式:

Process--If-Else語句必須要與process配合使用;

Begin --Process中此句必不可少,否則編譯時出錯;

if s="000" or s="011" or s="110" or s="111" then --If后若為組合條件可用括號也可不用;

z<=‘0’;

else

z<=‘1’;

end if;

end process;

End a;

--解法4:使用“Case-Is-When”表達方式:

Process --“Case-Is-When”也只能與“Process”配合使用;

Begin

case s is

when "000"|"011"|"110"|"111" =>

--此處不能將“|”改成“or”但可以像解法1或解法1或解法2那樣將不同信號值分開寫;

when others=> --When句末尾是“=>”而不是逗號或者分號。

z<=‘1’;

end case;

end process;

End a;

備注:

(1) VHDL語言對所有字母的大小寫狀態(tài)不敏感,關鍵在于語句要正確規(guī)范。

(2) 在VHDL語言中,所使用的標點符號均是英文標點符號。凡是設置單個的信號值均需使用 單引號,而設置序列信號值必須使用雙引號。

(3) 請參看相關資料。

3討論

3.1本例能否使用“Wait Until”表達方式

很遺憾,類似此例的情況不能使用這個語 句。起碼筆者經(jīng)過多次嘗試之后均沒有通過編譯檢查。但是在使用此語句時應該注意以下事項:

(1) Wait Until 后面緊接的語句中不能出現(xiàn)序列信號的值,例如不能寫成如下形式:

Wait Until s="000" 也不能寫成組合條件形式(無論是否使用括號):

Wait Until s="000" or s="011" or s="110" or s="111"

(2) 使用此表達方式編寫程序代碼時,不能設定輸出引腳的初始值(通過第三方信號傳遞也不 行,但是在進行仿真時可以設定初始輸出值),不能寫成如下形式:

……

s: in std_logic;

……

Architecture a of hf is

Begin

z<=0; --就算z的初、終值通過兩個常量信號(如c=‘0’,d=‘1 ’)傳遞

Process --也不行,因為z不能規(guī)定兩個狀態(tài)。否則編譯時出錯;

Begin

wait until s=‘0’; --此處也不可以寫成序列信號形式,更不能使用邏輯運算符將其

z<=1; --寫成組合條件形式。Wait Until語句不支持組合條件。

End process;

END a;

3.2更簡單的實現(xiàn)方法

順序語句除了前文所敘的幾種基本表達方式以 外,還有一種循環(huán)語句:For-Loop;而并行同時語句也還有方塊語句(Block)、組件定義(Component)與組件映像(Port Map)等多個模塊化語法。而使用“For-Loop”編寫此類有重復動作需求的代碼無疑是最簡單直觀的:

……

Architecture a OF hf IS

Begin

Process(s)

Variable Tmp: Std_Logic;

Begin

Tmp:=‘0’;

For I In 0 to 2 Loop

Tmp:=Tmp XOR s(I);

End Loop;

Z<=s & Tmp;

End Process;

End a;

其他更加簡單的方法,限于篇幅與本文主 旨,在此就不予深究了。

4結束語

從以上不同解法可以看出,各種基本的表達

方式均有各自的特點:采用“When -Else”表達式(解法1)與“When -Else-When”表達式(解法2)編寫編寫代碼的優(yōu)點是直觀,但是代碼很多,欲實現(xiàn)復 雜的功能時工作量將會很大;采用“IF-Else”表達式(解法4)編寫代碼的優(yōu)點是直觀與簡單并舉,尤其是允許使用由邏輯運算符(And、Or等等)寫成的組合條件更是精簡了不少代碼。

另外,在編寫VHDL程序的過程中,不同的 表達式中,表示語句結束的符號是不同的,這一點在 我們學習和使用VHDL的過程中值得特別留意。

參考文獻

[1]盧毅、賴杰.VHDL與數(shù)字電路設計.北京:科學出版社,2001-04

[2]李廣軍、孟憲元.可編程ASIC設計及應用.成都:電子科技大學出版社.2000-10

[3]徐志軍等.大規(guī)模可編程邏輯器件及其應用.成都:電子科技大學出版社.2000-11

[4]何鋒 男,1979年出生,本科,研究方向為硬件描述語言設計,嵌入式系統(tǒng)開發(fā)。