DC/DC轉(zhuǎn)換器的設(shè)計頻率越來越快,目的是減小輸出電容和電感的尺寸,以節(jié)省電路板空間。正因如此,現(xiàn)在市場上出現(xiàn)越來越多工作在高輸入電壓下的DC/DC轉(zhuǎn)換器,其可提供線壓瞬態(tài)保護,更低的占空比使更快頻率下難以達到更低的電壓。許多電源集成電路制造廠商(IC)正在積極推銷高頻DC/DC轉(zhuǎn)換器,聲稱可以減少電路板空間占用。工作在1MHz或者2MHz下的DC/DC轉(zhuǎn)換器似乎是一個好主意,但開關(guān)頻率對電源系統(tǒng)產(chǎn)生的影響遠不止體積和效率兩方面。本文介紹了幾個設(shè)計實例,說明在高頻下開關(guān)存在的一些好處和挑戰(zhàn)。

應(yīng)用選擇

為了說明使用高開關(guān)頻率的權(quán)衡過程,我們設(shè)計了三個獨立電源,其工作頻率分別為100、300和750 kHz。所有這三種設(shè)計,輸入電壓均為48V,輸出電壓均為5V,而輸出電流均為1A。這些要求常用于為一個5-V邏輯USB,或者為其它DC/DC轉(zhuǎn)換器使用的中頻通用5-V總線供電,例如:低壓降穩(wěn)壓器等。若想建立一些設(shè)計限制,所選允許紋波電壓需為50mV,其約為輸出電壓的1%;同時選擇使用0.5 A的峰至峰電感電流。德州儀器TPS54160是一種集成MOSFET的2.5-MHz、60-V、1.5-A降壓DC/DC轉(zhuǎn)換器,用作所有設(shè)計的穩(wěn)壓器。TPS54160特有外部補償和快速可編程頻率,適用于一些高輸入電壓的工業(yè)應(yīng)用。

電感和電容選擇

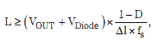

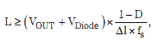

根據(jù)下列四個簡化公式,選擇每種情況的電感和電容:

電感選擇

![]() (1a)

(1a)

可重寫為:

(1b)

(1b)

其中,D(占空比)=5 V/48 V=0.104,且△I = 0.5 A峰至峰。

電容選擇

I= C x dv/dt (2a)

可重寫為:

(2b)

(2b)

其中,△I = 0.5 A峰至峰,且△V=50 mV。

就方程式2b而言,我們假設(shè)所選電容的等效串聯(lián)電阻(ESR)忽略不計,陶瓷電容便是如此。我們選擇陶瓷電容,用于所有三種設(shè)計,原因是其低電阻和小尺寸。方程式2b分子的乘數(shù)2表明DC偏壓相關(guān)電容下降情況,原因是大多數(shù)陶瓷電容的數(shù)據(jù)表中都沒有說明這一效應(yīng)。

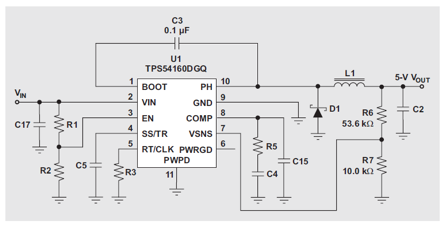

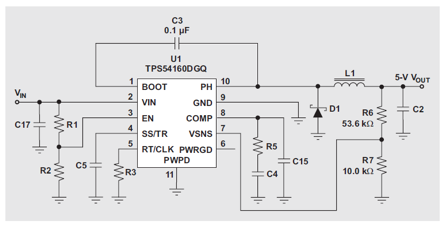

圖 1 TPS54160 參考示意圖

圖1所示電路用于評估實驗臺上每種設(shè)計的性能。示意圖中沒有值的一些組件,為設(shè)計中修改了的組件。輸出濾波器由L1和C2組成。所有三種設(shè)計的組件值都列舉在表1中,這些值的選擇是基于方程式1a到2b的結(jié)果。注意,每個電感的DC電阻隨頻率增加而減小。這是因為較少的匝數(shù)所需的銅長度更短。我們單獨為每個開關(guān)頻率設(shè)計了誤差放大器補償組件。選擇補償值的計算方法,超出了本文討論的范圍。

最小“導(dǎo)通”時間

最小可控“導(dǎo)通”時間限制是DC/DC轉(zhuǎn)換器IC的一個特點,其為脈寬調(diào)制(PWM)電路的最窄可達脈寬。在降壓轉(zhuǎn)換器中,開關(guān)周期期間功率MOSFET導(dǎo)通的時間百分比被稱作占空比,其等于輸出電壓與輸入電壓的比。使用TPS54160轉(zhuǎn)換器時,占空比為0.104(4 V/48 V),而數(shù)據(jù)表中列出的最小“導(dǎo)通”時間為130 ns。可控脈寬限制產(chǎn)生一個最小可達占空比,而用最小“導(dǎo)通”時間乘以開關(guān)頻率,我們可以輕松地計算出該占空比的大小。一旦知道了最小占空比,利用VIN乘以最小占空比,我們便可以計算出最低可達輸出電壓。最低輸出電壓同樣也受轉(zhuǎn)換器基準電壓的限制,使用TPS54160時其為0.8V。

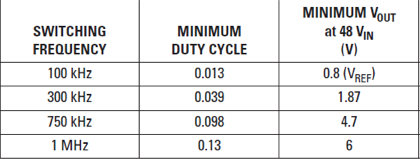

本例中,我們可以通過750-kHz開關(guān)頻率來產(chǎn)生一個5-V輸出電壓(參見表2)。但是,如果該頻率為1 MHz,則最低可能輸出電壓被限制為約6V;否則,DC/DC轉(zhuǎn)換器會跳過脈沖。替代方法是降低輸入電壓或者頻率。在選擇某個開關(guān)頻率以前,你最好是先查看DC/DC轉(zhuǎn)換器數(shù)據(jù)表,了解保證最小可控“導(dǎo)通”時間。

DC/DC轉(zhuǎn)換器的設(shè)計頻率越來越快,目的是減小輸出電容和電感的尺寸,以節(jié)省電路板空間。正因如此,現(xiàn)在市場上出現(xiàn)越來越多工作在高輸入電壓下的DC/DC轉(zhuǎn)換器,其可提供線壓瞬態(tài)保護,更低的占空比使更快頻率下難以達到更低的電壓。許多電源集成電路制造廠商(IC)正在積極推銷高頻DC/DC轉(zhuǎn)換器,聲稱可以減少電路板空間占用。工作在1MHz或者2MHz下的DC/DC轉(zhuǎn)換器似乎是一個好主意,但開關(guān)頻率對電源系統(tǒng)產(chǎn)生的影響遠不止體積和效率兩方面。本文介紹了幾個設(shè)計實例,說明在高頻下開關(guān)存在的一些好處和挑戰(zhàn)。

應(yīng)用選擇

為了說明使用高開關(guān)頻率的權(quán)衡過程,我們設(shè)計了三個獨立電源,其工作頻率分別為100、300和750 kHz。所有這三種設(shè)計,輸入電壓均為48V,輸出電壓均為5V,而輸出電流均為1A。這些要求常用于為一個5-V邏輯USB,或者為其它DC/DC轉(zhuǎn)換器使用的中頻通用5-V總線供電,例如:低壓降穩(wěn)壓器等。若想建立一些設(shè)計限制,所選允許紋波電壓需為50mV,其約為輸出電壓的1%;同時選擇使用0.5 A的峰至峰電感電流。德州儀器TPS54160是一種集成MOSFET的2.5-MHz、60-V、1.5-A降壓DC/DC轉(zhuǎn)換器,用作所有設(shè)計的穩(wěn)壓器。TPS54160特有外部補償和快速可編程頻率,適用于一些高輸入電壓的工業(yè)應(yīng)用。

電感和電容選擇

根據(jù)下列四個簡化公式,選擇每種情況的電感和電容:

電感選擇

![]() (1a)

(1a)

可重寫為:

(1b)

(1b)

其中,D(占空比)=5 V/48 V=0.104,且△I = 0.5 A峰至峰。

電容選擇

I= C x dv/dt (2a)

可重寫為:

(2b)

(2b)

其中,△I = 0.5 A峰至峰,且△V=50 mV。

就方程式2b而言,我們假設(shè)所選電容的等效串聯(lián)電阻(ESR)忽略不計,陶瓷電容便是如此。我們選擇陶瓷電容,用于所有三種設(shè)計,原因是其低電阻和小尺寸。方程式2b分子的乘數(shù)2表明DC偏壓相關(guān)電容下降情況,原因是大多數(shù)陶瓷電容的數(shù)據(jù)表中都沒有說明這一效應(yīng)。

圖 1 TPS54160 參考示意圖

圖1所示電路用于評估實驗臺上每種設(shè)計的性能。示意圖中沒有值的一些組件,為設(shè)計中修改了的組件。輸出濾波器由L1和C2組成。所有三種設(shè)計的組件值都列舉在表1中,這些值的選擇是基于方程式1a到2b的結(jié)果。注意,每個電感的DC電阻隨頻率增加而減小。這是因為較少的匝數(shù)所需的銅長度更短。我們單獨為每個開關(guān)頻率設(shè)計了誤差放大器補償組件。選擇補償值的計算方法,超出了本文討論的范圍。

最小“導(dǎo)通”時間

最小可控“導(dǎo)通”時間限制是DC/DC轉(zhuǎn)換器IC的一個特點,其為脈寬調(diào)制(PWM)電路的最窄可達脈寬。在降壓轉(zhuǎn)換器中,開關(guān)周期期間功率MOSFET導(dǎo)通的時間百分比被稱作占空比,其等于輸出電壓與輸入電壓的比。使用TPS54160轉(zhuǎn)換器時,占空比為0.104(4 V/48 V),而數(shù)據(jù)表中列出的最小“導(dǎo)通”時間為130 ns。可控脈寬限制產(chǎn)生一個最小可達占空比,而用最小“導(dǎo)通”時間乘以開關(guān)頻率,我們可以輕松地計算出該占空比的大小。一旦知道了最小占空比,利用VIN乘以最小占空比,我們便可以計算出最低可達輸出電壓。最低輸出電壓同樣也受轉(zhuǎn)換器基準電壓的限制,使用TPS54160時其為0.8V。

本例中,我們可以通過750-kHz開關(guān)頻率來產(chǎn)生一個5-V輸出電壓(參見表2)。但是,如果該頻率為1 MHz,則最低可能輸出電壓被限制為約6V;否則,DC/DC轉(zhuǎn)換器會跳過脈沖。替代方法是降低輸入電壓或者頻率。在選擇某個開關(guān)頻率以前,你最好是先查看DC/DC轉(zhuǎn)換器數(shù)據(jù)表,了解保證最小可控“導(dǎo)通”時間。

脈沖跳躍

DC/DC轉(zhuǎn)換器無法足夠快速地清除門驅(qū)動脈沖來維持理想占空比時,便會出現(xiàn)脈沖跳躍。電源會嘗試調(diào)節(jié)輸出電壓,但由于距離更遠的脈沖,紋波電壓會增加。由于存在脈沖跳躍,輸出紋波會呈現(xiàn)出分諧波成分,其可能出現(xiàn)噪聲問題。限流電路也可能不再正常工作,因為IC可能不響應(yīng)大電流峰值。一些情況下,如果控制器不正常工作,控制環(huán)路便可能會不穩(wěn)定。

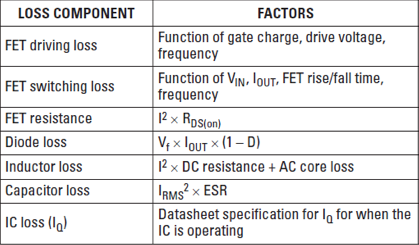

效率和功耗

DC/DC轉(zhuǎn)換器的效率,是進行電源設(shè)計時需要考慮的最重要屬性之一。低效率會轉(zhuǎn)換成高功耗,必須要在印刷電路板(PCB)上使用單獨的散熱器或者更多的銅,才能處理這些功耗。功耗也對電源上游器件提出了更高的要求。如表3所示,功耗共有幾個組成部分。

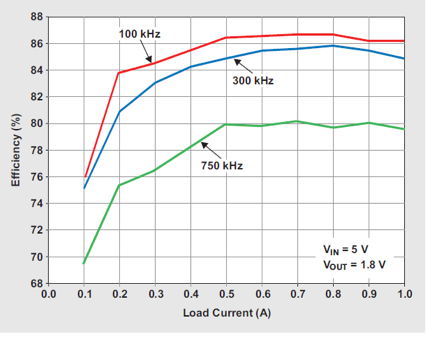

三個例子的重要損耗組成部分,來自于FET驅(qū)動損耗、FET開關(guān)損耗和電感損耗。FET電阻和IC損耗是一致的,因為所有三個設(shè)計中都使用了相同的IC。由于所有例子中都選擇了低ESR的陶瓷電容,因此電容損耗可以忽略不計。為了表明高頻開關(guān)的影響,我們對每個例子的效率都進行了測量,并將其顯示在圖2中。該圖清楚地表明,效率隨開關(guān)頻率增加而下降。若想提高所有頻率下的效率,需要尋找到一種全負載狀態(tài)下低漏到源“導(dǎo)通”電阻、低門電荷或者低靜態(tài)電流規(guī)范的DC/DC轉(zhuǎn)換器;或者尋找到一些具有更低等效電阻的電容和電感。

表 1 三個舉例電源設(shè)計的電容和電感選擇

表 2 130-ns最小“導(dǎo)通”時間的最小輸出電壓

表 3 功耗組成部分

圖 2 三個舉例頻率下 TPS54160 的效率

組件尺寸

表4列出了三種設(shè)計要求的總電路板面積,以及電容和電感的焊盤面積。電容或者電感的建議焊盤面積,稍稍大于單個組件本身,且三種設(shè)計舉例均使用了該面積。每個組件占用的面積相加(其包括IC、濾波器以及所有其它小型電阻器和電容的焊盤尺寸),然后將得到的結(jié)果乘以2倍(考慮到組件的間距),便得到總面積。100-kHz和750-kHz設(shè)計之間存在近250 mm2的總面積節(jié)省,從而使濾波器體積縮小50%,而板空間占用減少55%。但是,存在收益遞減規(guī)律,因為電容和電感值無法減少至零!換句話說,不斷推高頻率并不能夠一直減小總尺寸,因為你無法總是能夠在市場上買到這些尺寸適合且批量生產(chǎn)的電感和電容。注意,33-µH和15-µH電感占用相同的面積。存在這種可能性,是因為33-µH電感的高度為3.5 mm,而15-µH電感僅高2.4 mm。我們想通過這兩種電感來說明的觀點是:電感與體積成正比例關(guān)系。

表 4 組件尺寸和總面積要求

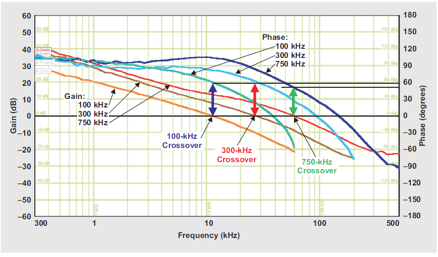

圖 3 100kHz、300 kHz和750 kHz 的波特圖

瞬態(tài)響應(yīng)

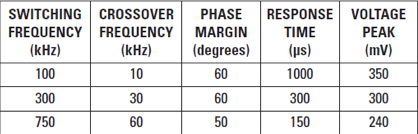

瞬態(tài)響應(yīng)是電源性能級別的一個較好指標。我們利用每種電源的波特圖來表明高開關(guān)頻率的對比情況(參見圖3)。如圖所示,每個電源的相位裕度在45°和55°之間,其表明瞬態(tài)響應(yīng)得到較好的抑制。交叉頻率約為開關(guān)頻率的1/8。使用快速開關(guān)DC/DC轉(zhuǎn)換器時,設(shè)計人員應(yīng)確保電源IC誤差放大器具有足夠的帶寬來支持高交叉頻率。TPS54160誤差放大器的單位增益頻寬一般為2.7 MHz。表5顯示了實際瞬態(tài)響應(yīng)時間以及電壓峰值過沖的相關(guān)值。開關(guān)頻率越高,過沖值便越是更低,原因是更寬的帶寬。

表 5 瞬態(tài)響應(yīng)

表 6 小占空比時抖動與“導(dǎo)通”時間之比

抖動考慮

高轉(zhuǎn)換比和更高頻率時,會存在噪聲問題。當(dāng)選擇某個高開關(guān)頻率時,設(shè)計人員應(yīng)考慮抖動和DC/DC轉(zhuǎn)換器的最小“導(dǎo)通”時間。當(dāng)占空比較小時,抖動噪聲便為開關(guān)脈沖的更大百分比。表6顯示了48-V到5-V轉(zhuǎn)換比時,抖動與“導(dǎo)通”時間之比。我們假設(shè),在該相位節(jié)點上存在0.5-V二極管壓降和20-ns抖動。

結(jié)論

設(shè)計高頻開關(guān)轉(zhuǎn)換器時,存在許多折中考慮。本文介紹的一些優(yōu)點包括更小的尺寸、更快的瞬態(tài)響應(yīng),以及更小的電壓過沖/欠沖。獲得這些優(yōu)點的代價是效率低和散熱多。但是,在挑戰(zhàn)性能極限的過程中同樣也存在許多陷阱,例如:脈沖跳躍和噪聲問題。在為高頻應(yīng)用選擇一種寬輸入電壓DC/DC轉(zhuǎn)換器以前,我們應(yīng)該首先查看制造廠商提供的數(shù)據(jù)表,以了解一些重要的規(guī)范,例如:最小“導(dǎo)通”時間、誤差放大器的增益帶寬、FET電阻以及FET開關(guān)損耗。在這些規(guī)范下運行良好的IC價格昂貴,但卻對得起它的價格;在設(shè)計人員擔(dān)心如何處理某個棘手的設(shè)計問題時,其更加易于使用。