1 引言

利用可見光成像與紅外成像傳感器實現(xiàn)實時目標成像跟蹤是精確制導武器及機載成像光電系統(tǒng)研究的核心技術,。伴隨著實戰(zhàn)環(huán)境日益復雜以及偽裝,、隱身等目標特性控制技術的飛速發(fā)展,機載實時圖像跟蹤系統(tǒng)的應用也日益廣泛與深入,。當跟蹤目標并非一般地面慢速目標,,而是其它快速運動目標?如:低空導彈、無人駕駛飛機等?時,,系統(tǒng)將要求現(xiàn)有機載實時圖像跟蹤系統(tǒng)具有更高的技術性能,。基于此,為了進一步提高現(xiàn)有機載光電跟蹤系統(tǒng)在實戰(zhàn)環(huán)境中,,針對復雜場景下快速運動目標實施實時跟蹤的魯棒性與穩(wěn)定性,,筆者提出以雙DSP和FP-GA為核心來構建主從式超高速并行處理體系的設計思想,并研究開發(fā)了基于雙DSP的新型柔性機載實時圖像跟蹤系統(tǒng),。一方面,,采用雙DSP體系結構實現(xiàn)系統(tǒng)任務的并行劃分使本系統(tǒng)具備極高的運算處理速度;另一方面,現(xiàn)場可編程邏輯器件FPGA的引入使系統(tǒng)的靈活性也得到極大的提高,。而將兩者結合可使本系統(tǒng)充分體現(xiàn)新一代機載實時圖像跟蹤系統(tǒng)更快速,、更精確、更靈活的特點,。

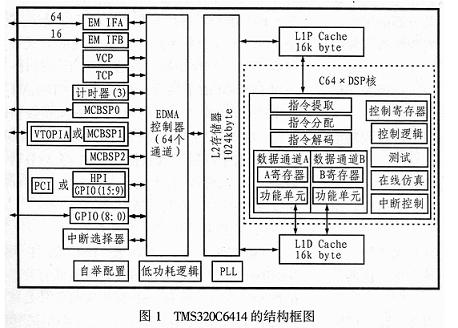

2 TMS320C6414的結構特點

美國德州儀器公司(TI)推出的新一代數字信號處理器TMS320C6414(以下簡稱C6414)的主頻為400MHz~700MHz,,其數據處理能力為3200MIPS~5760MIPS。該器件的結構框圖如圖1所示,。其主要特點如下:

(1)DSP內核采用超長指令字(VLIW)體系結構,,有8個功能單元、64個32bit通用寄存器,,一個時鐘周期可同時執(zhí)行8條指令,,運算能力可以達到5760MIPS;

(2)為了使數據能滿足超高速DSP內核的需求,C6414采用了兩級超高速緩沖存儲器,,即16k Byte的一級數據Cache,、16k Byte的一級程序Cache和1024k Byte的數據和程序統(tǒng)一內存。

(3)增加了直接處理打包數據指令,,可建立無縫的數據流,,以提高指令集的效率;

(4)每個功能單元在硬件上都增加了附加功能,從而增強了指令集的正交性,。

3 系統(tǒng)硬件設計

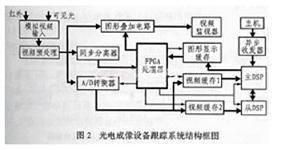

本光電成像跟蹤系統(tǒng)硬件平臺由六部分組成:圖像采集與預處理模塊,、同步分離模塊、FPGA邏輯控制模塊,、雙DSP+雙口RAM 圖像處理模塊,、異步通信模塊和圖形顯示模塊。其系統(tǒng)原理框圖如2所示,。從圖2可以知道:紅外探測器及可見光攝像儀輸出的模擬視頻信號經多路信號選擇芯片導入之后,,經箝位、放大,、濾波以及去同步頭等預處理后,,一路經A/D轉換器將模擬視頻轉換為8bit數字信號并導入片外視頻緩存1、2,,而后等待FPGA時序控制DSP外部中斷,,以便將全部緩存數據搬移到DSP片內的2級緩存,,再通過系統(tǒng)任務劃分實現(xiàn)數據重組,然后分別在主從DSP進行同步并行數據處理,,并將中間結果由主DSP綜合,,最后在完成后續(xù)運算后給出最終匹配結果。與此同時,,主DSP則通過寫圖形顯示緩存將目標匹配位置信息傳遞到外界;另一路模擬信號先導入同步分離器,,然后提取行場同步信號送交FPGA作為時基,以產生系統(tǒng)各級時序控制信號;第三路模擬信號送給圖形疊加電路作為輸入疊加信號之一,,當場正程來到時,,F(xiàn)PGA中斷控制并讀出圖形存儲器數據,同時在FPGA片內實現(xiàn)讀入數據的并/串轉換后移位輸出至圖形疊加電路,,此時兩路信號將會合送入視頻監(jiān)視器,,從而完成視頻圖像上圖形的顯示。整個系統(tǒng)工作期間,,每隔80ms主DSP還通過異步收發(fā)器與外部上位機進行串行通信,,以便系統(tǒng)能夠實時接收外部命令與目標參數,進而調整跟蹤系統(tǒng)的工作狀態(tài),。

3.1 圖像采集與預處理模塊

本系統(tǒng)中的多路選擇器件選用CD4052芯片。它能根據不同的工作場合來切換紅外/可見光視頻輸入;視頻預處理電路采用AD817進行視頻信號的放大,,以得到更清晰的信號來進行視頻處理;A/D芯片選用AD公司的AD9225,,輸出的8bit數字視頻信號送入74LS245進行數據鎖存。

3.2 同步分離模塊

系統(tǒng)采用一款專門的視頻同步分離器LM1881來從標準的負同步NTSC(PAL或SECAM)視頻信號中分離出有效的行/場同步信號,,并將其送入FPGA以產生系統(tǒng)的各級邏輯控制輸出,。

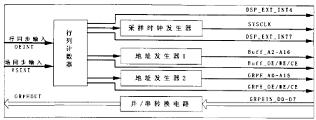

3.3 FPGA邏輯控制模塊

由于系統(tǒng)中各個芯片的功能相對獨立,要協(xié)調這些芯片的運作就需要一片起控制邏輯作用的可編程芯片,,為此,,筆者選用了ALTERAL公司的EPF10K30A,該芯片有246個用戶I/O口,、30000個典型門,、216個邏輯陣列塊、1728個邏輯單元?不僅能滿足系統(tǒng)的控制要求,,而且也可以為將來系統(tǒng)的功能擴展提供控制邏輯,。在這個光電跟蹤系統(tǒng)中,F(xiàn)PGA主要用來完成如下幾方面的工作:

(1)生成A/D采樣控制時鐘,,實現(xiàn)模擬視頻的正確采樣;

(2)提供字符圖形存儲器地址及片選/讀控制信號,,并在場正程到來時,控制圖形數據的讀出;

(3)提供視頻數據緩存器地址及片選/寫控制信號,,控制視頻數據的連續(xù)寫入;

(4)產生外部中斷4至雙DSP,,當數據寫滿視頻圖像高速緩存預定空間時,,控制主從DSP以將數據塊快速搬移至片內2級緩存;

(5)產生外部中斷7至主DSP,并在每個場逆程時刻來到時,,控制主DSP擦,、寫字符圖形存儲器數據;

(6)產生一并/串轉換電路,以將并行讀入的字符圖形數據串行移位輸出至圖形疊加電路,,從而實現(xiàn)“+”,、“□”圖形在視頻圖像上的疊加。

其FPGA內部結構框圖如圖3所示,。

圖3 FPGA內部結構框圖

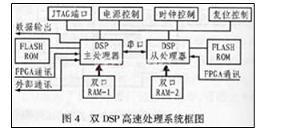

3.4 雙DSP+雙口RAM 圖像處理模塊

高速并行數字信號處理電路以雙DSP為并行運算處理核心單元,,并輔以雙口RAM來實現(xiàn)視頻圖像的高速緩存,從而完成大運算量的高速實時目標跟蹤處理任務,。該并行處理系統(tǒng)的組成與功能分述如下:

a. 視頻圖像高速緩存子模塊

為了實現(xiàn)圖像的實時采集與高速處理,,本系統(tǒng)用兩片雙口RAM組成相互獨立的視頻緩存,分別對應主/從DSP處理器,。設計時選用IDT公司的3.3V 異步雙口PRAM IDT70V657,,同時與DSP接口采用ASRAM方式。由于EMIF的ASRAM接口支持32Bit的數據接口,,因此,,利用IDT70V657構成不完全地址結構來存取數據能夠更好地實現(xiàn)8Bit鎖存數據與C6414的接口,而無須對DPRAM進行寬度擴展,。同時亦可減少DSP讀取外部數據的時間開銷,。

IDT70V657的大小是32K×36Bit?系統(tǒng)采用將兩個DPRAM各劃分為前后兩個半場的方式來實現(xiàn)存取數據時的乒乓切換。即在系統(tǒng)工作的任一時刻,,當對DPRAM前半場寫入數據時,,使DPRAM后半場向DSP讀出數據。當前半場寫滿視頻數據時,,由FPGA給DSP發(fā)出中斷信號,,以通知DSP讀出DPRAM前半場所寫入數據,同時,,將A/D轉換器的數據寫入DPRAM后半場緩沖空間,,如此反復進行來實現(xiàn)數據的讀出與寫入同步操作。

b. 雙DSP高速信號處理系統(tǒng)

TMS320C6414-600型DSP的主頻高達600MHz,,在超高速實時圖像處理領域有著非常出色的性能,。本系統(tǒng)的雙DSP高速實時信號處理系統(tǒng)就以2片C6414-600 DSP芯片為核心組成鄰域圖像并行處理機,并通過系統(tǒng)任務的劃分與分解實現(xiàn)同步并行運算處理,。其系統(tǒng)框圖如圖4所示,。

在本系統(tǒng)中,主DSP完成的主要功能如下:

(1) 實現(xiàn)外部緩存數據到片內的搬移,,為DSP高速批處理開辟片內二級緩存;

(2) 實現(xiàn)與外部上位機的即時通訊,,接收外部命令與目標參數;

(3) 實現(xiàn)與從DSP的即時通信,,下傳命令字與目標參數以及獲取中間結果;

(4) 運行系統(tǒng)跟蹤算法,承擔系統(tǒng)核心運算任務的一半;

(5) 與FPGA建立即時通信,,實現(xiàn)系統(tǒng)程序模塊的調度與協(xié)調;

從DSP完成的主要功能是:

(1) 實現(xiàn)外部緩存數據到片內的搬移,,為DSP高速批處理開辟片內二級緩存;

(2)運行系統(tǒng)跟蹤算法,承擔系統(tǒng)核心運算任務的一半;

(3)實現(xiàn)與主DSP的即時通信,,上傳匹配運算中間結果;

(4)與FPGA建立即時通信,,實現(xiàn)系統(tǒng)程序模塊的調度與協(xié)調。

雙DSP處理系統(tǒng)的柔性特色體現(xiàn)在:可依據實時環(huán)境需要加載不同的跟蹤算法來實現(xiàn)目標跟蹤,。算法運行之初,兩片C6414-600都在FPGA的控制下,,通過EMIFA口以EDMA方式,分若干次,依系統(tǒng)跟蹤算法而定?將外部視頻緩存中的數據(一場圖像)依次讀入DSP的L2片內緩存中;算法運行之后,主從DSP則通過McBSP直接互接來實現(xiàn)雙DSP間的高速同步通信?以便交換數據處理結果,。

系統(tǒng)設計中,,F(xiàn)lash ROM選用AMD公司的AM29LV800(1M×8Bit)來把FLASH映射到DSP統(tǒng)一編址地址空間EMIFB口的CE1空間。當系統(tǒng)上電復位后,,該地址空間為首先引導區(qū)域,,這樣即可將應用程序代碼加載到片內高速執(zhí)行,從而實現(xiàn)系統(tǒng)的脫機運行,。

3.5 異步通信模塊

本系統(tǒng)與外部上位機的異步通信主要通過主DSP的McBSP,。C6000的McBSP是一個功能非常強大的標準串口,支持全雙工串行通信,它的雙緩沖數據寄存器允許連續(xù)的數據流,可與多達128個通道進行收發(fā)通信,。通過對McBSP的SPCR,、RCR、XCR,、SRGR、PCR寄存器的配置可實現(xiàn)系統(tǒng)通信時收發(fā)數據的幀同步和時鐘同步,。

由于外部上位機的通訊機制是RS422標準,,而DSP與外部通信只提供RS232接口,故應采用一片MAX3074芯片來實現(xiàn)RS422到RS232的轉換,。MAX3074是MAXIM公司生產的一款專門用于RS422/485至RS232的轉接芯片,,采用3.3V供電,這與C6000 DSP 外圍供電電壓一致,,連接非常方便,,不再需要多余的電壓適配器。另一方面,,由于McBSP為同步串口,,為了實現(xiàn)McBSP與RS232的無縫連接,可通過軟件加入發(fā)送擴展算法與接收壓縮算法,,從而實現(xiàn)DSP與上位機異步串口通信協(xié)議的握手,。

3.6 圖形顯示模塊

該模塊由圖形存儲器,、圖形疊加電路和視頻監(jiān)視器組成。圖形存儲器選擇IDT公司的70V08(64K×8Bits)DPRAM來存儲標識目標匹配位置的圖形數據,。圖形疊加電路用于實現(xiàn)視頻與圖形的疊加,,并最終由視頻監(jiān)視器顯示疊加結果。

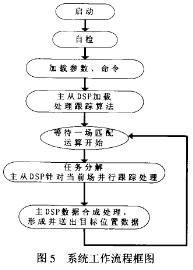

4 系統(tǒng)工作流程

本系統(tǒng)的軟件工作模式包括復位和初始化模式,、運行模式,、系統(tǒng)維護模式,可由系統(tǒng)程序來控制三種模式的切換,。

在復位和初始化模式下,,系統(tǒng)啟動后將由主從DSP同步實現(xiàn)程序搬移,把程序代碼搬移到片內并運行系統(tǒng)程序,從而初始化主從DSP的運行環(huán)境并設置相關參數,。

運行模式下,,雙DSP一方面獨立響應并處理FPGA中斷、運行核心跟蹤算法并實現(xiàn)子系統(tǒng)內的進程調度;另一方面通過主從DSP串口間的互連響應中斷以及主DSP串口與遠程主機的通訊等功能來實現(xiàn)雙DSP子系統(tǒng)間和雙DSP系統(tǒng)與外部主機的進程調度,。

系統(tǒng)維護模式下,,主從DSP在進行系統(tǒng)自檢后,可由遠程主機通過RS422接口與主DSP進行通訊,,以實現(xiàn)程序的更新下載和參數修改等功能,。圖5為系統(tǒng)軟件工作流程框圖。

5 結束語

筆者對該系統(tǒng)的實時性進行了仿真測試,,結果分析表明:

(1)單DSP只能實現(xiàn)開窗搜索,,高速場合下一旦目標逃逸搜索區(qū),將導致目標丟失;而本系統(tǒng)能夠實現(xiàn)基于整場搜索的大運算量高速處理,,從而加大了被跟蹤目標搜索區(qū)的動態(tài)范圍,,避免了目標丟失情況的發(fā)生,進一步提高了實時跟蹤的可靠性,。

(2)傳統(tǒng)單DSP系統(tǒng)一般只能實現(xiàn)基于一幀的匹配性能,,而本系統(tǒng)可實現(xiàn)基于逐場的跟蹤匹配,進一步提高了跟蹤系統(tǒng)的實時性,。

(3)根據實際場合的需要,,本系統(tǒng)可通過軟件選擇加載跟蹤算法,從而極大的增強了系統(tǒng)的通用性和易維護性,,體現(xiàn)出柔性處理系統(tǒng)的特色,。

由此可見,雙DSP柔性處理系統(tǒng)為復雜場景下快速移動目標的高速識別與跟蹤提供了一個有效的實現(xiàn)方案,同時也為機載實時圖像跟蹤系統(tǒng)提供了新的高速處理平臺,。