目前數(shù)字電子技術(shù)基礎(chǔ)課程的實(shí)驗(yàn)內(nèi)容包括驗(yàn)證性實(shí)驗(yàn)、綜合性實(shí)驗(yàn)、設(shè)計(jì)性實(shí)驗(yàn)三部分,每一部分實(shí)驗(yàn)內(nèi)容安排的側(cè)重點(diǎn)不同。比如設(shè)計(jì)性實(shí)驗(yàn)的關(guān)鍵是設(shè)計(jì),要求學(xué)生依據(jù)設(shè)計(jì)要求,設(shè)計(jì)合理的實(shí)驗(yàn)電路,并選擇器件、安裝調(diào)試完成實(shí)驗(yàn)內(nèi)容。從教學(xué)實(shí)踐來(lái)看,多數(shù)學(xué)生能夠順利完成實(shí)驗(yàn)要求,但解決問(wèn)題的思路單一,設(shè)計(jì)過(guò)程靈活性差,不注意創(chuàng)新思維能力的鍛煉。這就要求教師在合理安排實(shí)驗(yàn)內(nèi)容的同時(shí),不斷通過(guò)各種途徑,引導(dǎo)學(xué)生拓寬知識(shí)面,創(chuàng)新思維方式,對(duì)待同一問(wèn)題,積極探索多種解決問(wèn)題的路徑。組合邏輯電路的設(shè)計(jì)多種多樣,筆者選擇一種奇偶校驗(yàn)電路實(shí)現(xiàn)進(jìn)行詳細(xì)闡述。

奇偶校驗(yàn)電路在組合邏輯電路的分析與設(shè)計(jì)中具有一定的典型性和實(shí)用性,熟悉判奇電路的邏輯功能及電路實(shí)現(xiàn),有助于加深對(duì)組合邏輯電路的理解與掌握。以判奇電路實(shí)現(xiàn)為例,分別討論了用門電路、譯碼器、數(shù)據(jù)選擇器的多種實(shí)現(xiàn)方案, 用實(shí)例說(shuō)明了組合邏輯電路設(shè)計(jì)的靈活性與多樣性。

1 三輸入變量判奇電路的真值表及表達(dá)式

對(duì)于三輸入變量的判奇問(wèn)題, 設(shè)其輸入變量分別用A、B、C 表示,輸出函數(shù)用F 表示。當(dāng)輸入變量的取值組合中有奇數(shù)個(gè)1 時(shí),輸出函數(shù)值為1;當(dāng)輸入變量的取值組合中1 的個(gè)數(shù)為偶數(shù)時(shí),輸出函數(shù)值為0,依據(jù)這種邏輯關(guān)系可列寫出三輸入變量判奇電路的真值表如表1 所示。

表1 三輸入判奇電路的真值表

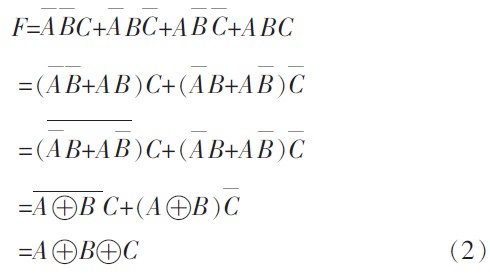

由真值表1 可見(jiàn),有4 組輸入變量取值組合使輸出函數(shù)值為1,即分別為![]() 。所以,三輸入變量判奇邏輯問(wèn)題的輸出函數(shù)表達(dá)式為:

。所以,三輸入變量判奇邏輯問(wèn)題的輸出函數(shù)表達(dá)式為:

![]()

2 采用門電路實(shí)現(xiàn)三輸入變量判奇電路

門電路實(shí)現(xiàn)三輸入變量判奇電路的方法有很多, 文中列舉如下。

方法一:與或表達(dá)式(1)可用反相器、與門、或門直接實(shí)現(xiàn),作其電路圖如圖1 所示。

圖1 采用反相器、與門、或門實(shí)現(xiàn)。

用反相器、與門、或門實(shí)現(xiàn)三輸入判奇電路,其特點(diǎn)是表達(dá)式基本沒(méi)有變化,實(shí)現(xiàn)途徑簡(jiǎn)單明了,缺點(diǎn)是連線較多,電路復(fù)雜。

方法二:與或表達(dá)式(1)也可用反相器、與或門實(shí)現(xiàn),電路圖如圖2 所示。

圖2 采用反相器、與或門實(shí)現(xiàn)

由上述兩種不同門電路設(shè)計(jì)方法實(shí)現(xiàn)三輸入變量判奇電路可以得出,方法一和方法二雖然實(shí)現(xiàn)邏輯簡(jiǎn)單,但是都連線太多,浪費(fèi)資源。

同一邏輯問(wèn)題的邏輯函數(shù)表達(dá)式是不具備唯一性的。對(duì)三變量輸入判奇邏輯問(wèn)題的輸出函數(shù)表達(dá)式(1)進(jìn)行變換如下所示:

方法三:根據(jù)上述表達(dá)式(2)得出,三輸入變量判奇電路也可采用異或門實(shí)現(xiàn),其電路如圖3 所示。

圖3 采用異或門實(shí)現(xiàn)

由圖3 所示電路可見(jiàn),對(duì)于三輸入變量判奇的邏輯問(wèn)題,當(dāng)采用異或門實(shí)現(xiàn)時(shí),相比于方法一和方法二,電路中的連線較少,電路簡(jiǎn)單明了,實(shí)現(xiàn)簡(jiǎn)單。

對(duì)于異或邏輯表達(dá)式也可以稍作變換得出:

![]()

即一個(gè)異或門可用4 個(gè)2 輸入與非門實(shí)現(xiàn), 所以三輸入判奇電路又可用8 個(gè)2 輸入與非門實(shí)現(xiàn),電路如圖4 所示。

圖4 采用2 輸入與非門實(shí)現(xiàn)

3 采用74138 譯碼器實(shí)現(xiàn)三輸入變量判奇電路

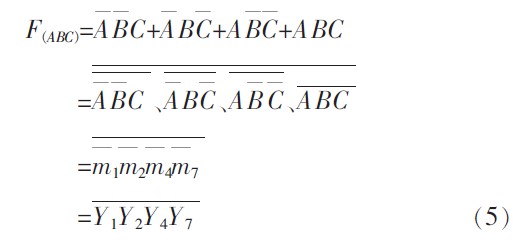

譯碼器的電路結(jié)構(gòu)表明,在適當(dāng)?shù)倪B接條件下,譯碼器實(shí)際上是一個(gè)最小項(xiàng)發(fā)生器。依據(jù)邏輯代數(shù)的基本原理,任何一個(gè)邏輯函數(shù)表達(dá)式都可以變換為最小項(xiàng)表達(dá)式。因此,譯碼器與適當(dāng)?shù)拈T電路結(jié)合,可以實(shí)現(xiàn)給定的邏輯函數(shù)。對(duì)于三輸入變量的判奇問(wèn)題, 利用74138 譯碼器并配備適當(dāng)?shù)拈T電路亦可實(shí)現(xiàn)。由74138 譯碼器的功能表可知:

在(4)式中,當(dāng)G1=1,G2A=G2B=0 時(shí),有Yi=m軓i.如果把給定邏輯函數(shù)的輸入變量連與74138 譯碼器的A2A1A0輸入端相連接,比如取A2A1A0=ABC,則邏輯函數(shù)表達(dá)式(1)可變換為:

(5)式表明,三輸入變量判奇電路可以利用74138 譯碼器和四輸入與非門實(shí)現(xiàn),其電路如圖5 所示。

圖5 三輸入判奇電路的譯碼器和與非門實(shí)現(xiàn)

4 采用數(shù)據(jù)選擇器實(shí)現(xiàn)三輸入變量判奇電路

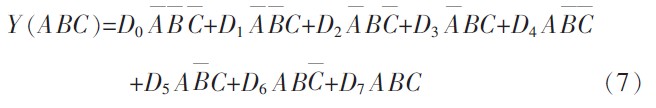

數(shù)據(jù)選擇器的輸出與輸入關(guān)系的一般表達(dá)式為:

![]()

(式)6 中EN 是輸入使能控制信號(hào),mi是地址輸入變量構(gòu)成的最小項(xiàng),Di表示數(shù)據(jù)輸入。當(dāng)使能輸入信號(hào)有效時(shí),如果把數(shù)據(jù)輸入作為控制信號(hào),則當(dāng)Di= 1 時(shí),其對(duì)應(yīng)的最小項(xiàng)mi在表達(dá)式中出現(xiàn),當(dāng)Di= 0 時(shí),其對(duì)應(yīng)的最小項(xiàng)mi在表達(dá)式中就不出現(xiàn)。所以,數(shù)據(jù)選擇器的輸出表達(dá)式事實(shí)上是受數(shù)據(jù)輸入端控制的最小項(xiàng)之和表達(dá)式。考慮到任何一個(gè)邏輯函數(shù)表達(dá)式都可以變換為最小項(xiàng)表達(dá)式,因此,只要邏輯函數(shù)的輸入變量接到數(shù)據(jù)選擇器的地址選擇輸入端,就可以實(shí)現(xiàn)組合邏輯函數(shù)。利用數(shù)據(jù)選擇器這一特點(diǎn),亦可實(shí)現(xiàn)三輸入變量的判奇電路。

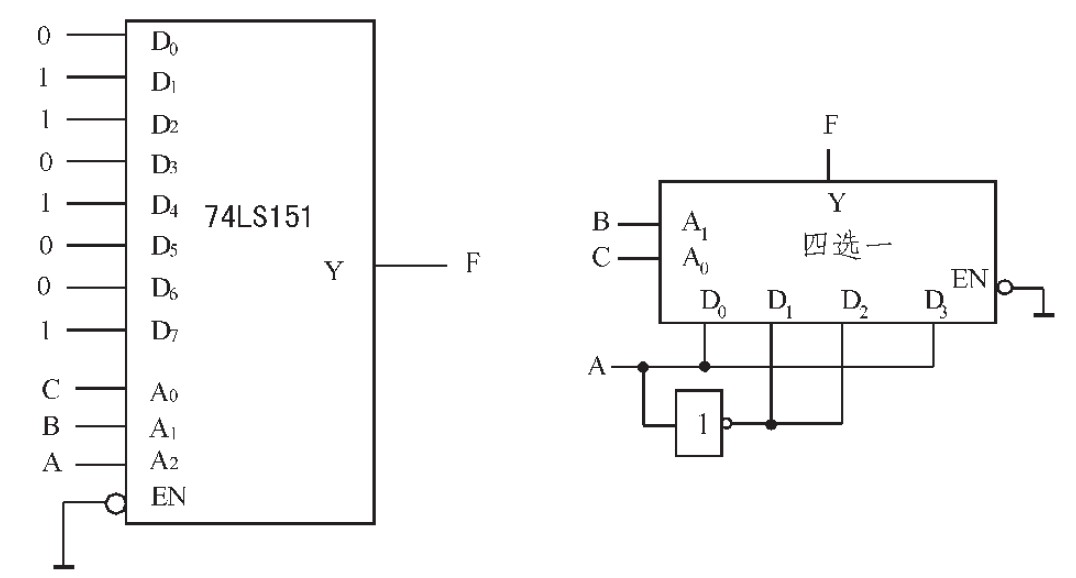

如果選用八選一數(shù)據(jù)選擇器實(shí)現(xiàn)三輸入變量的判奇電路,此時(shí),函數(shù)的輸入變量個(gè)數(shù)與數(shù)據(jù)選擇器的地址變量個(gè)數(shù)相同。如果令A(yù)2A1A0 =ABC,使能輸入端接地,則(6)式變?yōu)椋?/p>

比較(1)與(7)式,可見(jiàn)只要D0=D3=D5=D6=0,D1=D2=D4=D7=1,則有Y=F.由此可作電路圖如圖6(a)所示。也可以采用四選一數(shù)據(jù)選擇器實(shí)現(xiàn),其電路之一如圖6(b)所示。

圖6 采用數(shù)據(jù)選擇器實(shí)現(xiàn)

5 采用反函數(shù)取非的方式設(shè)計(jì)判奇電路

在上述的判奇電路設(shè)計(jì)中, 是按照輸出函數(shù)的原函數(shù)進(jìn)行分析。邏輯代數(shù)的基本定理表明:F=F ,由此可得出組合邏輯電路設(shè)計(jì)的另一途徑,即先求出F軈 再反相。這樣做看起來(lái)是麻煩一點(diǎn),但對(duì)于某些應(yīng)用場(chǎng)合,設(shè)計(jì)過(guò)程并不增加麻煩,反而提供了解決問(wèn)題的一種途徑。對(duì)于三輸入變量的判奇電路,在真值表1 中對(duì)0 寫出F 的反函數(shù)有:

![]()

對(duì)式(8)兩邊取反有:

![]()

對(duì)于(9)式,可采用反相器、與或非門實(shí)現(xiàn),其電路如圖7所示。(9)式同樣可采用74138 譯碼器或者數(shù)據(jù)選擇器實(shí)現(xiàn)。

圖7 采用反相器及與或非門實(shí)現(xiàn)

6 結(jié)束語(yǔ)

設(shè)計(jì)性實(shí)驗(yàn)的關(guān)鍵在于設(shè)計(jì)過(guò)程, 正確的設(shè)計(jì)以熟悉基本知識(shí)為前提。對(duì)于具體的應(yīng)用問(wèn)題,由于組合邏輯電路元器件的多樣性,為實(shí)現(xiàn)途徑提供了多種可能的選擇,文中以三輸入變量的判奇邏輯問(wèn)題為例, 分析討論了多種電路實(shí)現(xiàn)的途徑,給出了7 種電路實(shí)現(xiàn)方案,用實(shí)例說(shuō)明了邏輯電路設(shè)計(jì)的靈活性與多樣性。

三輸入變量判奇邏輯電路的設(shè)計(jì)僅僅是個(gè)例, 通過(guò)其設(shè)計(jì)途徑的討論在其他邏輯電路設(shè)計(jì)中舉一反三是目的。利用文中提出的設(shè)計(jì)思路,同樣可以設(shè)計(jì)全加器、全減器等其它組合邏輯電路,開(kāi)闊組合邏輯電路設(shè)計(jì)的視野,培養(yǎng)創(chuàng)新思維能力,指導(dǎo)數(shù)字邏輯電路的設(shè)計(jì)與實(shí)驗(yàn)。