摘要:給出一種具有多種觸發(fā)功能的可編程高速數(shù)據(jù)采集模塊的設(shè)計(jì)方法。模塊可以動(dòng)態(tài)設(shè)置觸發(fā)窗長(zhǎng)度,、觸發(fā)點(diǎn)電平,、觸發(fā)極性和觸發(fā)模式;依據(jù)觸發(fā)字與存儲(chǔ)在FIFO中的A/D轉(zhuǎn)換數(shù)據(jù)比較確定觸發(fā)位置,,并根據(jù)設(shè)置的預(yù)觸發(fā)深度實(shí)現(xiàn)對(duì)A/D轉(zhuǎn)換數(shù)據(jù)的存儲(chǔ)和傳輸,。由于觸發(fā)電路采用了全數(shù)字化設(shè)計(jì),與采用模擬電平比較器實(shí)現(xiàn)觸發(fā)電平比較相比,,無需硬件改動(dòng),,可以靈活地配置觸發(fā)方式,同時(shí)也降低了系統(tǒng)調(diào)試難度,。

關(guān)鍵詞:高速數(shù)據(jù)采集,;數(shù)字電路;觸發(fā)窗,;先進(jìn)先出存儲(chǔ)器

引言

在數(shù)據(jù)采集的過程中,,為了不漏掉任何一個(gè)既定特征的信號(hào),A/D轉(zhuǎn)換器必須不斷地采集數(shù)據(jù),。但是由于存儲(chǔ)器容量的限制,,不可能無限制地采集并存儲(chǔ)數(shù)據(jù)。如何使模塊能自動(dòng)檢測(cè),、采集并存儲(chǔ)有效數(shù)據(jù)呢?觸發(fā)技術(shù)的引入可以解決這一問題,。觸發(fā)是為了有效地觀測(cè)信號(hào),當(dāng)被測(cè)信號(hào)滿足觸發(fā)條件時(shí),,啟動(dòng)一次數(shù)據(jù)采集,使用戶在屏幕上能觀測(cè)到滿足觸發(fā)條件的波形,。

觸發(fā)電路在以往的設(shè)計(jì)中,,多采用電平比較器,其缺點(diǎn)是:采用的分立元件多,,不利于模塊移植和速度的提升,,同時(shí)觸發(fā)方式多樣化配置也受到硬件限制,不具備智能化特點(diǎn),。本模塊基于高速A/D轉(zhuǎn)換器和FPGA,,提出了一種全數(shù)字化的多種觸發(fā)功能的高速數(shù)字采集設(shè)計(jì)方案。模塊接口易于移植,,采集頻率高達(dá)50 MHz,,具有多種可編程觸發(fā)功能,采用的觸發(fā)窗技術(shù)進(jìn)一步保證了采樣存儲(chǔ)數(shù)據(jù)的正確性和有效性。

1 高速數(shù)據(jù)采集模塊結(jié)構(gòu)

高速數(shù)據(jù)采集模塊由FPGA存儲(chǔ)控制,、傳輸電路和AD9057數(shù)據(jù)采集部分構(gòu)成,。其中FPGA為此次模塊設(shè)計(jì)的重點(diǎn)。多種觸發(fā)功能的高速數(shù)據(jù)采集模塊結(jié)構(gòu)框圖如圖1所示,。采用Cyclone系列EP1C6Q240C8型號(hào)的FPGA控制芯片,,其Bank4 I/O口與AD9057相連,有源晶振提供了50 MHz的時(shí)鐘頻率,。

此模塊通過通信接口動(dòng)態(tài)設(shè)置觸發(fā)極性,、觸發(fā)模式、觸發(fā)窗長(zhǎng)度,、觸發(fā)點(diǎn)電平,,觸發(fā)極性可選上升沿觸發(fā)rising_edge和下降沿觸發(fā)falling_edge兩種。觸發(fā)模式可分為前觸發(fā)pre_trigger,、中間觸發(fā)mid_trigger,、后觸發(fā)post_trigger三種模式。觸發(fā)窗長(zhǎng)度設(shè)置為0~100的整數(shù),,觸發(fā)點(diǎn)電平可設(shè)置為0~255的整數(shù),。

當(dāng)連接通信接口的外部顯示控制界面設(shè)置好觸發(fā)極性、觸發(fā)模式,、觸發(fā)窗長(zhǎng)度,、觸發(fā)點(diǎn)電平時(shí),開始啟動(dòng)采集命令,,包裝好的40位數(shù)據(jù)流將被發(fā)送到FPGA,;FPGA接收到40位數(shù)據(jù)后,迅速分離成5個(gè)8位數(shù)據(jù),,即觸發(fā)極性,、觸發(fā)模式、觸發(fā)窗長(zhǎng)度,、觸發(fā)點(diǎn)電平和采集啟動(dòng)信號(hào),,利用FIFO存儲(chǔ)器先進(jìn)先出的特性以及對(duì)AD9057的控制時(shí)序,配合觸發(fā)信號(hào)存儲(chǔ)A/D數(shù)據(jù),;當(dāng)采樣完成后,,F(xiàn)IFO中的數(shù)據(jù)可以被發(fā)送到外部的顯示控制界面直觀地顯示出來。

1.1 觸發(fā)信號(hào)的產(chǎn)生

傳感器探測(cè)和感知的模擬信號(hào)一般都帶有一定干擾,,如果僅憑一個(gè)觸發(fā)點(diǎn)來決定觸發(fā)的位置則很難控制,,在本模塊觸發(fā)位置的設(shè)計(jì)中采用了三點(diǎn)觸發(fā)窗技術(shù),觸發(fā)窗的設(shè)置可以有效地屏蔽模擬信號(hào)的抖動(dòng),,使模塊正常運(yùn)行,。

觸發(fā)極性triggerpolar有上升沿觸發(fā)rising_edge和下降沿觸發(fā)falling_edge兩種模式,,在這兩種觸發(fā)極性下,觸發(fā)信號(hào)上升沿表示模塊開始存儲(chǔ)A/D轉(zhuǎn)換數(shù)據(jù),。模塊設(shè)置了觸發(fā)字1和觸發(fā)字2,,觸發(fā)字1為觸發(fā)點(diǎn)加上觸發(fā)窗長(zhǎng)度,如果結(jié)果小于255則觸發(fā)字為兩者相加結(jié)果,,否則為255,;觸發(fā)字2為觸發(fā)點(diǎn)減去觸發(fā)窗長(zhǎng)度,如果結(jié)果大于0則觸發(fā)字為兩者相減結(jié)果,,否則為0,。

圖2是下降沿觸發(fā)信號(hào)產(chǎn)生圖。圖中模塊開始采樣時(shí),,A/D轉(zhuǎn)換數(shù)據(jù)與觸發(fā)字1和觸發(fā)字2不斷地比較,,當(dāng)A/D數(shù)據(jù)大于觸發(fā)字1時(shí),觸發(fā)信號(hào)輸出為低電平,;此后A/D數(shù)據(jù)與觸發(fā)字2比較,,當(dāng)A/D數(shù)據(jù)小于觸發(fā)字2,觸發(fā)信號(hào)輸出高電平,。

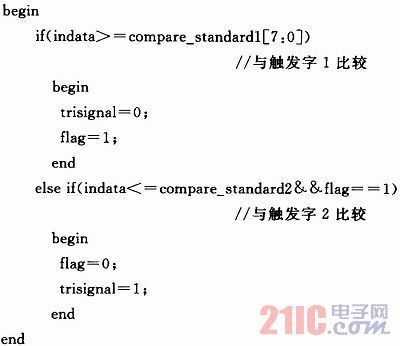

compare_standardl,、compare_standard2分別是觸發(fā)字1和觸發(fā)字2。flag為標(biāo)志變量,,當(dāng)A/D數(shù)據(jù)大于觸發(fā)字1時(shí),,flag=1;當(dāng)A/D數(shù)據(jù)小于觸發(fā)字2時(shí),,flag=0,。具體實(shí)現(xiàn)的代碼如下:

1.2 觸發(fā)模式的選擇

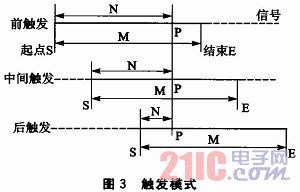

觸發(fā)模式分為前觸發(fā)、中間觸發(fā)和后觸發(fā),。觸發(fā)模式的選擇決定了觸發(fā)的預(yù)觸發(fā)深度N的不同,。在一定的存儲(chǔ)深度M下,捕捉的波形在觸發(fā)點(diǎn)P附近被最大化地存儲(chǔ)和顯示,。觸發(fā)點(diǎn)前端波形的觀察選擇前觸發(fā)模式,,即預(yù)觸發(fā)深度占存儲(chǔ)深度的比例要大。觸發(fā)模式如圖3所示,。S代表起點(diǎn),E代表結(jié)束點(diǎn),。觸發(fā)點(diǎn)前后波形的觀察選擇中間觸發(fā)模式,,觸發(fā)點(diǎn)后端波形的觀察選擇后觸發(fā)模式。

1.3 FIFO讀寫數(shù)據(jù)控制

FIFO存儲(chǔ)器的讀寫是用狀態(tài)機(jī)來實(shí)現(xiàn)的,。5個(gè)狀態(tài)分別為wait,、wr_trigger、wr_read、wr_full,、read,。FIFO控制器流程如圖4所示。模塊開始進(jìn)入wait狀態(tài)等待啟動(dòng)信號(hào)start上升沿,,如果start上升沿到來模塊轉(zhuǎn)到wr_trigger狀態(tài),,否則將在wait狀態(tài)一直等待;當(dāng)模塊進(jìn)入wr_trigger狀態(tài)時(shí),,F(xiàn)IFO開始寫數(shù)據(jù)直到滿足觸發(fā)模式的預(yù)觸發(fā)深度,,此時(shí)的寫時(shí)鐘等于采樣時(shí)鐘;此后模塊進(jìn)入wr_read狀態(tài),,F(xiàn)IFO開始一邊讀數(shù)據(jù)一邊寫數(shù)據(jù),,即一直保持FIFO中存儲(chǔ)的數(shù)據(jù)是最新A/D轉(zhuǎn)換數(shù)據(jù),此時(shí)的讀寫時(shí)鐘與采樣時(shí)鐘是同頻的,。直到觸發(fā)信號(hào)上升沿的到來,,否則FIFO存儲(chǔ)器將一直讀數(shù)據(jù)和寫數(shù)據(jù);當(dāng)觸發(fā)信號(hào)上升沿有效時(shí),,模塊進(jìn)入wr_full狀態(tài),,F(xiàn)IFO存儲(chǔ)器停止讀數(shù)據(jù),開始寫數(shù)據(jù),,直到FIFO寫滿數(shù)據(jù),;當(dāng)FIFO寫滿數(shù)據(jù)(full=1)以后,模塊轉(zhuǎn)到read狀態(tài),,F(xiàn)IFO開始讀數(shù)據(jù)并通過通信接口發(fā)送到顯示控制界面進(jìn)行直觀的顯示,,直到FIFO為空empty=1,此時(shí)讀時(shí)鐘為顯示時(shí)鐘,;FIFO讀數(shù)據(jù)操作完畢,,模塊將一直停留在wait狀態(tài)等待下一次采集啟動(dòng)信號(hào)的到來,如此反復(fù)執(zhí)行,。

1.4 高速數(shù)據(jù)采集模塊電路設(shè)計(jì)

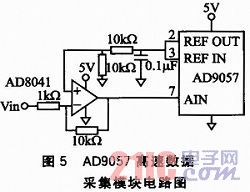

AD9057是8位的模數(shù)轉(zhuǎn)換器,,可以達(dá)到60 MHz的最大采樣頻率。設(shè)計(jì)中,,模塊采用50 MHz的采樣頻率,,AD9057帶有2.5V的基準(zhǔn)電壓,可以對(duì)1 V峰峰值輸入模擬信號(hào)進(jìn)行A/D轉(zhuǎn)換,。通常采用高頻,、寬帶運(yùn)放對(duì)模擬信號(hào)進(jìn)行緩沖,本設(shè)計(jì)中采用AD8041作為放大器,,AD9057高速數(shù)據(jù)采集模塊電路圖電路圖如圖5所示,。

2 結(jié)論

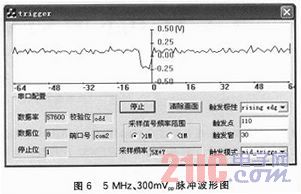

模塊可以工作在50 MHz的采樣頻率下,,并且在模擬信號(hào)幅度偏小和有一定干擾的情況下也可以正常地工作。本次設(shè)計(jì)中采用了VC++6.0編寫的顯示控制界面進(jìn)行模塊驗(yàn)證,。圖6是數(shù)據(jù)采集模塊捕捉的頻率為5 MHz,、300mVpp交替出現(xiàn)間隔為1 ms的一個(gè)脈沖波形圖。

其中,,觸發(fā)模式選用中間觸發(fā),,觸發(fā)極性為上升沿,采樣頻率為50 MHz,。由此可見,,本模塊的技術(shù)方案可行,具有靈活簡(jiǎn)潔的特點(diǎn),,可以應(yīng)用在程控儀器和自適應(yīng)信號(hào)采集與處理系統(tǒng)中,。