DSP的供電電路設(shè)計(jì)是DSP應(yīng)用系統(tǒng)設(shè)計(jì)的一個(gè)重要組成部分。TIDSP家族(C6000和C54xx)要求有獨(dú)立的內(nèi)核電源和I/O電源,如TMS320VC5402,它的內(nèi)核電壓是1.8V,I/O電壓是3.3V。由于DSP一般在系統(tǒng)中要承擔(dān)大量的實(shí)時(shí)數(shù)據(jù)計(jì)算,在其CPU內(nèi)部,頻繁的部件開關(guān)轉(zhuǎn)換會(huì)使系統(tǒng)功耗大大增加。所以降低為DSP內(nèi)部CPU供電的核心電壓無疑是降低系統(tǒng)功耗的最有效的辦法之一。

雖然TI的DSP不要求內(nèi)核電源和I/O電源之間有特殊的上電順序,但是假如有一個(gè)電源低于正常的工作電壓,設(shè)計(jì)時(shí)就要確保沒有任何一個(gè)電源在這個(gè)時(shí)間段處于上電狀態(tài),如果違反此規(guī)則,將嚴(yán)重影響器件的長(zhǎng)期可靠性。另外,從系統(tǒng)級(jí)考慮,總線競(jìng)爭(zhēng)就要求按順序上電。這種情況下,內(nèi)核電源的上電就應(yīng)當(dāng)同步或提前于I/O控制器。

講究供電次序的原因在于:如果只有CPU內(nèi)核獲得供電,周邊I/O沒有供電,對(duì)芯片是不會(huì)產(chǎn)生任何損害的,只是沒有輸入/輸出能力而已;如果反過來,周邊I/O得到供電而CPU內(nèi)核沒有加電,那么芯片緩沖/驅(qū)動(dòng)部分的三極管將處于一個(gè)未知狀態(tài)下工作,這是非常危險(xiǎn)的。在有一定安全措施保障的前提下,允許兩個(gè)電源同時(shí)加電,兩個(gè)電源都必須在25ms內(nèi)達(dá)到規(guī)定電平的95%。

1 輸入電壓等于3.3V的情況

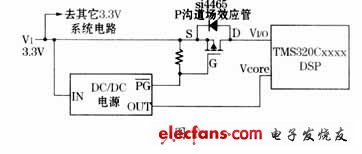

1.1 使用場(chǎng)效應(yīng)管和有PG引腳的直流電壓轉(zhuǎn)換器

這種方案是所有方案中最簡(jiǎn)單的一種。它用一個(gè)P溝道的場(chǎng)效應(yīng)管作為電源分配開關(guān)。這種方法要求直流電壓轉(zhuǎn)換器具有PG(Power Good)引腳。在核電壓輸出未到達(dá)額定值之前,PG引腳一直輸出為高。當(dāng)核電壓輸出達(dá)到額定值后,PG引腳變低,驅(qū)動(dòng)場(chǎng)效應(yīng)管打開,把外部3.3V電壓加到DSP的I/O上。所以,這種方法可以保持正確的上電順序。

斷電時(shí)的情況則比較復(fù)雜,有很多因素將會(huì)影響斷電的順序,如負(fù)載電流的驅(qū)動(dòng)能力、電容的大小等。不過一種可能的順序是:在去除了外部3.3V的電壓后,直流電壓轉(zhuǎn)換器的輸出電壓降低,同時(shí)PG引腳變高,關(guān)閉了場(chǎng)效應(yīng)管,去除了DSP的I/O電壓。

需要說明的一點(diǎn)是:因?yàn)镻G引腳是漏極開路輸出,所以要在源極與柵極之間加一個(gè)電阻,以確保當(dāng)PG引腳變成高阻時(shí),場(chǎng)效應(yīng)管能夠關(guān)閉。

1.2 使用場(chǎng)效應(yīng)管和電源監(jiān)測(cè)芯片

如果直流電源轉(zhuǎn)換器沒有PG管腳,則可以使用電源監(jiān)測(cè)芯片(Supply Voltage Supervisor,SVS)來完成這個(gè)功能。這樣不僅可以很好地保證上電和斷電的順序,還可以實(shí)現(xiàn)對(duì)DSP的復(fù)位。

在這個(gè)電路里,SVS負(fù)責(zé)監(jiān)測(cè)外部輸入電壓。上電時(shí),當(dāng)3.3V電壓超過SVS的門限電壓200ms后,RESET引腳輸出為低,驅(qū)動(dòng)場(chǎng)效應(yīng)管工作,把外部的3.3V電壓加到DSP的I/O上。這里假設(shè)直流電源轉(zhuǎn)換器的響應(yīng)時(shí)間小于200ms。

在斷電時(shí),當(dāng)去除3.3V的外部電壓后,SVS檢測(cè)到并馬上輸出一個(gè)RESET高,關(guān)閉場(chǎng)效應(yīng)管,這樣就可以保證在去除核電壓前去除I/O電壓。同樣,這里也有一個(gè)假設(shè),那就是在3.3V的電壓衰減后,直流電壓變換器還能持續(xù)輸出很短時(shí)間的電壓。當(dāng)然,這也是一個(gè)合理的假設(shè)。

在這個(gè)電路里,TPS3824-33專門用來監(jiān)測(cè)3.3V電壓。這一系列的芯片可以監(jiān)測(cè)1.1V到6V的電壓,同時(shí),SVS還有看門狗引腳WDI供設(shè)計(jì)者使用。SVS內(nèi)部集成了一個(gè)帶電復(fù)位生成器,只要其自身的供電電壓在1V以上,就可以保證輸出有效的RESET信號(hào)。一旦監(jiān)測(cè)電壓低于閾值電壓時(shí),復(fù)位邏輯輸出被激活并使處理器復(fù)位。

如果直流電壓轉(zhuǎn)換器有PG引腳,則可以如圖2所示:把PG引腳和RESET引腳用一個(gè)與門相連,輸出到DSP的RESET引腳。當(dāng)SVS的RESET引腳輸出為低,或者DC/DC的PG引腳輸出為低(表示現(xiàn)在電源輸出未達(dá)到正常),都將實(shí)現(xiàn)對(duì)DSP的復(fù)位操作。2 輸入電壓高于3.3V的情況

由于輸入電壓高于3.3V,所以在電路中還必須使用電壓調(diào)節(jié)器。這里選用的是TI的低壓差電壓調(diào)節(jié)器(LDO),在實(shí)際設(shè)計(jì)中選用具體的LDO時(shí),還要考慮輸出電流的驅(qū)動(dòng)能力等因素。在TI的網(wǎng)站上有為C5000和C6000系列推薦的電源系列。

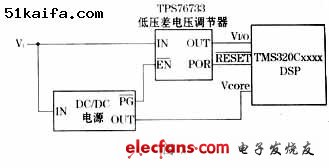

2.1 帶有PG引腳的低壓差電壓調(diào)節(jié)器

這種方案要求低壓差電壓調(diào)節(jié)器具有ENABLE引腳,直流電壓轉(zhuǎn)換器具有PG引腳。在上電時(shí),當(dāng)直流電壓轉(zhuǎn)換器輸出正常電壓后,PG引腳變低,使能LDO的ENABLE引腳,LDO工作,輸出DSP的I/O電壓,這樣就可以讓I/O電壓的上電電壓滯后于核電壓的上電。這里的直流電壓轉(zhuǎn)換器可以是LDO也可以是開關(guān)電源,這取決于輸出電流的要求。

同樣,在斷電時(shí)由于有很多不確定的因素,將無法保證準(zhǔn)確的斷電順序。一種可能的順序是:當(dāng)去除外部3.3V電壓后,直流電壓轉(zhuǎn)換器輸出衰減,同時(shí)PG 引腳輸出為高,關(guān)閉LDO,去除DSP的I/O電壓。對(duì)于特定的某一系統(tǒng),需要通過試驗(yàn)來確定準(zhǔn)確的斷電順序。TPS76733有一個(gè)加電啟動(dòng)的POR (Power-on-Reset)引腳,它與DSP的RESET引腳直接相連。

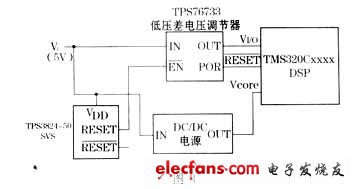

2.2 低壓差電壓調(diào)節(jié)器和SVS

如果對(duì)核電壓供電的直流電壓轉(zhuǎn)換器沒有PG引腳,則需要使用SVS來實(shí)現(xiàn)對(duì)I/O電壓的延遲。這種方案與1.2小節(jié)介紹的方案很類似。在上電時(shí),當(dāng)輸入電壓超過閾值電壓200ms后,RESET輸出高,使能LDO輸出I/O電壓。在斷電時(shí),當(dāng)外部電壓衰減后,SVS的RESET輸出高,關(guān)閉 LDO從而關(guān)閉I/O電壓,而直流電壓轉(zhuǎn)換器仍然可以持續(xù)供電很短的時(shí)間,這樣就保證了斷電的正確時(shí)序。在這里,SVS選用的是TPS3824-50,專門用來監(jiān)測(cè)5V的輸入電壓。

如果對(duì)核電壓供電的直流電壓轉(zhuǎn)換器有PG引腳,則若成本允許,也可以使用這種方法,同時(shí)還可以實(shí)現(xiàn)對(duì)DSP的復(fù)位。把SVS的RESET引腳和DC/DC的PG引腳通過一個(gè)與門相連,輸出到DSP的RESET引腳,具體電路可以參考圖2。

3 結(jié)束語

本文從總體上介紹了DSP的雙電源解決方案,但是針對(duì)具體的電源要求,如最大輸出電流、輸出紋波電壓、電源效率、輸出電壓容差等,都必須在電路設(shè)計(jì)和電源芯片的選擇上加以考慮。值得注意的是文中沒有包括必須的退耦電容。