中心議題:

解決方案:

- 20 - H規(guī)則及3 -W 法則

- 地線的布置

- 電源線的布置

隨著現(xiàn)代電子技術(shù)的發(fā)展以及芯片的高速化和集成化,各種電子設(shè)備系統(tǒng)內(nèi)外的電磁環(huán)境更加復(fù)雜,因此在印制電路板的電路設(shè)計(jì)階段考慮電磁兼容性( EMC) 設(shè)計(jì)是非常重要的。以12層板為例討論了多層PCB分層方法、布線的規(guī)則、地線和電源線布置以及電磁兼容性。

0 引言

電磁兼容(Electro - Magnetic Compatibility,簡稱EMC)是一門新興綜合性學(xué)科,它主要研究電磁干擾和抗干擾問題。電磁兼容性是指電子設(shè)備或系統(tǒng)在規(guī)定的電磁環(huán)境電平下,不因電磁干擾而降低性能指標(biāo),同時(shí)它們本身產(chǎn)生的電磁輻射不大于限定的極限電平,不影響其它系統(tǒng)的正常運(yùn)行,并達(dá)到設(shè)備與設(shè)備、系統(tǒng)與系統(tǒng)之間互不干擾、共同可靠工作的目的。電磁干擾( EM I)產(chǎn)生是由于電磁干擾源通過耦合路徑將能量傳遞給敏感系統(tǒng)造成的,它包括由導(dǎo)線和公共地線的傳導(dǎo)、通過空間輻射或近場耦合3種基本形式。實(shí)踐證明,即使電路原理圖設(shè)計(jì)正確,印制電路板設(shè)計(jì)不當(dāng),也會(huì)對(duì)電子設(shè)備的可靠性產(chǎn)生不利影響,所以保證印制電路板電磁兼容性是整個(gè)系統(tǒng)設(shè)計(jì)的關(guān)鍵,本文主要討論電磁兼容技術(shù)及其在多層印制線路板( Printed Circuit Board,簡稱PCB)設(shè)計(jì)中的應(yīng)用。

PCB是電子產(chǎn)品中電路元件和器件的支撐件,它提供電路元件和器件之間的電氣連接,是各種電子設(shè)備最基本的組成部分。如今,大規(guī)模和超大規(guī)模集成電路已在電子設(shè)備中得到廣泛應(yīng)用,而且元器件在印刷電路板上的安裝密度越來越高,信號(hào)的傳輸速度更是越來越快, 由此而引發(fā)的EMC問題也變得越來越突出。PCB 有單面板(單層板) 、雙面板(雙層板)和多層板之分。單面板和雙面板一般用于低、中密度布線的電路和集成度較低的電路, 多層板使用高密度布線和集成度高的電路。從電磁兼容的角度看單面板和雙面板不適宜高速電路,單面、雙面布線已滿足不了高性能電路的要求,而多層布線電路的發(fā)展為解決以上問題提供了一種可能,并且其應(yīng)用變得越來越廣泛。

1 多層布線的特點(diǎn)

PCB是由具有多層結(jié)構(gòu)的有機(jī)和無機(jī)介質(zhì)材料組成,層之間的連接通過過孔來實(shí)現(xiàn),過孔鍍上或填充金屬材料就可以實(shí)現(xiàn)層之間的電信號(hào)導(dǎo)通。多層布線之所以得到廣泛的應(yīng)用,究其原因,有以下特點(diǎn):

(1)多層板內(nèi)部設(shè)有專用電源層、地線層。電源層可以作為噪聲回路,降低干擾;同時(shí)電源層還為系統(tǒng)所有信號(hào)提供回路,消除公共阻抗耦合干擾。減小了供電線路的阻抗,從而減小了公共阻抗干擾。

(2)多層板采用了專門地線層,對(duì)所有信號(hào)線而言都有專門接地線。信號(hào)線的特性:阻抗穩(wěn)定、易匹配,減少了反射引起的波形畸變;同時(shí),采用專門的地線層加大了信號(hào)線和地線之間的分布電容,減小了串?dāng)_。

2 印制電路板的疊層設(shè)計(jì)

2.1 PCB的布線規(guī)則

多層電路板的電磁兼容分析可以基于克希霍夫定律和法拉第電磁感應(yīng)定律。根據(jù)克希霍夫定律, 任何時(shí)域信號(hào)由源到負(fù)載的傳輸都必須有一個(gè)最低阻抗的路徑。

具有多層的PCB常常用于高速、高性能的系統(tǒng),其中的多層用于直流(DC)電源或地參考平面。這些平面通常是沒有任何分割的實(shí)體平面,因?yàn)榫哂凶銐虻膶佑米麟娫椿虻貙樱虼藳]有必要將不同的DC電壓置于同一層上。該層將會(huì)用作與它們相鄰的傳輸線上信號(hào)的電流返回通路。構(gòu)造低阻抗的電流返回通路是這些平面層最重要的EMC目標(biāo)。

信號(hào)層分布在實(shí)體參考平面層之間,它們可以是對(duì)稱的帶狀線和非對(duì)稱的帶狀線。以一個(gè)12層板為例說明多層板的結(jié)構(gòu)和布局 。其分層結(jié)構(gòu)為T - P - S - P - S - P - S - P - S - S - P - B,“T”為頂層,“P”為參考平面層,“S”為信號(hào)層,“B”為底層。從頂層至底層依次為第1層、第2層、……、第12層。頂層和底層用作元件的焊盤,信號(hào)在頂層和底層不應(yīng)傳輸太長的距離,以便減少來自走線的直接輻射。不相容的信號(hào)線應(yīng)相互隔離,這樣做的目的是避免相互之間產(chǎn)生耦合干擾。高頻與低頻、大電流與小電流、數(shù)字與模擬信號(hào)線是不相容的, 元件布置中就應(yīng)該把不相容元件放在印制板上不同的位置, 在信號(hào)線的布置上仍要注意把它們隔離。設(shè)計(jì)時(shí)要注意以下3個(gè)問題:

- 全球PCB2011年增速7%

- 共模和差模信號(hào)及其噪音抑制

- 印刷線路板元件布局結(jié)構(gòu)設(shè)計(jì)

- 電子產(chǎn)品輕薄化 高階銅箔基板需求俏

- 數(shù)模混合電路的PCB設(shè)計(jì)

- PCB布線技巧

- 什么是EMC認(rèn)證

- EMC是什么意思?

- EMC是什么?

- 常規(guī)pcb生產(chǎn)工藝流程

(1)確定哪個(gè)參考平面層將包含用于不同的DC電壓的多個(gè)電源區(qū)。假設(shè)第11層有多個(gè)DC電壓,就意味著設(shè)計(jì)者必須將高速信號(hào)盡可能遠(yuǎn)離第10層和底層,因?yàn)榉祷仉娏鞑荒芰鬟^第10層以上的參考平面,并且需要使用縫合電容,第3、5、7和9層分別為高速信號(hào)的信號(hào)層。重要信號(hào)的走線盡可能以一個(gè)方向布局,以便優(yōu)化層上可能的走線通道數(shù)。分布在不同層上的信號(hào)走線應(yīng)互相垂直,這樣可以減少線間的電場和磁場的耦合干擾,第3和第7層可以設(shè)定為“東西”走線,而第5和第9層設(shè)置為“南北”走線。走線布在哪一層要根據(jù)其到達(dá)目的地的方向。

(2)高速信號(hào)走線時(shí)層的變化,及哪些不同的層用于一個(gè)獨(dú)立的走線,確保返回電流從一個(gè)參考平面流到需要的新參考平面。這樣是為了減小信號(hào)環(huán)路面積,減小環(huán)路的差模電流輻射和共模電流輻射。環(huán)路輻射與電流強(qiáng)度、環(huán)路面積成正比。實(shí)際上,最好的設(shè)計(jì)并不要求返回電流改變參考平面,而是簡單地從參考平面的一側(cè)改變到另一側(cè)。如信號(hào)層的組合可以用作信號(hào)層對(duì):第3層和第5層,第5層和第7層,第7層和第9層,這就允許一個(gè)東西方向和南北方向形成一個(gè)布線組合。但是第3層和第9層的組合就不應(yīng)使用,因?yàn)檫@要求返回電流從第4層流到第8層。盡管一個(gè)去耦電容可以放置在過孔附近,但在高頻時(shí)由于存在引線和過孔電感而使電容失去作用。并且這種走線會(huì)使信號(hào)環(huán)路面積增大,不利減小電流輻射。

(3)為參考平面層選定DC電壓。該例中,由于處理器內(nèi)部信號(hào)處理的高速性,致使在電源/地參考引腳上存在大量的噪聲。因此,在為處理器提供相同DC電壓上使用去耦電容器非常重要,并且盡可能有效地使用去耦電容器。降低這些元件電感的最好方法是連接走線盡可能短和寬,并且盡可能使過孔短和粗。

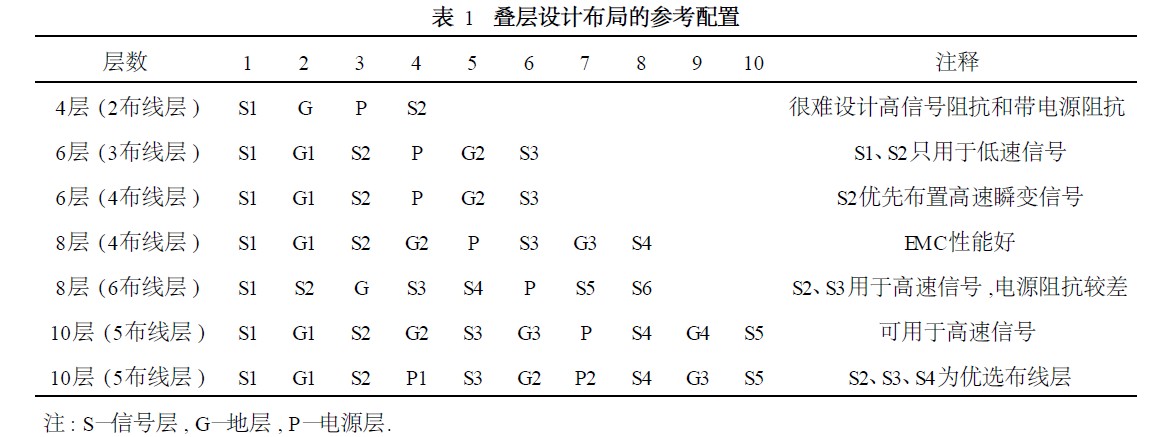

如果第2層分配為“地”,且第4層分配為處理器的電源,則過孔距離放置處理器和去耦電容器的頂層應(yīng)該盡可能短。延伸到板的底層的過空剩余部分不包含任何重要的電流,而且距離短不會(huì)具有天線作用。表1列出了疊層設(shè)計(jì)布局的參考配置。

2.2 20 - H規(guī)則及3 -W 法則

在多層PCB板電磁兼容性設(shè)計(jì)中,確定多層板電源層與邊沿的距離和解決印制條間的距離有兩個(gè)基本原則: 20 - H規(guī)則及3 - W法則。

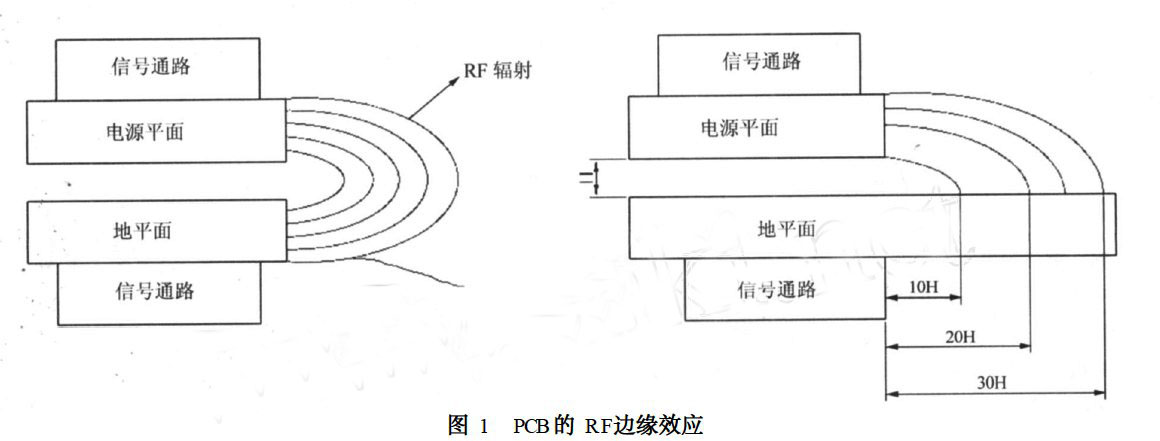

20 - H原則:由于磁通之間的連接, RF電流通常存在于電源平面的邊緣,這種層間的耦合稱為邊緣效應(yīng),當(dāng)使用高速的數(shù)字邏輯和時(shí)鐘信號(hào)時(shí),電源平面間會(huì)互相耦合RF電流,如圖1所示。為減小這種效應(yīng),電源平面的物理尺寸都應(yīng)該比最靠近地平面的物理尺寸至少小20H (H為電源平面和地平面之間的距離) ,電源的邊緣效應(yīng)通常發(fā)生在10H左右, 20H時(shí)約10%的磁通被阻斷,如果想達(dá)到98%磁通被阻斷的話,則需要100%的邊界值,如圖1所示。20 - H規(guī)則決定了電源平面和最近的接地平面間的物理距離,這個(gè)距離包括敷銅厚度、預(yù)填充和絕緣分離層。使用20 - H可以提高PCB自身的諧振頻率。

3 - W法則:當(dāng)兩條印制線間距較小時(shí),兩條線之間會(huì)發(fā)生電磁串?dāng)_,這會(huì)使有關(guān)電路功能失常,為避免這種干擾,應(yīng)保持任何線條間距不小于3倍印制線條寬度,即不小于3W (W為印制線條寬度)。印制線條寬度取決于線條阻抗的要求,太寬會(huì)影響布線密度,太窄會(huì)影響傳輸?shù)浇K端的信號(hào)完整性和強(qiáng)度。時(shí)鐘電路、差分對(duì)、I/O端口的布線都是3 - W原則的基本應(yīng)用對(duì)象。3 - W原則只是表示了串?dāng)_能量衰減70%的電磁通量線邊界,若要求更高,如保證串?dāng)_能量衰減98%的電磁通量邊界線就必須采用10W間隔。

2.3 地線的布置

首先,要建立分布參數(shù)的概念,高于一定頻率時(shí), 任何金屬導(dǎo)線都要看成是由電阻、電感構(gòu)成的器件 。所以接地引線具有一定阻抗并且構(gòu)成電氣回路,不管是單點(diǎn)接地還是多點(diǎn)接地, 都必須構(gòu)成低阻抗回路進(jìn)入真正的地或機(jī)架。25mm 長的典型印制線大約會(huì)表現(xiàn)15~ 20nH電感,加上分布電容的存在,就會(huì)在接地板和設(shè)備機(jī)架之間構(gòu)成諧振電路。其次, 接地電流流經(jīng)接地線時(shí),會(huì)產(chǎn)生傳輸線效應(yīng)和天線效應(yīng)。當(dāng)線條長度為1 /4波長時(shí),表現(xiàn)出很高的阻抗,接地線實(shí)際上是開路的, 接地線反而成為向外輻射的天線。最后,接地板上充滿高頻電流和騷擾形成的渦流,因此,在接地點(diǎn)之間構(gòu)成許多回路,這些回路的直徑(或接地點(diǎn)間距) 應(yīng)小于最高頻率波長的1 /20。選擇恰當(dāng)?shù)钠骷窃O(shè)計(jì)成功的重要因素,特別是在選擇邏輯器件時(shí),盡量選擇上升時(shí)間比5ns長的, 決不要選比電路要求時(shí)序快的邏輯器件。

2.4 電源線的布置

對(duì)于多層板, 采用電源層- 地層結(jié)構(gòu)供電,這種結(jié)構(gòu)的特性阻抗比軌線對(duì)小得多,可以做到小于1Ω。這種結(jié)構(gòu)具有一定的電容,不必在每個(gè)集成芯片旁加高頻去耦電容。即使層電容容量不夠,需要外加去耦電容時(shí),也不要加在集成芯片旁邊,可加在印制板的任何地方。集成芯片的電源腳和地腳可以通過金屬化通孔直接與電源層和地層連接, 所以供電環(huán)路總是最小的。由于“電流總是走阻抗最小途徑”原則, 地層上的高頻回流總是緊貼在軌線下面走, 除非有地層隔縫阻擋, 因此信號(hào)環(huán)路也總是最小的。可見電源層- 地層結(jié)構(gòu)與軌線對(duì)供電相比較, 具有布置簡單靈活、電磁兼容性好等優(yōu)點(diǎn)。

3 結(jié)束語

總之,在多層PCB設(shè)計(jì)中,元器件要分組放置, 以防止產(chǎn)生組間干擾; 高速電路位置要安排恰當(dāng), 以免通過電場耦合或磁場耦合干擾其他電路; 根據(jù)情況分別設(shè)置地線, 以防止共地線阻抗耦合干擾; 供電環(huán)路面積應(yīng)該減小到最低程度, 且不同電源的供電環(huán)路不要重疊, 以避免產(chǎn)生磁場耦合;不相容的信號(hào)線要相互隔離, 以免產(chǎn)生耦合干擾; 還應(yīng)減小信號(hào)環(huán)路面積, 以降低環(huán)路輻射和共模輻射。