本文給出了采用這些技術(shù)的高速環(huán)境狀態(tài)機(jī)設(shè)計(jì)的規(guī)范及分析方法和優(yōu)化方法,并給出了相應(yīng)的示例。

為了使FPGA或CPLD中的狀態(tài)機(jī)設(shè)計(jì)滿足高速環(huán)境要求,設(shè)計(jì)工程師需要認(rèn)識(shí)到以下幾點(diǎn):寄存器資源和邏輯資源已經(jīng)不是問題的所在,狀態(tài)機(jī)本身所占用的FPGA或CPLD邏輯資源或寄存器資源非常小;狀態(tài)機(jī)對整體數(shù)據(jù)流的是串行操作,如果希望數(shù)據(jù)處理的延時(shí)非常小,就必須提高操作的并行程度,壓縮狀態(tài)機(jī)中狀態(tài)轉(zhuǎn)移的路徑長度;高速環(huán)境下應(yīng)合理分配狀態(tài)機(jī)的狀態(tài)及轉(zhuǎn)移條件。本文將結(jié)合實(shí)際應(yīng)用案例來說明。

狀態(tài)機(jī)設(shè)計(jì)規(guī)范

1. 使用一位有效的方式進(jìn)行狀態(tài)編碼

狀態(tài)機(jī)中狀態(tài)編碼主要有三種:連續(xù)編碼(sequential encoding)、一位有效(one-hot encoding)方式編碼以及不屬于這兩種的編碼。例如,對于一個(gè)5個(gè)狀態(tài)(State0~State4)的狀態(tài)機(jī),連續(xù)編碼方式狀態(tài)編碼為:State0-000、State1-001、State2-010、State3-011、State4-100。一位有效方式為下為:State0-00001、State1-00010、State2-00100、State3-01000、State4-10000。對于自行定義的編碼則差別很大,例如試圖將狀態(tài)機(jī)的狀態(tài)位直接作為輸出所需信號(hào),這可能會(huì)增加設(shè)計(jì)難度。

使用一位有效編碼方式使邏輯實(shí)現(xiàn)更簡潔,因?yàn)橐粋€(gè)狀態(tài)只需要用一位來指示,而為此增加的狀態(tài)寄存器數(shù)目相對于整個(gè)設(shè)計(jì)來說可以忽略。一位有效至少有兩個(gè)含義:對每個(gè)狀態(tài)位,該位為1對應(yīng)唯一的狀態(tài),判斷當(dāng)前狀態(tài)是否為該狀態(tài),只需判斷該狀態(tài)位是否為1;如果狀態(tài)寄存器輸入端該位為1,則下一狀態(tài)將轉(zhuǎn)移為該狀態(tài),判斷下一狀態(tài)是否為該狀態(tài),只需判斷表示下一狀態(tài)的信號(hào)中該位是否為1。

2. 合理分配狀態(tài)轉(zhuǎn)移條件

在狀態(tài)轉(zhuǎn)移圖中,每個(gè)狀態(tài)都有對應(yīng)的出線和入線,從不同狀態(tài)經(jīng)不同的轉(zhuǎn)移條件到該狀態(tài)的入線數(shù)目不能太多。以采用與或邏輯的CPLD設(shè)計(jì)來分析,如果這樣的入線太多則將會(huì)需要較多的乘積項(xiàng)及或邏輯,這就需要更多級(jí)的邏輯級(jí)聯(lián)來完成,從而增加了寄存器間的延遲;對于FPGA則需要多級(jí)查找表來實(shí)現(xiàn)相應(yīng)的邏輯,同樣會(huì)增加延遲。狀態(tài)機(jī)的應(yīng)用模型如圖1所示。

狀態(tài)機(jī)設(shè)計(jì)的分析方法

狀態(tài)機(jī)設(shè)計(jì)的分析方法可以分為兩種:一種是流程處理分析,即分析數(shù)據(jù)如何分步處理,將相應(yīng)處理的步驟依次定為不同狀態(tài),該方法能夠分析非常復(fù)雜的狀態(tài)機(jī),類似于編寫一個(gè)軟件程序的分析,典型設(shè)計(jì)如讀寫操作和數(shù)據(jù)包字節(jié)分析;另一種方法是關(guān)鍵條件分析,即根據(jù)參考信號(hào)的邏輯條件來確定相應(yīng)的狀態(tài),這樣的參考信號(hào)如空或滿指示、起始或結(jié)束、握手應(yīng)答信號(hào)等。這兩種分析方法并沒有嚴(yán)格的界限,在實(shí)際的狀態(tài)機(jī)設(shè)計(jì)分析時(shí)往往是這兩種方法結(jié)合使用。下面分別說明這兩種分析方法。

1. 流程處理分析

例如,在一個(gè)讀取ZBT SRAM中數(shù)據(jù)包的設(shè)計(jì)中,要根據(jù)讀出的數(shù)據(jù)中EOP(End of Packet)信號(hào)是否為1來決定一個(gè)包的讀操作是否結(jié)束,由于讀取數(shù)據(jù)的延后,這樣就會(huì)從ZBT SRAM中多讀取數(shù)據(jù),為此可以設(shè)計(jì)一個(gè)信號(hào)VAL_out來過濾掉多讀的數(shù)據(jù)。

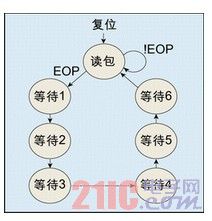

根據(jù)數(shù)據(jù)到達(dá)的先后及占用的時(shí)鐘周期數(shù),可以設(shè)計(jì)如圖2所示的狀態(tài)機(jī)(本文設(shè)定:文字說明及插圖中當(dāng)前狀態(tài)表示為s_State[n:0],為狀態(tài)寄存器的輸出;下一狀態(tài)next_State[n:0],為狀態(tài)寄存器的輸入;信號(hào)之間的邏輯關(guān)系采用Verilog語言(或C語言)中的符號(hào)表示;#R表示需要經(jīng)過一級(jí)寄存器,輸出信號(hào)對應(yīng)寄存器的輸出端)。該狀態(tài)機(jī)首先判斷是否已經(jīng)到達(dá)包尾,如果是,則依次進(jìn)入6個(gè)等待狀態(tài),等待狀態(tài)下的數(shù)據(jù)無效,6個(gè)等待狀態(tài)結(jié)束后將正常處理數(shù)據(jù)。

2. 關(guān)鍵條件分析

圖3為一個(gè)路由器線卡高速數(shù)據(jù)包分發(fā)處理的框圖,較高速率的數(shù)據(jù)包經(jīng)過分發(fā)模塊以包為單位送往兩個(gè)較低速率數(shù)據(jù)通路(即寫入FIFO1或FIFO2)。

對于分發(fā)模塊設(shè)計(jì),關(guān)鍵參考信號(hào)是EOP及快滿信號(hào)AF1、AF2,參考EOP可以實(shí)現(xiàn)每次處理一個(gè)包,參考AF1、AF2信號(hào)可以決定相應(yīng)的包該往哪個(gè)FIFO中寫入。分發(fā)算法為:FIFO1未滿(AF1=0),數(shù)據(jù)包將寫入FIFO1;如果FIFO1將滿且FIFO2未滿(AF1=1,且AF2=0),則下一數(shù)據(jù)包將寫入FIFO2;如果FIFO1、FIFO2都將滿(AF1=1且AF2=1),則進(jìn)入丟包狀態(tài)。狀態(tài)機(jī)描述如圖4所示:UseFifo1狀態(tài)下數(shù)據(jù)包將寫入FIFO1,UseFifo2狀態(tài)下數(shù)據(jù)包將寫入FIFO2,丟包狀態(tài)下數(shù)據(jù)包被丟棄,提供丟包計(jì)數(shù)使能DropCountEnable。

狀態(tài)機(jī)的進(jìn)一步優(yōu)化

1. 利用一位有效編碼方式

如前所述,狀態(tài)機(jī)的工作頻率跟狀態(tài)機(jī)中各個(gè)狀態(tài)對應(yīng)的不同轉(zhuǎn)移條件的入線數(shù)目有關(guān)。如果到一個(gè)狀態(tài)的轉(zhuǎn)移條件相同但入線數(shù)非常多,其邏輯實(shí)現(xiàn)很可能并不復(fù)雜。在一位有效編碼方式下,對于某個(gè)狀態(tài),如果其他所有狀態(tài)經(jīng)相同的轉(zhuǎn)移條件到該狀態(tài),那么其邏輯實(shí)現(xiàn)可以很好地化簡。

例4:一位有效編碼方式下狀態(tài)位s_State[n:0]中,

s_State[1] | s_State[2] | ... | s_State[n]=1與 s_State[0]=1等價(jià),那么

next_State[0]=(s_State[0]&S) | (s_State[1]&T) | (s_State[2]&T) | ... | (s_State[n]) 可以化簡為:

next_State[0]=(s_State[0]&S) | ((~s_State[0])&T),右端輸入信號(hào)數(shù)目大大減少。

2. 利用寄存器的使能信號(hào)

多數(shù)FPGA或CPLD寄存器提供使能端,如果所有的狀態(tài)機(jī)轉(zhuǎn)移必須至少滿足某個(gè)條件,那么這個(gè)條件可以通過使能信號(hào)連接實(shí)現(xiàn),從而可以降低寄存器輸入端的邏輯復(fù)雜度。如上例中不同狀態(tài)間轉(zhuǎn)移必須以EOP為1作為前提,因而可以將該信號(hào)作為使能信號(hào)來設(shè)計(jì)。

3. 結(jié)合所選FPGA或CPLD內(nèi)部邏輯單元結(jié)構(gòu)編寫代碼

以Xilinx FPGA為例,一個(gè)單元內(nèi)2個(gè)4輸入查找表及相關(guān)配置邏輯可以實(shí)現(xiàn)5個(gè)信號(hào)輸入的最復(fù)雜的邏輯,或8~9個(gè)信號(hào)的簡單邏輯(例如全與或者全或),延時(shí)為一級(jí)查找表及配置邏輯延時(shí);如果將相鄰單元的4個(gè)4輸入查找表輸出連接到一個(gè)4輸入查找表,那么可以實(shí)現(xiàn)最復(fù)雜的6輸入邏輯,此時(shí)需要兩級(jí)查找表延時(shí)及相關(guān)配置邏輯延時(shí)。更復(fù)雜的邏輯需要更多的級(jí)連來實(shí)現(xiàn)。針對高速狀態(tài)機(jī)的情況,可以盡量將狀態(tài)寄存器輸入端的邏輯來源控制在7個(gè)信號(hào)以內(nèi),從而自主控制查找表的級(jí)連級(jí)數(shù),提高設(shè)計(jì)的工作頻率。

4. 通過修改狀態(tài)機(jī)

如果一個(gè)狀態(tài)機(jī)達(dá)不到工作頻率要求,則必須根據(jù)延時(shí)最大路徑修改設(shè)計(jì),通常的辦法有:改變狀態(tài)設(shè)置,添加新狀態(tài)或刪除某些狀態(tài),簡化轉(zhuǎn)移條件及單個(gè)狀態(tài)連接的轉(zhuǎn)移數(shù)目;修改轉(zhuǎn)移條件設(shè)置,包括改變轉(zhuǎn)移條件的組合,以及將復(fù)雜的邏輯改為分級(jí)經(jīng)寄存器輸出由寄存器信號(hào)再形成的邏輯,后者將會(huì)改變信號(hào)時(shí)序,因而可能需要改變狀態(tài)設(shè)置。

5. 使用并行邏輯

很多情況下要參考的關(guān)鍵信號(hào)可能非常多,如果參考這些關(guān)鍵信號(hào)直接設(shè)計(jì)狀態(tài)機(jī)所得到的結(jié)果可能很復(fù)雜,個(gè)別狀態(tài)的出線或入線將會(huì)非常多,因而將降低工作頻率。可以考慮通過設(shè)計(jì)并行邏輯來提供狀態(tài)機(jī)的關(guān)鍵信號(hào)以及所需的中間結(jié)果,狀態(tài)機(jī)負(fù)責(zé)維護(hù)并行邏輯以及產(chǎn)生數(shù)據(jù)處理的流程。并行邏輯應(yīng)分級(jí)設(shè)計(jì),級(jí)間為寄存器,從而減少寄存器到寄存器的延時(shí)。

一個(gè)使用并行邏輯的狀態(tài)機(jī),該設(shè)計(jì)用于使用單一數(shù)據(jù)總線將FIFO1~4中的數(shù)據(jù)發(fā)送到4個(gè)數(shù)據(jù)通路上去,該設(shè)計(jì)中并行邏輯產(chǎn)生每次操作時(shí)的通路及FIFO選擇結(jié)果,狀態(tài)機(jī)負(fù)責(zé)控制每次操作的流程:在“Idle”狀態(tài)下,如果FIFO1~4中有數(shù)據(jù)包供讀取,則進(jìn)入“Schedule”狀態(tài);獲得調(diào)度結(jié)果后“Schedule”經(jīng)過一個(gè)“Wait”狀態(tài),然后進(jìn)入“ReadData”狀態(tài)讀取數(shù)據(jù),同時(shí)開始計(jì)數(shù),計(jì)數(shù)到達(dá)所指定數(shù)值或者讀到數(shù)據(jù)包尾時(shí)進(jìn)入空閑狀態(tài)“Idle”,依次循環(huán)下去。

流水線設(shè)計(jì)

流水線(Pipelining)設(shè)計(jì)是將一個(gè)時(shí)鐘周期內(nèi)執(zhí)行的邏輯操作分成幾步較小的操作,并在較高速時(shí)鐘下完成。圖6a中邏輯被分為圖6b中三小部分,如果它的Tpd為T,則該電路最高時(shí)鐘頻率為1/T,而在圖6b中假設(shè)每部分的Tpd為T/3,則其時(shí)鐘頻率可提高到原來的3倍,因而單位時(shí)間內(nèi)的數(shù)據(jù)流量可以達(dá)到原來的三倍。代價(jià)是輸出信號(hào)相對于輸入滯后3個(gè)周期,時(shí)序有所改變(圖6b中輸出信號(hào)的總延時(shí)與圖6a中一樣,但數(shù)據(jù)吞吐量提高了),同時(shí)增加了寄存器資源,而FPGA具有豐富的寄存器資源。

本文所強(qiáng)調(diào)的通過減少寄存器間的邏輯延時(shí)來提高狀態(tài)機(jī)的工作頻率,與流水線設(shè)計(jì)的出發(fā)點(diǎn)一樣,不同的是流水線所強(qiáng)調(diào)的是數(shù)據(jù)處理時(shí)的數(shù)據(jù)通路優(yōu)化,而本文所強(qiáng)調(diào)的是狀態(tài)機(jī)中控制邏輯的優(yōu)化。