LED顯示屏的節(jié)能概念悄然掀起,成為它最為吸引消費(fèi)者眼球的亮點(diǎn),也是近年來(lái)火爆增長(zhǎng)的原因。當(dāng)然,經(jīng)過(guò)近幾年的瘋狂式增長(zhǎng),目前這個(gè)行業(yè)也陷入了一種僵局以重新洗牌的困局。在這一困境之中,必然有許多企業(yè)受此影響而元?dú)獯髠踔恋归]破產(chǎn),當(dāng)然也會(huì)有許多企業(yè)因此而走出陰霾,獲得更為長(zhǎng)遠(yuǎn)的發(fā)展。這是行業(yè)的發(fā)展規(guī)律,任何企業(yè)都逃脫不了這一劫難,如何在劫難中重生,是每個(gè)企業(yè)當(dāng)前比較關(guān)注的問(wèn)題。

在這個(gè)節(jié)能呼聲極高的時(shí)代,LED顯示屏的進(jìn)一步節(jié)能又無(wú)可厚非的成為了這個(gè)行業(yè)追逐的支撐點(diǎn)。很多企業(yè)在這一點(diǎn)上進(jìn)行各方面改良,在一定程度上有所改進(jìn),實(shí)現(xiàn)了節(jié)能的效果,但是要實(shí)現(xiàn)更大意義上的節(jié)能,還有很長(zhǎng)的路要走,這需要整個(gè)行業(yè)的共同努力。

最近市場(chǎng)上出現(xiàn)了為數(shù)不多的節(jié)能led顯示屏,通過(guò)對(duì)供電電源" title="電源">電源的改進(jìn)對(duì)于led顯示屏的節(jié)能效果起到重大的提升,吸引了不少消費(fèi)者的注意力,并給予了相當(dāng)高的期待,很多l(xiāng)ed顯示屏廠(chǎng)家躍躍欲試,準(zhǔn)備搶先引進(jìn)這一技術(shù),獲得發(fā)展先機(jī)。在目前的技術(shù)基礎(chǔ)上,節(jié)能led顯示屏的節(jié)能效果到底是如何實(shí)現(xiàn)的呢?

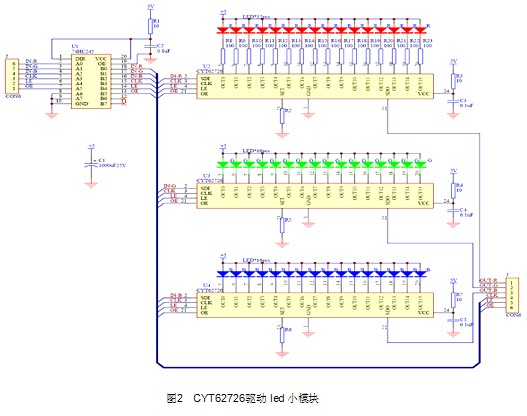

我們以一個(gè)led小模塊來(lái)分析其耗電狀況!如圖2,是一個(gè)以長(zhǎng)運(yùn)通光電推出的CYT62726為驅(qū)動(dòng)芯片的led小模塊,其供電電壓為5V,先不計(jì)算外圍器件的功耗,因?yàn)樗鼈冊(cè)谡麄€(gè)屏中所占的比重極小,那整個(gè)屏所耗的功率都在燈上,先計(jì)算燈點(diǎn)功率為Pled=n*Uvf*Iled(n為通道數(shù),Uvf為L(zhǎng)ED燈點(diǎn)的壓降,Iled為設(shè)定的電流值)CYT62726驅(qū)動(dòng)IC的管腳壓降一般為0.6V左右,紅綠藍(lán)燈點(diǎn)的壓降分別為1.8V,3.0V,3.0V如此那每個(gè)通道只需4V(3.0+0.6V)即可正常工作,保守一點(diǎn)可以設(shè)置成紅燈通道2.8V,藍(lán)綠通道3.8V而實(shí)際上我們的供電電壓都為5V,就相當(dāng)于增加了1V*Iled的功耗在IC內(nèi)部,所以如上可以設(shè)想只要將供電電源下降至紅2.8V,綠3.8V,藍(lán)3.8V,我們就可以省去那加在IC通道上的1V*Iled功耗,在其他器件不變的情況下便可實(shí)現(xiàn)led顯示屏節(jié)能至少15%以上,再加上本身對(duì)LED屏散熱要求的降低也能實(shí)現(xiàn)一定程度上的節(jié)能,這對(duì)于一個(gè)大屏來(lái)說(shuō)已經(jīng)是一個(gè)相當(dāng)大的數(shù)字了,相信客戶(hù)會(huì)樂(lè)于接受!

我們可以進(jìn)一步剖析其節(jié)能原理" title="節(jié)能原理">節(jié)能原理!

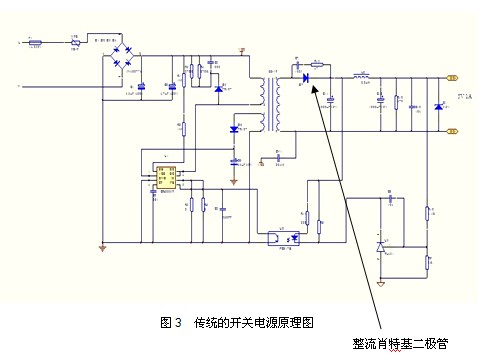

首先,從供電電源來(lái)看,如圖3是一個(gè)傳統(tǒng)的開(kāi)關(guān)電源原理圖,如果要將5V降為4V,整流肖特基正向壓降所占輸出電壓比重必然增加,開(kāi)關(guān)電源輸出電壓越低,因整流肖特基正向電壓比重越高(其比重X=V壓降/V輸出,輸出從5V降為4V,加入其壓降為0.5V,則其比重將從0.1上升為0.125,提高25%),電源輸出效率就越低,這對(duì)于LED屏幕整體節(jié)能效果并不明顯,所以采用這一電源設(shè)計(jì)原理顯然是是無(wú)法實(shí)現(xiàn)電源工作效率的提升。同時(shí),5V是標(biāo)稱(chēng)值電壓,在市場(chǎng)運(yùn)用上已經(jīng)相當(dāng)成熟,啟用新的開(kāi)關(guān)電源電源電壓,降低效率的同時(shí)只會(huì)增加成本,品質(zhì)也難保障,實(shí)現(xiàn)有困難。

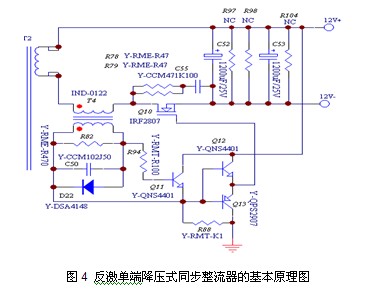

電源的設(shè)計(jì)是一個(gè)比較成熟的領(lǐng)域,可以采用另外一種設(shè)計(jì)思路實(shí)現(xiàn)度顯示屏的供電,例如同步整流技術(shù)。基本原理如圖4,Q10為功率MOSFET,在次級(jí)電壓的正半周,Q10導(dǎo)通,Q10起整流作用;在次級(jí)電壓的負(fù)半周,Q10關(guān)斷,同步整流電路的功率損耗主要包括Q10的導(dǎo)通損耗及柵極驅(qū)動(dòng)損耗。當(dāng)開(kāi)關(guān)頻率低于60KHz時(shí),導(dǎo)通損耗占主導(dǎo)地位;開(kāi)關(guān)頻率高于60KHz時(shí),以柵極驅(qū)動(dòng)損耗為主。在驅(qū)動(dòng)較大功率的同步整流器時(shí),要求柵極峰值驅(qū)動(dòng)電流IG(PK)≥1A時(shí),還可采用CMOS高速功率MOSFET驅(qū)動(dòng)器。同步整流替代肖特基整流后,可以有效減小在輸出功率中消耗的比例。采用同步整流技術(shù)是必須的。

在選擇AC/DC開(kāi)關(guān)電源時(shí),可以選用半橋或全橋新技術(shù),這樣可以使開(kāi)關(guān)電源效率提升到90%以上。當(dāng)然這些技術(shù)應(yīng)用,給led顯示屏供電是可以將電壓降至最佳狀態(tài),同時(shí)電源的效率也能達(dá)到高效率水平,因此采用新的電源技術(shù)給led顯示屏供電是可以達(dá)到顯著節(jié)能的效果。電源成本也肯定會(huì)有一些增加,

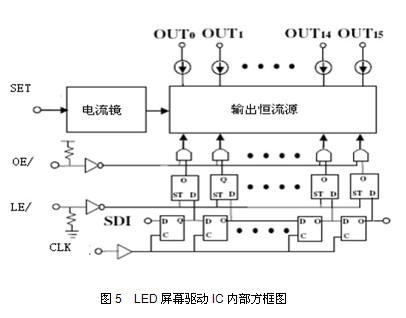

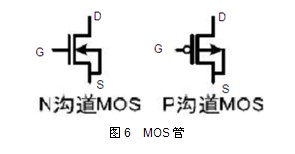

其次,我們可以仔細(xì)的研究一下led屏幕驅(qū)動(dòng)IC,如圖5所示輸出端為一個(gè)MOS開(kāi)關(guān)管(如圖6),控制輸出端口的關(guān)或者開(kāi),輸出端口壓降即VDS =0.65V左右,這是工藝和材料所決定,要把VDS 降為0.2V甚至0.1V,本身所需的面積必然增大。在MOS管的結(jié)構(gòu)中可以看到,在GS,GD之間存在寄生電容,而MOS管的驅(qū)動(dòng),實(shí)際上就是對(duì)電容的充放電。這個(gè)充放電的過(guò)程是需要段時(shí)間的,面積如果增加,在MOS管上的寄生電容也會(huì)隨之增大,如此,導(dǎo)致的后果就是整個(gè)IC的端口響應(yīng)速度下降,這對(duì)于一個(gè)LED屏幕驅(qū)動(dòng)IC將是致命的弱點(diǎn),因此,想從IC上入手,把轉(zhuǎn)折電壓降低,同時(shí)使驅(qū)動(dòng)IC有足夠的響應(yīng)速度,起決定作用的是工藝,這是是難以實(shí)現(xiàn)的。有人認(rèn)為可以采用其他的設(shè)計(jì)原理,但是如果是恒流IC,內(nèi)部電路是可能不一樣,但是通道端口的開(kāi)關(guān)管是必須存在的,所以即使采用其他的設(shè)計(jì)原理,要想達(dá)到電壓下降的目的也是難以實(shí)現(xiàn)的。

綜上所述,led節(jié)能顯示屏的實(shí)現(xiàn)主要是從供電電源上著手,在現(xiàn)有的LED顯示屏上直接采用半橋或全橋高效率開(kāi)關(guān)電源,再加上同步整流節(jié)能效果顯著。給驅(qū)動(dòng)IC恒流的狀態(tài)下盡量的減小電源電壓,通過(guò)紅綠藍(lán)各管芯分開(kāi)供電來(lái)達(dá)到更好的節(jié)能效果。當(dāng)然這種非標(biāo)準(zhǔn)電壓電源和新技術(shù)的應(yīng)用成本必然有所上升。從屏幕驅(qū)動(dòng)IC上看,節(jié)能并不明顯,減小驅(qū)動(dòng)恒流壓差還會(huì)帶來(lái)包括成本在內(nèi)的新的問(wèn)題。部分IC企業(yè)宣傳驅(qū)動(dòng)節(jié)能設(shè)計(jì),無(wú)非是出于銷(xiāo)售策略而已。