引言

信號傳輸一般可分為兩大部分:編碼與解碼。其中編碼要求根據(jù)所傳輸信號特點(diǎn)選擇合適的編碼方式。由于不同的信號在不同的環(huán)境中進(jìn)行傳輸,受到的干擾是不同的,而選擇合適的編碼方法可以最大限度的避免干擾,使通信更加順暢、更加準(zhǔn)確。

要實現(xiàn)不同的編碼方式關(guān)鍵是要找到合適的算法,并且要求算法必須簡潔亦兼容。筆者在這里主要采用了對比、聯(lián)合和模塊化的設(shè)計方法,使每一種編碼成為一個獨(dú)立模塊,但又共用同一個或多個時鐘。由此,大大節(jié)約了程序的存儲空間,減少了程序的調(diào)試時間。

文章將用VHDL設(shè)計八種常用的編碼方式,并運(yùn)用ALTERA公司的QUARTUSII設(shè)計軟件進(jìn)行仿真調(diào)試。QUARTUSII設(shè)計軟件是一款開放、與結(jié)構(gòu)無關(guān)、多平臺、完全集成化、豐富的設(shè)計庫、模塊化工具、支持各種HDL、有多種高級編程語言接口的非常先進(jìn)的EDA工具軟件。另外,超高速硬件描述語言VHDL具有強(qiáng)大的語言結(jié)構(gòu)、多層次的描述功能、良好的移植性和快速的ASIC轉(zhuǎn)換能力,支持硬件的設(shè)計、綜合、驗證和測試。因此,應(yīng)用VHDL設(shè)計通信編碼波形具有重要意義。

總體方案設(shè)計

方案總體設(shè)計如圖1所示。首先,在運(yùn)用VHDL編寫程序時必須遵照系統(tǒng)規(guī)則,按照系統(tǒng)庫函數(shù)調(diào)用,否則編譯將會產(chǎn)生問題。其次,考慮到分模塊編程,而每一種編碼方式的編程會用到不同頻率的時鐘,因此要將系統(tǒng)時鐘二分頻、四分頻和八分頻,以備需要。然后就是要設(shè)計選擇模塊,方便對八種編碼的自由選擇。再進(jìn)行 各個編碼模塊的VHDL編碼,進(jìn)而可以逐個編譯仿真。最后,當(dāng)每一個模塊編譯仿真通過后,就是要將每一個獨(dú)立模塊程序整合在一起,形成總的編碼程序,并且調(diào)試總程序。

圖1 總體設(shè)計流程圖

單元模塊設(shè)計及調(diào)試

分頻模塊

工作原理

所謂分頻,就是將一個給定頻率較高的數(shù)字輸入信號,經(jīng)過適當(dāng)?shù)奶幚砗螅a(chǎn)生一個或數(shù)個頻率較低的數(shù)字輸出信號。分頻本質(zhì)上是加法器的變化,其計數(shù)值由分頻常數(shù)N=fin/fout(fin是輸入頻率,fout是輸出頻率)決定,其輸出不是一般計數(shù)器計數(shù)結(jié)果,而是根據(jù)分頻常數(shù)對輸出信號的高、低電平進(jìn)行控制。

軟件設(shè)計

下面設(shè)計一個對輸入時鐘信號進(jìn)行2分頻、4分頻和8分頻的分頻程序。根據(jù)實際需要還可以設(shè)計分頻系數(shù)為2N的分頻器,只需要實現(xiàn)一個模N的計數(shù)器,再把模N的計數(shù)器的最高位直接付給分頻器的輸出信號,即可得到所需要的分頻信號。

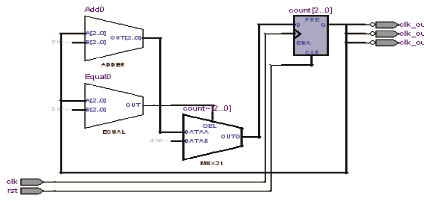

分頻系數(shù)是2的整數(shù)次冪的偶數(shù)分頻器模塊圖如圖2所示。

圖2 2、4、8分頻器的RTL模塊圖

此程序中rst為低電平有效,若實現(xiàn)2分頻電路則輸出最高有效位count(0),4分頻電路輸出最高有效位count(1),依次類推,8分頻輸出最高有效位count(2)。

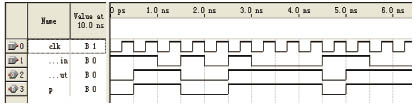

在MAX-plusII環(huán)境中編譯仿真波形如圖3所示。

圖3 2、4、8分頻波形

選擇模塊

工作原理

此模塊是用于選擇信號的,作用就是當(dāng)輸入多路信號時,只選取其中一路輸出,其選擇依據(jù)是根據(jù)其地址線的信號,地址線有N條,就能制作2N選一選擇器。

軟件設(shè)計

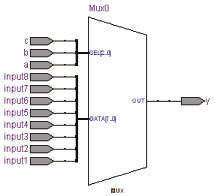

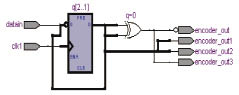

根據(jù)選擇模塊的工作原理,應(yīng)用VHDL編寫的選擇器模塊圖如圖4所示。

圖4 選擇器的模塊圖

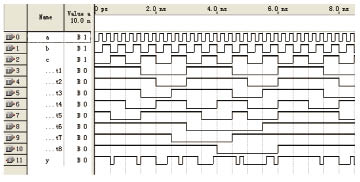

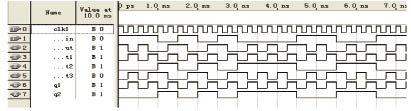

選擇器程序在QUARTUSII環(huán)境中編譯仿真波形如圖5所示。

圖5 選擇器波形

功能模塊

NRZ-L(不歸零碼)

NRZ-L(平)碼無論是“1”還是“0”時,相鄰碼元電平極性均不改變,即在4分頻的時鐘clk上升沿隨輸入信號din變化而輸出信號encoder-out。

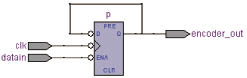

具體VHDL模塊圖如圖6所示。

圖6 NRZ-L(平)的模塊圖

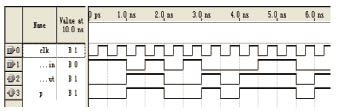

程序在QUARTUSII環(huán)境中編譯仿真波形如圖7所示。

圖7 NRZ-L碼波形

NRZ-M(信號差分碼)

NRZ-M信號差分碼,當(dāng)為“1”時相鄰碼元電平極性改變,“0”時相鄰碼元電極性不改變,即在時鐘clk為4分頻的上升沿遇輸入信號datain “1”而跳變,“0”保持輸出信號encoder-out。

具體VHDL模塊圖如圖8所示。

圖8 NRZ-M(信號差分碼)的模塊圖

程序在QUARTUSII環(huán)境中編譯仿真波形如圖9所示。

圖9 NRZ-M碼波形

NRZ-S(空格差分碼)

NRZ-S(空格差分碼),當(dāng)為“0”時相鄰碼元電平極性改變,“1”時相鄰碼元電極性不改變,即與NRZ-M(信號差分碼)恰好相反,clk為4分頻。

具體VHDL模塊圖如圖10所示。

圖10 NRZ-S(空格差分碼)的模塊圖

程序在QUARTUSII環(huán)境中編譯仿真波形如圖11所示。

圖11 NRZ-S碼波形

RZ(單極性歸零碼)

在歸零碼RZ中,碼元中間的信號回歸到0電平,因此任意兩個碼元之間被0電平隔開。當(dāng)為“1”時為“0”,當(dāng)為“0”時則為“0”,即輸入datain信號中間隔開,時鐘clk是2分頻,在上升沿遇“1”跳變,其它為“0”,輸出信號encoder-out。

具體VHDL模塊圖如圖12所示。

圖12 RZ(單極性歸零碼)的模塊圖

程序在QUARTUSII環(huán)境中編譯仿真波形如圖13所示。

圖13 RZ碼波形

積分曼徹斯特碼

曼徹斯特編碼是一種雙相碼。除了中間發(fā)生跳變外,當(dāng)為“0”時相鄰碼元電平極性改變,“1”時相鄰碼元電極性不改變,由于要將輸入datain信號中間跳變,故需兩個時鐘clk1、clk2,且clk1是4分頻,clk2是2分頻,都在兩時鐘上升沿遇“0”跳變,遇“1”保持,輸出信號encoder-out。

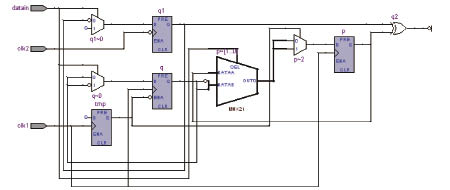

其具體VHDL模塊圖如圖14所示。

圖14 積分曼徹斯特碼的模塊圖

程序在QUARTUSII環(huán)境中編譯仿真波形如圖15所示。

圖15 積分曼徹斯特碼波形

雙相-M碼

雙相-M碼:除了相鄰碼元電平極性發(fā)生跳變外,當(dāng)為“1”時中間發(fā)生跳變,當(dāng)為“0”時中間不發(fā)生跳變,即時鐘clk1為4分頻,輸入信號datain相鄰碼元極性跳變,遇“1”時在時鐘clk1的上升、下降沿跳變,輸出信號encoder-out。

具體VHDL模塊圖如圖16所示。

圖16 雙相-M碼的模塊圖

程序在QUARTUSII環(huán)境中編譯仿真波形如圖17所示。

圖17 雙相-M碼波形

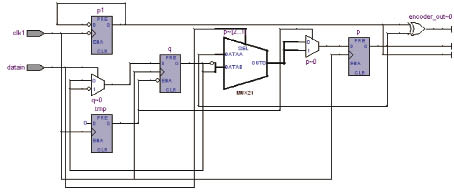

雙相-L碼

雙相-L碼,除了中間發(fā)生跳變外,當(dāng)為“1”時相鄰碼元電平極性改變,“0”時相鄰碼元電極性不改變,即需要2分頻時鐘clk1,datain信號中間遇時鐘clk1上升沿跳變外,且遇“1”相鄰碼元極性改變,“0”時不變,輸出信號encoder-out。

具體VHDL模塊圖如圖18所示。

圖18 雙相-L

程序在QUARTUSII環(huán)境中編譯仿真波形如圖19所示。

圖19 雙相-L碼波形

雙相-S碼

雙相-S碼,除了相鄰碼元電平極性發(fā)生跳變外,當(dāng)為“0”時中間發(fā)生跳變,當(dāng)為“1”時中間不發(fā)生跳變,即與雙相-L碼相反,clk1為4分頻。

具體VHDL模塊圖如圖20所示。

圖20 雙相-S碼的模塊圖碼的模塊圖

程序在QUARTUSII環(huán)境中編譯仿真波形如圖21所示。

圖21 雙相-S碼波形

整體程序調(diào)試

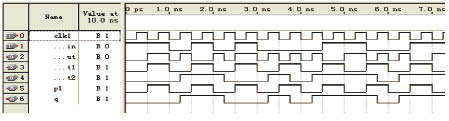

整體程序在MAX-plusII環(huán)境中的編譯仿真波形如圖22所示。

圖22 八種編碼波形

總結(jié)

1) 運(yùn)用VHDL編寫以上八種編碼是可行的。

2) 經(jīng)過觀察各模塊的仿真波形,符合各個編碼的特性。

3) 通過整體程序的調(diào)試仿真,并在FPGA上實現(xiàn)了波形的鍵選。