在路上似乎到處都有令人討厭的減速帶,,在行車道和停車場,隨處可見它們的身影,。盡管它們的尺寸大小不一,,但都一樣不討人喜歡。碰到這些減速帶時,,您可以選擇減速通過以減少對車輛的磨損,,也可以退回去,但最好的辦法是繞過去,。

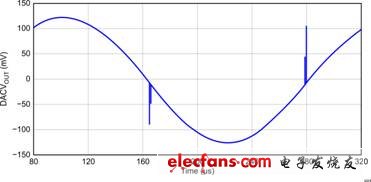

昨天,,在我減速通過一條討厭的減速帶時,突然想到了我的那個精密型 16 位 R-2R DAC,。它在中間刻度時存在短時脈沖波形干擾問題(請參見圖 1),。我想,在選擇使用具有較大短時脈沖波形干擾特性的 DAC 時,,可以在 DAC 輸出端添加一些去干擾電路,,從而減少干擾的影響。兩種常見的 DAC 去干擾電路是簡單的低通濾波器(相當于一種減速方法),,以及采樣/保持電路(相當于“繞過”干擾),。這兩種去干擾電路都可以降低干擾振幅,或者去除干擾能量,。

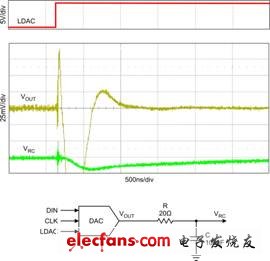

最簡單的 DAC 去干擾方法是在 DAC 放大器輸出端 (VOUT) 使用一個 R/C 濾波器(圖 2 底部),。這種濾波器可以降低干擾的振幅,但增加了建立時間,。

圖2頂部的曲線為DAC負載DAC(LDAC)引腳的信號,。利用DIN(數(shù)據(jù)輸入)引腳和CLK(時鐘引腳),便能夠以串行方式將一個數(shù)據(jù)字載入到 DAC 中,。一旦DAC 有了全部的數(shù)據(jù),,LDAC 引腳的升沿便將數(shù)據(jù)字載入內(nèi)部 DAC 寄存器。這樣便改變了 DAC 輸出電壓,。中間的曲線表示測得的 DAC 輸出中間刻度模擬干擾,。底部曲線表示使用一個 R/C 低通濾波器后測得的模擬信號。

一般而言,,這個過程會比較順利,。在您增加(或者減小)數(shù)據(jù)碼值時,輸出電壓也隨之上升(或者下降)。但在四分之一和四分之三中間刻度處,,DAC 會產(chǎn)生干擾,。中間刻度干擾最大。

要想確定正確的 R/C 比,,首先要查看干擾時間,,然后給您的濾波器選擇一個 3dB點,其比干擾頻率低 10 倍左右,。

例如,,圖 2 中干擾時間約為 1 μsec,經(jīng)過轉(zhuǎn)換得到 1 MHz 干擾時間,。由這種估算,,我們知道圖 2 中的 R/C 值構(gòu)建了一個 80 kHz 低通濾波器,。在選擇您的 R/C 值時,,請確定 R 足夠的低,以避免出現(xiàn)載入誤差,。

這種 R/C 濾波器解決了 R-2R DAC 干擾問題,,但它也并非是一頓“免費的午餐”。正如您在圖 2 底部曲線所看到的那樣,,R/C 濾波器延長了 DAC 的建立時間輸出信號,。

根據(jù)您不同的應用要求,簡單的R/C濾波器都可以奏效,。如果系統(tǒng)要求一個有干擾問題的R-2R DAC,,則開關(guān)電容解決方案結(jié)合 R/C 濾波器可能會是一種解決方案。