SOPC" title="SOPC">SOPC(System On Programmable Chip)技術(shù)是美國Altera" title="Altera">Altera公司于2000年最早提出的,并同時推出了相應的開發(fā)軟件Quartus II。SOPC是基于FPGA解決方案的SOC(System On Chip),構(gòu)成SOPC的方案也有多種。第一種是基于FPGA嵌入IP硬核的SOPC系統(tǒng),即在FPGA中事先植入嵌入式系統(tǒng)處理器,目前最常用的嵌入式處理器大多采用了含有ARM的32位知識產(chǎn)權(quán)處理器核的器件。第二種是基于FPGA嵌入IP軟核的SOPC系統(tǒng),目前最有代表性的軟核處理器分別是Altera公司的Nios II核,以及Xilinx公司的MicroBlaze核。第三種是基于HardCopy技術(shù)的SOPC系統(tǒng),HardCopy就是利用原有的FPGA開發(fā)工具,將成功實現(xiàn)于FPGA器件上的SOPC系統(tǒng)通過特定的技術(shù)直接向ASIC轉(zhuǎn)化。

1 基于Altera公司NiosⅡ" title="NiosⅡ">NiosⅡ軟核處理器的SOPC系統(tǒng)

Altera公司Nios II軟核是目前使用最為廣泛的一種軟核處理器。值得一提的是,利用Matlab和Altera公司的DSP Builder,用戶可以為Nios II軟核處理器設(shè)計各類DSP硬件加速器,并以指令的方式加入Nios II的指令集,從而可以構(gòu)建自己的DSP處理器系統(tǒng)。

1.1 基于NiosⅡ軟核處理器的SOPC系統(tǒng)結(jié)構(gòu)

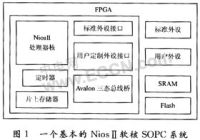

如圖1所示的一個基本的基于NiosⅡ軟核的SOPC系統(tǒng),除NiosⅡ核、定時器和片上存儲器以外,還需要在FPGA器件中添加一些接口元件。這些元件一方面通過片上的Avolon總線與NiosⅡ軟核相連,另外一方面又提供了外設(shè)與NiosⅡ軟核通信的接口界面。

Altera公司QuartusⅡ軟件中的SOPC Builder工具提供了許多常用的外設(shè)接口元件,如UART接口元件、PIO接口元件等,通過這些接口元件可以連接諸如RS232、LED、數(shù)碼管" title="數(shù)碼管">數(shù)碼管和按鍵等輸入輸出設(shè)備。在相對復雜的系統(tǒng)設(shè)計當中,還可以通過Avalon三態(tài)總線橋外接大容最的SRAM和FLASH,以提供更大的程序和數(shù)據(jù)存儲空間。從圖1中,還可以注意到,通過使用系統(tǒng)提供的用戶自定制外設(shè)接口元件的功能,用戶可以在系統(tǒng)中添加一個符合Avalon總線規(guī)范的外設(shè)接口元件,以連接用戶特定功能的外部設(shè)備。

1.2 自定制Avalon用戶外設(shè)接口元件簡介

對于自定制的Avalon外設(shè)接口元件按照Avalon總線操作的不同可以分為兩類:Avalon Slave外設(shè)接口元件型的自定制的Avalon Slave外設(shè)接口元件框圖。從圖2中可以看到寄存器的定義是自定制外設(shè)接口元件很重要的一部分,必須根據(jù)設(shè)計的需要確定寄存器的個數(shù)和種類。圖2中的Avalon Slave接口提供了自定制外設(shè)接口元件與NiosⅡ處理器之間數(shù)據(jù)交換的界面,其接口信號類型也必須根據(jù)設(shè)計的需要合理地進行選擇。常用的Avalon Slave接口信號類型有:clk,chipselect,address,write,writedata,byteenable,reset等。圖2中的任務(wù)邏輯具體說明了自定制外設(shè)接口的功能,并給出了與外設(shè)連接的接口信號。

自定制Avalon Slave外設(shè)接口元件的方法:可以利用SOPC Builder提供的元件編輯器在圖形用戶界面下將用硬件描述語言(Verilog或VHDL)描述的用戶邏輯封裝成一個SOPC Builder元件。相應的硬件描述語言文件給出了自定制外設(shè)接口元件的內(nèi)部寄存器結(jié)構(gòu),使用到的Avalon Slave接口信號和自定制外設(shè)接口的邏輯功能。一旦定制成功后,用戶自定制的外設(shè)接口就可以象SOPCBuilder中其他元件一樣被調(diào)用。

2 基于NiosⅡ軟核處理器的七段數(shù)碼管動態(tài)顯示設(shè)計

數(shù)字系統(tǒng)設(shè)計中,用數(shù)碼管顯示數(shù)據(jù)結(jié)果是常用的一種方法。利用Altera的SOPC Builder工具進行Nios Ⅱ系統(tǒng)設(shè)計時,并沒有提供專門的數(shù)碼管顯示接口元件,但可以使用PIO元件驅(qū)動數(shù)碼管顯示,不足之處是占用器件引腳數(shù)目過多。本文當中以自定制Avalon Slave外設(shè)接口元件的方式,給出了一種基于NiosⅡ軟核的七段數(shù)碼管動態(tài)顯示設(shè)計方案。該設(shè)計可以用來驅(qū)動1~8個共陰極(或共陽極)數(shù)碼管的顯示,可以根據(jù)需要選擇小數(shù)點顯示的位置,每個數(shù)碼管可以顯示0~F之間的十六進制字符。

圖3為自定制的數(shù)碼管動態(tài)顯示接口元件邏輯結(jié)構(gòu)圖,其中定義了2個寄存器display_data_reg和controlreg。display_data_reg是個一個32位二進制的數(shù)據(jù)寄存器,其數(shù)據(jù)每4位可以譯碼得到1個數(shù)碼管的七段顯示所需的字符碼,因此,display_data_reg同時最多可以給出8個數(shù)碼管所需要的顯示數(shù)據(jù)。control_reg是一個8位二進制的控制寄存器,但只定義了0~2位和第4位的含義。0~2位的數(shù)據(jù)給出了小數(shù)點顯示的位置,數(shù)值范圍在“000”~“111”之間,對應著8個數(shù)碼管最低位到最高位的小數(shù)點的位置。第4位是數(shù)碼管顯示的啟動停止位,當該數(shù)據(jù)位為1時,可使自定制接口元件所驅(qū)動的數(shù)碼管正常顯示結(jié)果;當該數(shù)據(jù)位為0時,停止顯示,所有被驅(qū)動的數(shù)碼管熄滅。

參數(shù)n定義了循環(huán)加法計數(shù)器的模數(shù),同時也決定了驅(qū)動數(shù)碼管顯示的個數(shù),其取值范圍在1~8之間。clkdisplay是循環(huán)加法計數(shù)器的時鐘輸入,他決定了計數(shù)器的計數(shù)頻率,同時也決定了數(shù)碼管顯示的動態(tài)掃描頻率。參數(shù)pos用于決定驅(qū)動數(shù)碼管的類型,其值可設(shè)定為0或1。當其值為0時,seg_out字符碼輸出高電平有效,bit_control數(shù)碼管位選控制輸出低電平有效,此時輸出結(jié)果用于驅(qū)動共陰極數(shù)碼管顯示;當pos值為1時,seg_out字符碼輸出低電平有效,bit_control數(shù)碼管位選控制輸出高電平有效,此時輸出結(jié)果用于驅(qū)動共陽極數(shù)碼管顯示。

seg_out為自定制元件的字符碼輸出,用于驅(qū)動數(shù)碼管顯示(包括小數(shù)點位)。其中,最高一位seg_out[7]用于驅(qū)動對應數(shù)碼管的小數(shù)點顯示,低7位seg_out[6..0]用于驅(qū)動數(shù)碼管的七段寧符顯示。圖3中數(shù)碼管七段譯碼器根據(jù)循環(huán)加法計數(shù)器的當前狀態(tài)值,從display_data_reg寄存器中選擇4位二進制數(shù)據(jù)進行譯碼。例如,當前驅(qū)動的數(shù)碼管的個數(shù)為5個(即n=5),循環(huán)加法計數(shù)器的當前狀態(tài)值用count表示,則count在0~4范圍內(nèi)變化;若計數(shù)器的當前狀態(tài)值count為2,則選擇寄存器display_data_reg[11..8]的4位二進制數(shù)據(jù)進行譯碼,若計數(shù)器的當前狀態(tài)值count為3,則選擇寄存器display_data_reg[15..12]的4位二進制數(shù)據(jù)進行譯碼,即總是選擇寄存器display_data_reg[(count+1)×4-1..count×4]的4位二進制數(shù)據(jù)進行譯碼。寄存器control_reg的低3位指明了小數(shù)點顯示的位置,如control_reg[2..0]的值為“000”,則第0位數(shù)碼管的小數(shù)點點亮,若control_reg[2..0]的值為“010”,則第2位數(shù)碼管的小數(shù)點點亮。因為,循環(huán)計數(shù)器的狀態(tài)值count反應了數(shù)碼管動態(tài)顯示過程中當前數(shù)碼管顯示的位皆,因此,數(shù)碼管小數(shù)點譯碼器只要比較control_reg[2..0]與count的值,若兩者相等,seg_out[7]輸山有效值(共陰極輸出為高電平,共陽極輸出為低電平)即可驅(qū)動對應數(shù)碼管的小數(shù)點點亮。

bit_control為自定制元件的位選控制輸出,其數(shù)據(jù)寬度為n位二進制,與要驅(qū)動的數(shù)碼管的個數(shù)是一致的。上面已經(jīng)提到,循環(huán)加法計數(shù)器的狀態(tài)值count反應了當前數(shù)碼管顯示的位置。因此,只要根據(jù)count的值,使得bit_control對應位輸出有效值即可。例如,n取值為5,pos取值為0(即驅(qū)動共陰極數(shù)碼管),若計數(shù)器的當前狀態(tài)值count為2,則bit_control的輸出結(jié)果為“11011”,若count為4,則bit_control的輸出結(jié)果為“01111”。

自定制元件的設(shè)計采用的是VHDL語言,其實體描述如下面程序所示:

從上面的程序可以看到:n和pos定義成了類屬變量,當完成接口元件的定制以后,類屬變量在自定制元件的設(shè)置窗口中將以用戶參數(shù)的形式出現(xiàn),如圖4所示,用戶可以設(shè)置其值。

實體描述當中除定義了自定制元件與外部設(shè)備的接口信號clk_display,seg7_out,bit_control信號以外,還定義了 Avalon Slave接口信號,NiosⅡ軟核通過這些信號訪問自定制元件中定義的寄存器。前面介紹的兩個寄存器display_data_reg和control_reg是在程序的結(jié)構(gòu)體說明部分定義的,具體語句如下:

signal display_data_reg:std_logic_vector(31downto 0);

signal control_reg:std_logic_vector(7 downto 0);

結(jié)構(gòu)體中還完成了所定義的兩個寄存器的數(shù)據(jù)寫入操作。圖3中所示的模n循環(huán)加法計數(shù)器、七段譯碼器、小數(shù)點譯碼器和位譯碼器也在結(jié)構(gòu)體中按上面所介紹的功能設(shè)計完成。

3 實驗結(jié)果

為了驗證用于驅(qū)動七段數(shù)碼管動態(tài)顯示的自定制元件功能,實驗中使用SOPC Builder建立了一個最簡單的NiosⅡ系統(tǒng)。該NiosⅡ系統(tǒng)添加了3個元件,名稱為cpu_0的NiosⅡ軟核處理器;名稱為seg7的自定制元件,用于完成數(shù)碼管的顯示驅(qū)動;名稱為onchip_RAM的片上隨機存儲器,存放調(diào)試時的程序代碼以及用作程序運行空間。生成的NiosⅡ系統(tǒng)的圖形符號如圖5所示,clk是系統(tǒng)工作時鐘輸入;reset_n是系統(tǒng)復位輸入,低電平有效;clk_display_to_the_seg7是數(shù)碼管掃描時鐘輸入,他決定了數(shù)碼管動態(tài)顯示的掃描速度;bit_control_from_the_seg7是位選控制輸出,決定了動態(tài)過程中哪一個數(shù)碼進行顯示seg7_out_from_the_seg7是數(shù)碼管顯示數(shù)據(jù)輸出,決定了數(shù)碼管顯示的內(nèi)容。

新建頂層原理圖,調(diào)用該NiosⅡ系統(tǒng),為其添加輸入輸出引腳,并定義引腳號,選擇目標器件型號為EP1C6Q240C8,編譯生成配置文件,并通過下載電纜下載到目標器件中。接下來利用NiosⅡIDE建立用戶程序。

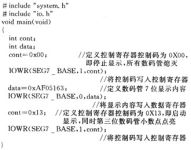

實驗建立NiosⅡ系統(tǒng)時,添加驅(qū)動七段數(shù)碼管顯示的自定制元件seg7時的參數(shù)n和pos(如圖4所示)設(shè)置成了兩種測試情況,分別用來驗證其驅(qū)動共陰極和共陽極數(shù)碼管顯示的情況。第一種測試情況將n設(shè)置成7,pos設(shè)置成0,用來驅(qū)動7個共陰極數(shù)碼管顯示。NiosⅡIDE建立的用戶測試程序如下:

程序編譯通過后,可以在硬件中調(diào)試運行程序。為了便于觀察測試結(jié)果,在ModelSim中運行仿真結(jié)果,得到仿真波形如圖6所示。仿真分析時系統(tǒng)工作時鐘(clk)設(shè)置為了50 MHz,數(shù)碼管動態(tài)顯示掃描頻率(clk_display)設(shè)置為1 kHz。圖6(a)給出了寄存器內(nèi)容的寫入過程,3個write高電平期間完成了 3次寄存器的寫入操作。第一次write高電平將0x00寫入address為1的寄存器(即控制寄存器,該定義是在自定制元件的硬件描述語言設(shè)計中完成的);第二次write高電平將0xAF05163寫入address為0的寄存器(即數(shù)據(jù)寄存器);第三次write高電平將0x13又寫入address為1的控制寄存器。當控制寄存器的內(nèi)容為0x00時,數(shù)碼管是停止顯示的,因此,在共陰極顯示的情況下bit_control的輸出全為高電平,直到控制寄存器的內(nèi)容寫入0x13后,bit_control才有輸出為低電平的情況(如圖6所示)。圖6(b)給出了寫入寄存器內(nèi)容以后的工作情況,當數(shù)據(jù)寄存器寫入0xAF05163、控制寄存器寫入0x13后,bit_control將從1111110到0111111循環(huán)變化,同時將數(shù)碼管顯示所需要的字符碼從seg7_out輸出。如當bit_control為1111110時,seg7_out輸出字符碼為0x4F,對應顯示“3”;當bit_control為1111101時,seg7_out輸出字符碼為0x7D,對應顯示“6”。由于控制寄存器寫入的內(nèi)容為0x13,即第三位數(shù)據(jù)管的小數(shù)點會亮起,因此當bit_control為1110111時,seg7_out輸出字符碼為0xED(即二進制的“11101101”),數(shù)碼管對應顯示“5”,而最高一位的“1”會讓該數(shù)碼管的小數(shù)點點亮。

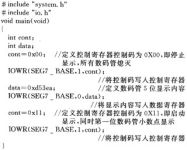

以上是第一種測試情況。第二種測試情況是將seg7的參數(shù)n設(shè)置成5,pos設(shè)置成1,用來驅(qū)動5個共陽極數(shù)碼管顯示。NiosⅡ IDE建立的用戶測試程序如下:

程序編譯通過后,同樣在Modelsim中運行仿真結(jié)果,得到仿真波形如罔7所示。仿真分析時系統(tǒng)工作時鐘(clk)設(shè)置為了50 MHz,數(shù)碼管動態(tài)顯示掃描頻率(clkdisplay)設(shè)置為1 kHz。

與第一種共陰極顯示情況相比,第二種共陽極顯示時的寄存器寫入過程是大體一樣的。不同之處在于共陽極顯示時的bit_control和seg7_out和輸出極性正好與共陰極顯示時的相反。

通過以上的實驗,驗證了自定制七段數(shù)碼管動態(tài)顯示接口元件功能的正確性。

4 結(jié) 語

在用Altera公司的SOPC Builder工具完成NiosⅡ軟核SOPC系統(tǒng)設(shè)計時,可以用SOPC Builder中提供的元件來構(gòu)建整個系統(tǒng)。但對于有些外部設(shè)備,SOPC Builder并沒有提供對應的接口元件,此時,就可以使用SOPC Build-er工具的自定制用戶元件功能來創(chuàng)建特定功能的接口元件。在本文中,針對數(shù)碼管的顯示,定制了一個七段數(shù)碼管動態(tài)顯示接口元件,可以用來驅(qū)動1~8個共陰極(或共陽極)數(shù)碼管的顯示,可以根據(jù)需要選擇小數(shù)點顯示的位置,每個數(shù)碼管可以顯示0~F之間的十六進制字符,并通過實驗驗證了其功能的正確性。