此外,電源管理芯片制造商僅僅把注意力集中在供電的管理方面。情況一般是這樣的,嵌入式處理器供應商給出輸入/輸出功率要求,功率半導體供應商則爭相開發(fā)出盡可能高效的滿足要求的 IC。然而,現(xiàn)在象開關穩(wěn)壓器這樣的電源管理 IC 效率已經(jīng)達到了 95% 的高峰。這迫使今天的電源 IC 供應商不僅要在價格上競爭,還要靠效率的每一點細微增長進行競爭。當前手機市場的發(fā)展趨勢顯示,這些傳統(tǒng)的方法已無法滿足業(yè)界對提升效率的需求。

盡管電池技術一直有穩(wěn)定改進,如更長的壽命及更小的體積,但這種發(fā)展仍然無法趕上下一代設計快速增長的功率需求。要在新產(chǎn)品中將電池壽命延長到最終用戶可以接受的水平,普通的電源管理方法已經(jīng)不能勝任了。

工藝技術的發(fā)展趨勢也加劇了電源管理的復雜性。過去,CMOS 晶體管在靜態(tài)時消耗功率很少,幾乎可以忽略不計。然而,隨著速度和密度的增加,工藝尺寸在不斷縮小,靜態(tài)功耗也在增長。根據(jù)估計,對于用 0.13 微米高速工藝實現(xiàn)的芯片,其靜態(tài)功耗要占總功耗的 15-20%。而且,隨著工藝技術進入 100 納米以下,靜態(tài)功耗將呈現(xiàn)指數(shù)式的增長,并將在處理器總功耗中占據(jù)主要部分。

有一種方法可以協(xié)調高性能與低功耗之間的矛盾,這就是讓處理器根據(jù)當前的工作負載,運行在不同的性能等級上。舉例來說,一個 MPEG 視頻播放器需要的處理性能比 MP3 音頻播放器高一個數(shù)量級。因此,當播放 MP3 時,處理器可以運行在較低頻率上,而仍然能保證播放的高質量。當時鐘頻率降低時,可以同時降低處理器的供電電壓,以達到節(jié)能的目的。

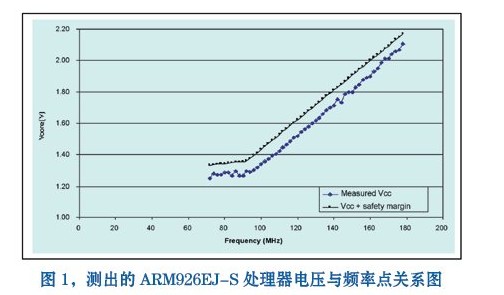

動態(tài)電壓調整技術 (DVS) 就利用了這樣一個事實,即 CMOS 工藝處理器的峰值頻率與供電電壓成正比。圖 1 顯示了頻率與電壓的關系,其中的測試使用了一個 ARM926EJ-S 處理器內核(0.18 微米工藝)。可以看到轉折點在大約 90 MHz,這是調整技術適用電壓范圍的一個限額。

以下是一個 CMOS 電路的近似功率方程:

P = CVDD 2fc + VDDIQ其中:

· P 為供電電壓 VDD 消耗的功率。

· C(VDD)2fc 是源于切換的動態(tài)功耗部分(C 是電容,fc 為頻率)。

· VDDIQ 是源于泄漏的靜態(tài)功耗部分(IQ 為泄漏電流)顯然,對一個給定負載,動態(tài)功率的量值與供電電壓的平方成正比。

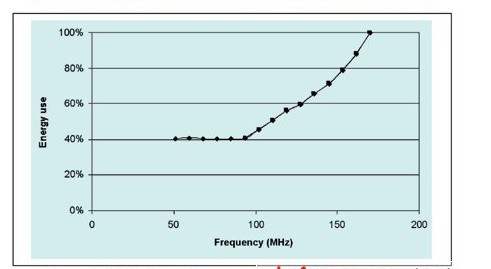

減少供電電壓并同時降低處理器的時鐘速度,功耗將會呈二次方的速度下降,代價是增加了運行時間。由于每次電池充電后其中儲存的能量是有限的,所以能量管理技術是唯一一種可以擴展電池使用壽命的方法。圖 2 顯示的是當頻率與電壓都從最高值下調時,等效的節(jié)能情況。因為電壓的下降不可能超過某一個最低限,所以即使把頻率降低到曲度以下也不能產(chǎn)生更多的節(jié)能效果。因此,能量管理技術也存在一個適用頻率范圍,在這個范圍內的電壓升降才是有效的(本例中約為 90-170 MHz)。

圖2 計算出ARM926EJ-S處理器節(jié)能與頻率關系圖

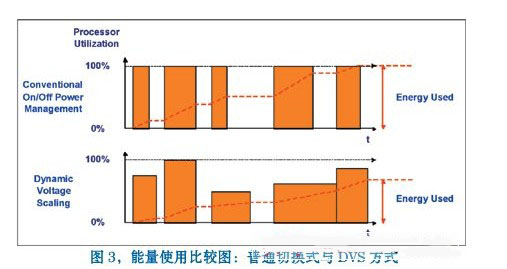

電壓控制和頻率控制的要求圖 3 比較了兩種電源管理方法的效果,一種使用動態(tài)電壓調整法(DVS),另一種是普通的門控電源管理方法。DVS 方法能顯著降低整體功耗。

一般來說,處理器運行得都太快了。例如,從 QoS 觀點來看,如果軟件只需要在一秒鐘內顯示完 30 幀視頻圖像,則處理器在半秒內就完成所有解碼是沒有意義的。提前完成任務的做法使能量利用效率較低。

取得性能與節(jié)能平衡的關鍵在于使用智能軟件,它可以把處理器的性能降低到正好滿足應用軟件需求底線的水平。這種軟件應該包括“性能設定”算法,由該算法來確定處理器運行的最佳性能級別,并且管理象 DVS 這樣的性能調整技術。

現(xiàn)有的 DVS 系統(tǒng)使用的是開環(huán)控制技術,CPU 的特性是通過給定時鐘速度和電壓下的工作量來確定的,并留有足夠的余量來適應溫度、供電和晶圓工藝的變化。

嵌入式處理器被設計成能在寬廣的溫度范圍內工作和適應不同的硅工藝。因此,必須采用較高的安全裕度,才能在電源效率降低時確保足夠的安全工作范圍。隨著供電電壓逐步轉向 1.2V 或更低,所需安全裕度的百分比也隨之增加,以覆蓋溫度及硅片工藝的各種變化。

CMOS 電路的速度會隨溫度的升高而減慢,這一效應必須算到供電電壓安全裕度里,雖然一般的工作溫度都是室溫。由于工藝技術的變數(shù)很多,如不同內核、不同晶圓、不同批量甚至不同代工廠都各不相同。為了保證高的產(chǎn)量,這些保護帶(guard-b ands)可以相當寬,從而對總體功耗有顯著的影響。

可以用大量的特性來構建一個頻率與電壓對照表,以確保在所有工作條件下都能滿足性能要求。然后把一個確定的電壓/速度集合以硬編碼方式寫到芯片中。在實際工作中,SoC 上定制的軟件驅動通過一個專門的硬件接口來設定所需電壓級別。在改變時鐘頻率前,必須通過一個定時器或其它方法來檢查穩(wěn)定電壓狀態(tài)(VDD_OK)。

自適應電壓調整(AVS)方法是一種閉環(huán)控制技術,它比 DVS 有明顯的改進。AVS 采用固有的對工藝與溫度變化的補償,簡化了電壓調整的方法,不再需要頻率/電壓表。這種技術的實現(xiàn)需要與嵌入式處理器協(xié)同使用幾個硬件性能監(jiān)控器,由它們接收從性能設定算法送來的更改性能級別的請求。這些性能監(jiān)控器可以準確地監(jiān)控內核內外的工藝與溫度變化情況,并且通過標準接口與外部的能量管理單元(EMU)進行通信。

ARM國家半導體能量管理解決方案ARM公司一直在研究一種對性能調整硬件進行智能控制的解決方案。美國國家半導體公司則一直在研究一種智能控制供電電壓、簡化 DVS 方法以及通過 AVS 減小安全裕度的解決方案。兩家公司現(xiàn)在已經(jīng)可以給電池供電設備的開發(fā)商提供一種端到端的方案。

ARM 公司的 Intelligent Energy Manager(智能能量管理器,IEM)解決方案以一個軟件部件為中心,即 Intelligent Energy Management 軟件。IEM 軟件與運行在應用軟件下的操作系統(tǒng)(OS)相互銜接,使用從 OS 內部架構獲得的參數(shù),通過正在運行的應用程序“指導” OS 的使用。可以用一些復雜的軟件算法來評價不同類型的軟件活動,然后產(chǎn)生一個對未來性能的預測。每個預測結果用一個評測棧來加總,以確定出一個總體的性能預測。

策略棧的工作情況顯示在圖 4 中。每個算法都把自己的預測作為一種性能級別 (PeRF.)送進棧中,每個預測都有一個相關的指令指出當前預測的權重,如果信任水平為低則 IGNORE(放棄該預測),如果為高則 SET(指定該預測),SET_IFGT 表示如果該預測的信任水平在棧中為最高,則應該使用該水平。當系統(tǒng)中發(fā)生某特殊事件時,例如一次任務切換,則要從棧底開始向上重新對不同的預測進行評估,以導出一個唯一的總體性能預測。

與 IEM 軟件一起聯(lián)合工作的是 Intelligent Energy Controller(智能能量控制器,IEC)部件。IEC 是一個 APB 外設,它可以快速地集成到任何基于 AMBA 規(guī)范的 SoC 設計中。IEC 使用精密計數(shù)器和定時器測出當前的系統(tǒng)性能水平,并將其送給軟件,以確保處理器的性能永遠能夠滿足軟件工作負荷的最低要求。它還將大部分軟件測量活動下載給硬件,從而減少了處理器上 IEM 軟件的開銷。

IEC 部件還提供一個對性能調整硬件的抽象。從軟件的角度看,當工作負載變化而且預測被修改時,才向 IEC 提交一個新的性能級別請求。這種性能級別的實現(xiàn)則用抽象方法對軟件進行隱藏。ARM 的 IEM 軟件部件優(yōu)化功耗的性能設定算法是基于工作負荷的差異,與之類似,國家半導體的 PowerWise 技術也根據(jù)當時的環(huán)境狀況以及各器件間的工藝差異,通過調整運行參數(shù)來確保處理器不會在最差的情況下工作。

國家半導體用于自適應電壓調整或動態(tài)電壓調整的 PowerWise 技術的核心是一個低門數(shù)、綜合的數(shù)字部件,名叫 Adaptive Power CONtroller(自適應功率控制器,APC)。APC 包括硬件性能監(jiān)控器,它可以準確地監(jiān)控處理器的功耗,跟蹤溫度以及不同器件工藝的變化。APC 與片外能量管理單元(EMU)的通信通過一個雙線、雙向總線進行,這個總線叫 PowerWise 接口(PWI)。

圖 5 顯示了完整的端到端參考解決方案,它使用了 ARM 公司的 IEM 和 IEC 部件,以及國家半導體公司的 APC 和 EMU 部件。

由 ARM 的 IEM 預測出的總體性能級別通過 IEM 硬件部分的抽象層傳送給 APC。APC 自適應地調整供電電壓,以覆蓋內核工藝和當時的運行條件,滿足特定的性能要求。

在設計時 IEC 可以配置為連接到片上特別設計的時鐘管理單元(CMU)和 APC 部件。CMU 負責為處理器提供與所需性能級別相適應的時鐘頻率。APC 負責管理片外 EMU,為處理器內核提供能滿足所需性能級別的最低電壓,同時還要考慮當前內核工藝與溫度狀況。由 IEC 部件來協(xié)調管理時鐘頻率與電壓的變化,以保證任何時候兩者的組合都是有效的,并且不同性能級別之間的轉換要順利,而且在時鐘產(chǎn)生方案與外部 EMU 的限制下轉換要盡可能快。

能量管理的最大限度ARM 與國家半導體開發(fā)出了這些先進的能量管理解決方案,可 以協(xié)助 OEM 廠商實現(xiàn)他們的手持式電池供電產(chǎn)品的電池壽命最大化(電池壽命現(xiàn)在是最終用戶真正關心的幾個關鍵要素之一)。整個解決方案具有部件化的特性,這意味著該技術可以自我調整去適應各種性能調整硬件,包括 DVS 和 AVS。IEM 預測軟件決定了處理器可以運行的最低性能級別,同時通過 IEC 的幫助,也確保永遠不會低于軟件的最低界線。APC 用性能預測與外部 EMU 一起工作,使處理器運行在能保證應用軟件正確運行的最低電壓和頻率下。在已確定時鐘發(fā)生器、供電電壓動態(tài)范圍,以及混合應用軟件可用余量等限制條件下,這一完整的解決方案能將處理器的功耗降低到最低程度。

ARM 智能能量管理技術可以用于降低一個嵌入式處理器的能量需求,最高可達75%。國家半導體公司的 PowerWise 技術可以減小安全裕度,并進一步減少能耗,與開環(huán)電壓控制方案相比,在室溫下使用 AVS 可以再節(jié)省 45% 的能耗。通過模擬工作與測試芯片顯示,結合使用 IEM 和 PowerWise 技術可以把智能手機和 PDA 這類產(chǎn)品的總能耗降低 30%,這對增加電池壽命有相當大的好處,同時還可以減小產(chǎn)品體積或降低成本。

正如前面所說,在一個典型設計中,處理器只是許多耗能部件中的一個。當 IEM 和 PowerWise 技術進入實用時,預計它們將被用于在一片 SoC 中,用于控制其它器件。