利用FPGA實現(xiàn)大型設計時,可能需要FPGA具有以多個時鐘運行的多重數(shù)據(jù)通路,,這種多時鐘FPGA設計必須特別小心,,需要注意最大時鐘速率、抖動,、最大時鐘數(shù),、異步時鐘設計和時鐘/數(shù)據(jù)關(guān)系。設計過程中最重要的一步是確定要用多少個不同的時鐘,,以及如何進行布線,,本文將對這些設計策略深入闡述。

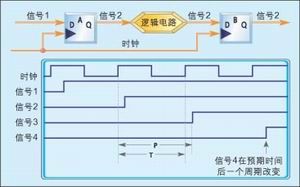

FPGA設計的第一步是決定需要什么樣的時鐘速率,,設計中最快的時鐘將確定FPGA必須能處理的時鐘速率,。最快時鐘速率由設計中兩個觸發(fā)器之間一個信號的傳輸時間P來決定,如果P大于時鐘周期T,,則當信號在一個觸發(fā)器上改變后,,在下一個邏輯級上將不會改變,直到兩個時鐘周期以后才改變,,如圖1所示,。

傳輸時間為信號在第一個觸發(fā)器輸出處所需的保持時間加上兩級之間的任何組合邏輯的延遲,再加兩級之間的布線延遲以及信號進入第二級觸發(fā)器的設置時間,。無論時鐘速率為多少,,每一個FPGA設計所用的時鐘必須具有低抖動特性。抖動S是觸發(fā)器的一個時鐘輸入到另一個觸發(fā)器的時鐘輸入之間的最大延遲,。為使電路正常工作,,抖動必須小于兩個觸發(fā)器之間的傳輸時間,。

圖2顯示了如果抖動大于傳輸時間(S>P)將出現(xiàn)的情況,該電路用時鐘的兩個上升沿來延遲信號1,。然而,,信號1上的一個改變會在相同的時鐘周期上傳輸?shù)降男盘?上,從而引起信號2的改變,。因為S>P,,電路將不能不正常。

須注意的是,,時鐘速率與傳輸延時并沒有什么關(guān)系,,甚至普通的100bps時鐘也會出現(xiàn)抖動問題。這意味著雖然FPGA供應商宣稱他們的芯片具有較短的傳輸時間和很高的時鐘速率,,但抖動問題可能會嚴重,,甚至那些沒有運行在最高速率上的設計也是如此。

好在FPGA供應商已經(jīng)認識到時鐘抖動的影響,,并在他們的芯片中提供低抖動的布線資源,。這些特殊的布線能夠在芯片中一個給定范圍內(nèi)的任何兩個觸發(fā)器之間提供一個確定的最大抖動。部分產(chǎn)品的低抖動資源覆蓋了整個芯片,,而其它的則可能只覆蓋了FPGA邏輯塊中的一個特定的行或列。對于一個需要很多不同時鐘源的設計,,這些低抖動FPGA是比較理想的選擇,。

多時鐘設計的最嚴重問題之一是用異步時鐘將兩級邏輯結(jié)合在一起。由于異步時鐘會產(chǎn)生亞穩(wěn)態(tài),,從而嚴重降低設計性能,,或完全破壞設計所能實現(xiàn)的功能。在觸發(fā)器的時序要求產(chǎn)生沖突時(設置時間和保持時間)將產(chǎn)生亞穩(wěn)態(tài),,觸發(fā)器的最終輸出是未知的,,并使整個設計處于不確定狀態(tài)。如果有一級邏輯要將數(shù)據(jù)異步地發(fā)送到另一級,,圖3所示的情形將不能滿足觸發(fā)器的設置和保持時間要求,。確切地說,如果設計中含有異步邏輯將有可能會產(chǎn)生亞穩(wěn)態(tài),。在處置異步資源時必需非常小心,,因為這可能產(chǎn)生一些很嚴重的問題。

多時鐘設計

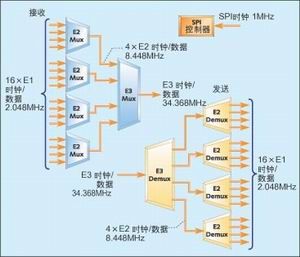

本文以電信應用中的E3多路復用/解復用設計為例,。如圖4所示,,多路復用器接收來自一組獨立線路接口芯片的16個獨立E1信道,每一個信道都工作于2.048MHz,;經(jīng)復用后,,這些E1流組合成4個E2流,,分別工作在8.0448MHz;4個E2流最后組合成一個E3流,,以34.368Mbps的速率串行發(fā)送出去,。在接收端執(zhí)行相反的操作:解復用器從E3流提取4個E2數(shù)據(jù)流,然后從E2流提取16個E1流,,最終將E1流發(fā)送到接收端的線路接口芯片,。

這些E1線路接口在發(fā)送和接收時都獨立工作,因此2.048MHz的時鐘速率可以有+/- 20ppm的偏差,。同樣,,因為大多數(shù)系統(tǒng)同時發(fā)送和接收數(shù)據(jù),分立的多路復用器和多路解復用器將提供2個獨立的E3流(發(fā)送和接收),。因此,,兩個34.368MHz的時鐘可以存在細微的差異。

由于E2流是在芯片上產(chǎn)生的,,這些E2多路復用器可以共享同一個8.448MHz時鐘,。然而,由于接收的數(shù)據(jù)速率與我們所設計的板無關(guān)(且不能假定所有E2多路復用器使用相同時鐘),,所以E2解復用器時鐘必須能工作在略為不同的速率下,。

此外,假定設計中需要一個由工作頻率為1MHz的處理器控制的獨立SPI(串行外圍接口)總線接口,,該接口用于狀態(tài)和控制,。這樣一來,設計中總共用了32個2.048MHz時鐘,,5個8.448MHz時鐘,,2個34.368MHz時鐘和一個1MHz時鐘,總共多達40個時鐘,。

本設計中最快時鐘是34.368MHz E3時鐘,。FPGA的最大時鐘速率的確定很重要,因為設計的差異將影響到該最大值,。然而,,在芯片商的資料手冊中常常可以看到“全局時鐘設置及保持時間”和“至CLB輸出的時鐘”兩個參數(shù),,將這兩個參數(shù)的最大值相加,,再增加25%就能可以得到最小時鐘周期的初略值,在最大時鐘速率條件下允許10%的余量,,以保證過熱條件下能正常工作,。因此,我們設置的最小速率為40MHz,,很多較新的FPGA都能夠很容易地支持該頻率,。事實上,,F(xiàn)PGA供應商已經(jīng)推出了超過300MHz的器件。

在確定了能滿足最大頻率要求的FPGA后,,就需要保證有足夠的空間來實現(xiàn)你的設計,。如果所選的FPGA沒有足夠的余量,就不能提供足夠的布線資源來滿足設計的時序約束,。通常芯片供應商宣稱的速率是最佳條件下的速率,,F(xiàn)PGA供應商一般建議FPGA邏輯在布線功能開始明顯變差以前可以用到80%。在選擇FPGA器件時,,建議在新的設計時最好使FPGA邏輯用到50%左右,,這樣就允許計算起始設計大小出現(xiàn)超差,以及為在設計起動后產(chǎn)生不可避免的設計變更留出空間,。如果最終的設計只占用低于50%的資源,,則可以使用同一系列中較小的FPGA以降低成本。

通過時序約束來規(guī)定慢時鐘速率,,從而可以改進設計中最快時鐘的布線,。在多路復用器例子中,如果設置FPGA布線工具SPI總線時鐘為1MHz,,而E3時鐘為40MHz,,布線工具將盡量使E3時鐘的邏輯電路模塊相鄰布局。如果由于空間的限制而不能將全部電路布局在一起,,則首先應將SPI邏輯另外布局,,因為SPI邏輯可以處理更長傳輸延遲。所有FPGA供應商的布線工具都能規(guī)定這些較慢時鐘速率,。

減少時鐘數(shù)量

根據(jù)市場調(diào)查,目前還沒有哪個FPGA器件能夠支持這種多路復用器/解復用器設計所需的40個時鐘,。所以,,我們必須減少所需要的時鐘數(shù)。

首先了解E2和E3多路復用器的時鐘,。前面已經(jīng)分析了4個E2多路復用器工作在相同時鐘下的可接受度,,E3多路復用器運行于比E2時鐘高得多的速率,必需使用一個不同的時鐘,。但是,,如果我們從E3時鐘中引出E2時鐘是否可行呢?因為E3多路復用器要從每個E2支路得到數(shù)據(jù),,我們可以在需要E2多路復用器給我們數(shù)據(jù)時,,簡單地將脈沖送給每個多路復用器。我們沒有去掉任何時鐘,,但E2時鐘現(xiàn)在是基于E3時鐘,。

如果在所有的多路復用器中也使用同樣的時鐘,,并且只使用一個使能信號來告訴E2多路復用器什么時候工作,這時會產(chǎn)生什么問題呢,?如果E3多路復用器用34.368MHz時鐘產(chǎn)生使能信號,,在這些使能信號上的抖動不會比用在FPGA中任何其它同步邏輯更大。所以,,使能信號可以使用正常(高抖動)布線資源,,這樣就不需要單獨的8.448MHz多路復用器時鐘,讀取E1數(shù)據(jù)緩沖器的數(shù)據(jù)時也是一樣,。換言之,,如果E2多路復用器需要數(shù)據(jù),它可以激活到特定緩沖器的使能信號,。到緩沖器的時鐘本身能夠保持E3多路復用器所用的34.368MHz時鐘,,如圖5所示。

最后,,我們檢查16個從線路接口芯片輸入到FPGA的E1時鐘,。這些時鐘有會產(chǎn)生下面幾個問題:首先,16個時鐘將占用太多可用芯片時鐘布線資源,;其次,,在同一個FPGA中使用16個異步時鐘來驅(qū)動相互鄰近的觸發(fā)器,由于地彈,、串擾和其它效應將產(chǎn)生噪聲問題,。例如,由于噪聲的原因,,一個正邊沿觸發(fā)器會在下降邊沿時改變輸出狀態(tài),,此類問題將難以處理。

作為一種可能的解決方案,,我們推薦使用一個最快的時鐘來對16個E1時鐘采樣,。16個輸入時鐘都接近2.048MHz,并且還有一個34.368MHz的系統(tǒng)時鐘,。這樣,,我們可以用34.368MHz時鐘來對16個E1時鐘分別進行采樣,并將結(jié)果存儲在一個16位存儲器中(每個E1時鐘一個位),。然后,,我們可以使用一個算法來檢測在E1時鐘上由低至高的轉(zhuǎn)換,為每一個E1數(shù)據(jù)信號產(chǎn)生一個使能信號,,并在下一個周期(34.368MHz)中存儲數(shù)據(jù),。

要成功實現(xiàn)這種方案,還必需了解時鐘-數(shù)據(jù)關(guān)系以避免在數(shù)據(jù)變化時對數(shù)據(jù)采樣,,參見圖6,。請注意在時鐘采樣電路的第一級中使用了兩個觸發(fā)器以確保在亞穩(wěn)態(tài)下正常工作,。另外需要注意的是,數(shù)據(jù)和時鐘必須具有相同時鐘周期數(shù)的延遲,。

我們已經(jīng)成功地將多路復用器的時鐘減少到一個時鐘,,同樣的方法可否用在解復用器呢?E3解復用器必須采用一個外部輸入時鐘,,這是因為驅(qū)動E3輸入數(shù)據(jù)的同一個片外器件利用到該時鐘,。由于E3解復用器知道在什么時候發(fā)送數(shù)據(jù)到E2解復用器,并能對每個E2解復用器產(chǎn)生使能信號,,而四個E2解復用器能工作在與E3多路復用器相同的主時鐘下,。同樣,E2多路復用器能夠為每個E1流產(chǎn)生使能信號,。

如果我們假設線路接口芯片能夠接受有間隙的時鐘(gapped clock),,一旦確定發(fā)出E1使能信號,我們只需要發(fā)送一個時鐘脈沖至線路接口。然而,,只需要簡單地發(fā)送使能信號本身至接口芯片而不必產(chǎn)生一個新的時鐘,。因為送至接口的數(shù)據(jù)將在使能信號的下降沿產(chǎn)生改變(參見圖5),我們需要確認接口在時鐘的上升沿進行采樣,。因為使能信號僅在線路接口芯片上而不是在FPGA內(nèi)用作一個時鐘,,就沒有必要在一個低抖動源中進行布線。注意這是在知道將再也不會用主時鐘的連續(xù)脈沖送數(shù)據(jù)到相同的從屬器件中時才這樣做,。

1MHz SPI時鐘并不能簡單去掉,,但我們現(xiàn)在通過使用使能信號和時鐘過采樣技術(shù),將原先40個時鐘減少到3個,,這樣我們就有了更大的器件選擇范圍,。

異步時鐘

在用異步時鐘產(chǎn)生任何邏輯前應該盡量先考慮采用其它替代方法,用異步時鐘的組合邏輯是產(chǎn)生亞穩(wěn)態(tài)問題的主要原因,。同樣,,當違反觸發(fā)器的設置和保持時間約束時,在一個短時間內(nèi)輸出將具有不確定性,,并且將最終設定在“1”或“0”上,確切的狀態(tài)不可預知,。

幸運的是對于亞穩(wěn)態(tài)性問題已經(jīng)有一些解決方案,。圖6說明了這一方案,這是一種雙寄存器方法:進入第一級觸發(fā)器的數(shù)據(jù)與時鐘異步,,所以第一級觸發(fā)器幾乎肯定是亞穩(wěn)態(tài),;然而,只要亞穩(wěn)態(tài)的長度小于時鐘的周期,,第二級觸發(fā)器就不會進入亞穩(wěn)態(tài),。但是,,F(xiàn)PGA供應商很少提供亞穩(wěn)態(tài)時間,盡管該時間一般小于觸發(fā)器的設置和保持時間之和,。

如果時鐘不是太快而且能滿足時序約束的話,,像圖6所示的電路將可能不會產(chǎn)生亞穩(wěn)態(tài)。只要所有輸出到觸發(fā)器的通路由相同時鐘驅(qū)動,,即使第一級觸發(fā)器的輸出可用,,通常還是需要用像圖6中電路來將亞穩(wěn)態(tài)隔離到一條短線。采用這種方法后,,將不太可能出現(xiàn)由于電路的改變而無意地在無時鐘驅(qū)動的邏輯中用到該亞穩(wěn)太線,。

如果讀數(shù)據(jù)的是一個計數(shù)器,像從一個異步FIFO讀或?qū)懙刂?,你應該考慮下列情況:一個傳統(tǒng)的3位計數(shù)器在狀態(tài)之間有一個,、兩個或三個位的變化,例如讀數(shù)發(fā)生在計數(shù)器從“011”到“100”變化的瞬間,,則所有三個位的值將不確定,,讀的值會是八種可能狀態(tài)中的任一種。如果計數(shù)器是使用格雷碼,,如表所示,,則每次僅有一位發(fā)生狀態(tài)改變,如果讀數(shù)發(fā)生在計數(shù)器變化的瞬間,,則只有一個位會有問題,,所以在讀操作中只有兩種可能結(jié)果,而且這兩種可能結(jié)果是計數(shù)器正好在讀以前的值和正好在讀以后的值時,。因為讀正好發(fā)生在計數(shù)器產(chǎn)生變化的瞬間,,你不可能確切地說哪個值是正確的,即兩者都應該認為是有效的,。

另一個避免異步時鐘問題的方法是忽略較慢的時鐘,,并用較快的時鐘來采樣。這需要數(shù)據(jù)有特殊的成幀特性(例如,,具有一個前導碼)來定義數(shù)據(jù)邊界,。這是一個常用的方法,在差不多每一個具有UART形式的嵌入式系統(tǒng)都有應用,。該方法是:采用一個非??斓臅r鐘,比如數(shù)據(jù)符號率的16倍,,在連續(xù)發(fā)現(xiàn)15個起始字符后開始采樣,,則下一個16(左右)位相當于送的第一個位,再下一個16(左右)位對應下一個位,并以次類推,。