摘 要:介紹了一種基于現(xiàn)場可編程門陣列(FPGA" title="FPGA">FPGA)的尺寸自動檢測方法,,同時給出了尺寸檢測" title="尺寸檢測">尺寸檢測結(jié)果的實時在屏顯示方法,。研究了基于FPGA的縱、橫向尺寸的檢測方法,,給出了系統(tǒng)的軟,、硬件設(shè)計,并進行了系統(tǒng)精度分析,。

關(guān)鍵詞:FPGA 視頻分劃" title="視頻分劃">視頻分劃 尺寸檢測

隨著自動化制造系統(tǒng)在各行各業(yè)的廣泛應用,,有效控制加工質(zhì)量,防止廢品產(chǎn)生,提高加工生產(chǎn)率和檢測精度被越來越多的企業(yè)所關(guān)注。工件尺寸精度是直接反映產(chǎn)品質(zhì)量的重要指標,。目前,,在有些方面雖然已實現(xiàn)了自動化,但仍有一些尺寸檢測或檢驗還處在人工階段,。人工檢測所需勞動量大,,易產(chǎn)生誤判,且檢測效率不高,,不方便進行質(zhì)量的統(tǒng)計分析,。隨著工件的批量化生產(chǎn),,這種檢測方法顯然是不合適的。

針對這些情況,,本文提出了一種基于FPGA的視頻檢測新方法,。本系統(tǒng)采用FPGA和VHDL語言實現(xiàn)。這種方法簡單易行,,減少了元器件使用數(shù)量,,不僅提高了測量精度和可靠性,而且避開了使用機器視覺技術(shù)的價格障礙,。其操作的靈活性和直觀的在屏顯示效果在很大程度上方便了工件質(zhì)量檢測和管理,。

1 系統(tǒng)構(gòu)成及基本原理

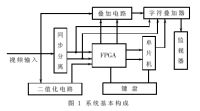

系統(tǒng)的組成框圖如圖1所示,經(jīng)過對待檢工件定位,、調(diào)節(jié)CCD攝像機等操作后,,使待檢工件成像清晰且位于監(jiān)視器中間。調(diào)節(jié)到位后,,F(xiàn)PGA模塊將利用視頻信號同步分離后得到的行,、場同步信號和奇偶場信號產(chǎn)生視頻橫、豎線的生成控制信號,,通過該控制信號控制疊加電路將視頻線疊加到監(jiān)視器顯示(其上下,、左右位置,長度及亮度均可通過鍵盤進行調(diào)節(jié)),。同時,,利用視頻線生成控制信號去控制視頻二值化信號以得到待檢部位尺寸信息。當視頻線位置調(diào)節(jié)到剛好使其跨躍工件的待檢部位時(不要使視頻線過長而伸到工件圖像的另一邊界外),,F(xiàn)PGA模塊將輸出代表待檢部位尺寸信息的脈寬信號,。鍵盤啟動檢測,單片機將對此脈寬信號進行計數(shù)采集,,并對計數(shù)值進行分析處理,,得出檢測結(jié)果和合格性分析結(jié)果,然后建立單片機與專用字符疊加芯片之間的通信,,把這些結(jié)果全部顯示在屏幕上,。不同的檢測結(jié)果伴有不同的閃爍提示,以提醒操作人員進行正確的操作,。

2 FPGA中各模塊功能原理

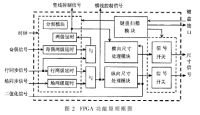

FPGA模塊主要功能包括以下幾個方面:視頻橫,、豎線的實現(xiàn)及其控制模塊,縱,、橫向尺寸信息處理模塊,,待檢尺寸類型處理模塊,鍵盤掃描模塊以及鍵值處理模塊,。其具體框圖如圖2所示,,粗虛線內(nèi)表示FPGA要實現(xiàn)的功能,,外界的都是輸入或輸出信號。

2.1 視頻豎,、橫線的生成原理

本系統(tǒng)中用于瞄準工件尺寸信息的視頻橫,、豎線是基于視頻分劃技術(shù)[1]生成的。視頻分劃的簡單描述如下:當電子束在屏幕上從左到右掃描時, 在某一行的電視信號上加一白色或黑色電平脈沖, 則在屏幕的相應位置上會出現(xiàn)一個白點或黑點,。同樣,,如果在整幅視頻圖像上按一定規(guī)律加上相應的白色或黑色電平脈沖,則會在屏幕上顯示出相應的幾何圖形來,。

依照視頻分劃原理,,如果從視頻信號的某一個行同步頭開始到另一個行同步頭結(jié)束,對這之間各行的行同步頭延時相同時刻后,,控制疊加電路在相應行的圖像信號上疊加相同寬度的白色或黑色電平脈沖,,則在屏幕上將產(chǎn)生一條亮或暗的豎線。實現(xiàn)方法如下:對輸入的視頻信號進行同步分離,,分離出行同步信號(H)和場同步信號(V),。通過對V和H分別進行兩級延時后相與就可以捕捉到連續(xù)幾行中的經(jīng)過延時后的行同步頭,即得到視頻豎線生成控制信號,。其中,,場信號第一級延時用來調(diào)節(jié)豎線在屏幕上的上下位置(延時越長,豎線越向下移),,場信號第二級延時用來調(diào)整豎線在屏幕上的長短(延時越長,,捕捉行同頻頭越多)。行同步信號第一級延時(延時短,,小于行同頻信號周期)用來調(diào)整豎線在屏幕上的左右位置,;第二級行延時(延時越長,豎線越粗)則用來實現(xiàn)豎線的粗細調(diào)整,。如果用視頻豎線生成控制信號去控制疊加電路,,就可以實現(xiàn)在視頻圖像上疊加一條豎線。

視頻橫線的生成原理與視頻豎線差不多,,可以把它看成是一條很短又很寬的豎線,它只是對一場圖像中的某一個行同步信號進行兩級延時,。實現(xiàn)方法如下:對輸入的視頻信號同步分離得到H,、V以及奇偶場信號。為了保證橫線的穩(wěn)定性,,本方案利用奇偶場信號來代替V,。利用奇偶場信號的上升沿(或下降沿)觸發(fā)來進行兩級延時,其中,,第一級延時用來調(diào)節(jié)橫線在屏幕上的上下位置,。為保證一場獲取一個行同步信號,,第二級延時時間的長度應該等于行同步信號周期(64us)。用第二級延時后的信號與 H 信號相與便可獲取一個行同步信號,。對這個行同步信號再進行兩級延時,,第一級延時調(diào)整橫線在屏幕上的左右位置;第二級行延時實現(xiàn)橫線的長短調(diào)整,。至此,,便得到了視頻橫線的生成控制信號。如果用它去控制疊加電路就可以實現(xiàn)在視頻圖像上疊加一條橫線,。

以上各級延時操作在具體設(shè)計時,,都設(shè)計成按鍵可調(diào)的,這樣可以方便地調(diào)節(jié)各視頻線的位置和長短,。

2.2 尺寸信息處理

與工件待檢尺寸信息聯(lián)系最緊密的是其邊界點的信息,,因此,對工件圖像信息中的邊界點的采集成為關(guān)鍵,。通常采用將視頻信號二值化[2]的方法,。為避免CCD周圍光照環(huán)境引起的干擾,本系統(tǒng)采用了浮動閾值的二值化技術(shù)對視頻信號進行預處理,。

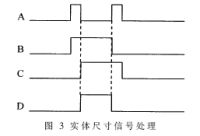

采集工件縱向尺寸信息的實現(xiàn)方法是使視頻豎線剛好跨躍待檢尺寸的兩端,,以視頻豎線生成控制信號作為敏感信號,以經(jīng)二值化處理后的視頻信號為輸入信號,,敏感信號上升沿變化啟動進程輸出一個信號等于此時輸入的二值化信號,,如此一場圖像掃描下來,就可將縱向間隙尺寸信號轉(zhuǎn)換成一個門信號,。如果檢測的是縱向?qū)嶓w尺寸,,則在經(jīng)上述處理后得到的只是如圖3所示的信號A。為將其轉(zhuǎn)化為脈寬信號,,還需進一步處理,,方法如下:以該信號為敏感信號,用兩個進程分別以它的上升沿和下降沿進行翻轉(zhuǎn),,如圖3中信號B,、C所示,再將二者相與即可得到代表尺寸信息的脈寬信號D,。為區(qū)別檢測的是間隙還是實體尺寸,,在外設(shè)有鍵盤進行切換。利用單片機對輸出的脈寬信號進行計數(shù),、處理,,便得到檢測結(jié)果。

采集工件橫向尺寸信息的實現(xiàn)方法是使視頻橫線剛好跨躍待檢測尺寸的兩端,,以橫線生成控制信號為敏感信號,,以二值化處理后的視頻信號為輸入信號,。當敏感信號為“1”時,進程輸出信號隨二值化信號變化,;當敏感信號為“0”時,,進程將輸出低電平。這樣得到的信號波形和縱向尺寸情況一樣,。若檢測的是間隙尺寸,,將輸出一個脈寬信號,若檢測的是實體尺寸,,輸出的也是如圖3所示信號A,,用同樣的方法處理可得檢測結(jié)果。

2.3 時鐘分頻和鍵盤掃描

時鐘分頻的功能是將系統(tǒng)提供的主時鐘進行分頻以提供其他模塊所需,。本系統(tǒng)主要為視頻線的產(chǎn)生和移動所需的延時進行了時鐘分頻,,同時為單片機的計數(shù)頻率也進行了時鐘分頻。在 FPGA 中,,時鐘分頻一般是通過 VHDL 語言的進程語句由計數(shù)器實現(xiàn)的[3],。

鍵盤掃描主要是為外部鍵盤提供接口,本系統(tǒng)中按鍵包括對視頻線的位置,、長度,、類型、亮度以及待檢尺寸類型等參數(shù)進行調(diào)整和選擇,,還為所疊加字符的相關(guān)參數(shù)進行設(shè)置和調(diào)整,,因此可以用 VHDL 設(shè)計一個4×4的動態(tài)掃描鍵盤[3]來進行各參數(shù)的控制。

2.4 疊加電路

本系統(tǒng)中疊加電路有兩部分,,一是視頻橫,、豎線與圖像的疊加,其實現(xiàn)方法是用動態(tài)視頻線的生成控制信號來控制疊加電路,,當控制信號為“1”時,,疊加電路輸出為一個可調(diào)灰度電平(在外設(shè)有控制旋紐來調(diào)節(jié)該電平)取代在相應行相應位置的圖像信號;當控制信號為“0”時,,疊加電路輸出為圖像信號,,由此實現(xiàn)在圖像信號上疊加視頻線。二是字符與視頻圖像的疊加,,它是通過專用字符疊加芯片uPD6450[4~5]來實現(xiàn)的,。uPD6450是一種可編程的字符疊加芯片,顯示的字符格式為12×18點陣,,內(nèi)部設(shè)有128字的固定字庫,提供多種顯示方式,,如閃爍,、背景選擇等,。

3 軟件設(shè)計

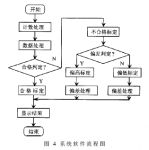

系統(tǒng)軟件部分由計數(shù)單元、數(shù)據(jù)處理,、合格分析,、偏差處理、顯示處理等單元組成,。主程序流程圖如圖4所示,。

為提高測量結(jié)果的準確性,在計數(shù)單元部分中對工件尺寸信息進行20場計數(shù)處理,,對所計數(shù)值進行乘當量,、取平均值等數(shù)據(jù)處理操作,得到檢測結(jié)果,。再對檢測結(jié)果與標準值進行比較,,進而得出合格性分析結(jié)果。同時,,在偏差處理部分還對不合格的結(jié)果進行了偏差判定,,最終分析出該結(jié)果相對于標準值是偏高還是偏低,并且偏高或是偏低標準值的具體數(shù)據(jù)也會計算出,。在顯示處理部分將把這些分析處理所得的所有結(jié)果都直觀地顯示在監(jiān)視器上,。

4 系統(tǒng)精度分析

為滿足檢測精度的要求,對系統(tǒng)的脈沖當量必需進行設(shè)計,其方法是用本系統(tǒng)對一個測量精度高的量具(如千分尺)進行原始數(shù)據(jù)采集,,若標準尺寸(L)所得計數(shù)值為n,,則可得脈沖當量為S=L/n。

將測量公式f=S·N(其中,,S表示脈沖當量,, N表示計數(shù)值)代入脈沖當量計算式有f=(L·N)/n,則檢測精度表達式為:

由上式可以看出影響測量精度的因素有標準器的精度(?啄L)和計數(shù)精度(?啄n,、?啄N),。選用精度高(?啄L小)的標準器一般對系統(tǒng)精度影響不大,,?啄n和?啄N受計數(shù)頻率和定位精度影響,。考慮到計數(shù)頻率的穩(wěn)定性,,其頻率不宜選得過高(過高會影響計數(shù)誤差,,起不到明顯效果),也不能選得過低(過低時脈沖當量太大,,若有一個或半個計數(shù)值的誤差會對系統(tǒng)造成較大影響),。一般根據(jù)實際需求調(diào)整CCD的放大率和計數(shù)分頻時鐘,使脈沖當量值高于所需精度值。其次,,如果改進系統(tǒng)的定位精度將進一步提高檢測精度,。

通過大量實驗表明,該方法在1~8mm的尺寸范圍內(nèi)能獲得較好的檢測效果,,檢測精度都優(yōu)于0.01mm,,而且重復測量精度高,檢測速度快,。若為適應其他精度要求,,只需調(diào)整CCD的放大率和 FPGA 模塊中的計數(shù)分頻時鐘部分的VHDL 程序即可。因此,,這種方法特別適合于生產(chǎn)線上縱,、橫向尺寸的自動化檢測。

5 應用

利用上述原理應用于電能表磁推高度自動檢測,,取得了比較滿意的效果,。電能表磁推高度的標準尺寸為1.2±0.1mm,公差帶寬度為0.2mm,則檢測精度為±0.02mm,,大量實測表明本方法測量精度高于0.02mm,排除上料的時間,,檢測速度優(yōu)于 1個/秒,在檢測速度和檢測精度上都優(yōu)于傳統(tǒng)的人工檢驗方法,。各種檢測結(jié)果的在屏顯示情況如圖5所示,。

圖5(a)表示待檢電能表磁推高度合格,屏幕上將顯示電能表磁推高度標準值和所檢測的結(jié)果,,同時顯示該電能表的合格性結(jié)果,,圖中第三行的“PASS”字樣會閃爍以提示操作人員進行分選操作。

圖5(b)或(c)表示待檢電能表磁推高度不合格,,相對于標準值偏低(或偏高),,屏幕上除了顯示電能表磁推高度標準值和所檢測的結(jié)果之外,還顯示偏差結(jié)果,,并且顯示偏低(或偏高)標準值下限(或上限)多少,。同時屏幕中的“LOW”(或“HIGN”)和“FAIL”字樣也會顯示,以提示操作人員正確操作,。

本文基于FPGA研究了尺寸自動檢測原理,,并將該原理應用于電能表磁推高度的自動檢測,取得了很好的效果,,表明該技術(shù)應用于實踐能夠大幅度地提高檢測速度和檢測效率,。本系統(tǒng)支持ISP技術(shù),方便功能拓展而不用添加新的外圍電路,,并且易操作,,顯示結(jié)果直觀,、靈活,在實際中可減少人為因素造成的誤判,,減輕了勞動強度,。

參考文獻

[1] 張慶生,,李錦玲.光電瞄準具中的視頻分劃生成技術(shù).光學技術(shù), 2001(7).

[2] 王慶有. CCD應用技術(shù).天津: 天津大學出版社, 2000.

[3] 辛春艷.VHDL硬件描述語語言.北京:國防工業(yè)出版社,2002.

[4] 孫洪波,,楊兆選,楊同實. OSD芯片uPD6450及其應用.電子技術(shù)應用,,1997,,23(4).

[5] uPD6450 Video Design Guides.NEC,2001.