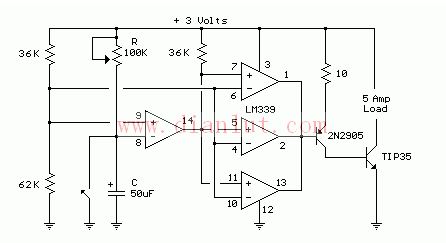

低電壓,高電流延時(shí)電路設(shè)計(jì)

摘要: 本電路由LM339四個(gè)電壓比較器用來產(chǎn)生時(shí)間延遲和控制在低電壓高電流輸出。比較器的三個(gè)平行的有線駕駛中型功率PNP晶體管(2N2905或類似)這反過來又驅(qū)動(dòng)高電流NPN晶體管(TIP35或類似)。

Abstract:

Key words :

本電路由LM339四個(gè)電壓比較器用來產(chǎn)生時(shí)間延遲和控制在低電壓高電流輸出。 比較器的三個(gè)平行的有線駕駛中型功率PNP晶體管(2N2905或類似)這反過來又驅(qū)動(dòng)高電流NPN晶體管(TIP35或類似)。

第四個(gè)比較器用來產(chǎn)生時(shí)間延遲后,常閉開關(guān)打開。兩個(gè)電阻(36K和62K)用作分壓器,適用于大約三分之二的電池電壓三分之二的(+)比較器輸入,或約2伏。延遲時(shí)間后,打開開關(guān)將圍繞一個(gè)時(shí)間常數(shù)使用50uF電容和100K的可變電阻,或約(50u * 10萬)= 5秒。時(shí)間可以通過調(diào)整電阻降低到一個(gè)較低的值或使用較小的電容器。較長的時(shí)間可以得到一個(gè)更大的電阻或電容。操作上更高的電壓電路,10歐姆的電阻應(yīng)增加比例,(4.5伏= 15歐姆)。

系統(tǒng)原理圖

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。