引言

隨著通信與廣播電視業(yè)務(wù)的發(fā)展,無線電頻譜迅速、大量的被占用,頻道擁擠和相互間干擾日趨嚴(yán)重,為了能有效地利用無線電頻譜,減少相互間的干擾,信號監(jiān)測業(yè)務(wù)隨之成為必要。調(diào)幅廣播信號監(jiān)測系統(tǒng)是用于實時監(jiān)測短波調(diào)幅廣播信號的調(diào)幅度、載波頻率的專用系統(tǒng)。

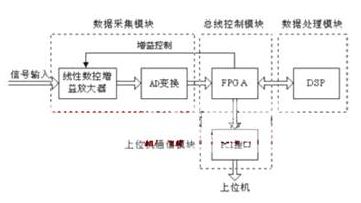

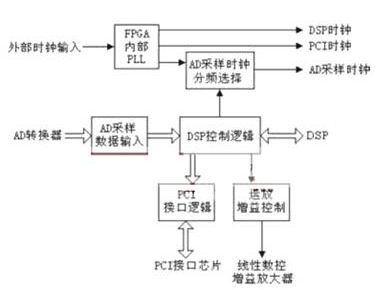

圖1為調(diào)幅廣播信號質(zhì)量監(jiān)測系統(tǒng)的系統(tǒng)框圖。本系統(tǒng)由數(shù)據(jù)采集模塊、總線控制模塊、數(shù)據(jù)處理模塊、上位機(jī)通信模塊組成。其工作方式為:輸入信號通過線性數(shù)控增益放大器后由A/D轉(zhuǎn)換器采樣,采樣后的數(shù)據(jù)由FPGA送入DSP進(jìn)行數(shù)據(jù)處理,所得到的監(jiān)測結(jié)果由FPGA通過PCI接口送入上位機(jī)。同時由DSP對采樣所得信號大小進(jìn)行監(jiān)測,通過FPGA對線性數(shù)控增益放大器的增益進(jìn)行調(diào)整,使其輸出信號滿足系統(tǒng)測量要求。

圖1:監(jiān)測系統(tǒng)框圖

算法和數(shù)字處理軟件

調(diào)幅廣播信號的特點(diǎn)是載波頻率相對穩(wěn)定而調(diào)幅度實時變化,所以系統(tǒng)每監(jiān)測一百次調(diào)幅度再監(jiān)測一次載波頻率同樣可以達(dá)到監(jiān)測信號的目的。系統(tǒng)所要監(jiān)測的信號的帶寬小于10kHz,頻率范圍為1.5MHz~30MHz。若對信號進(jìn)行過采樣,為保證測量精度則采樣頻率要達(dá)到240MHz,后續(xù)數(shù)據(jù)處理難度較大,所以系統(tǒng)選擇對信號進(jìn)行欠采樣。采樣點(diǎn)數(shù)為N=4096。

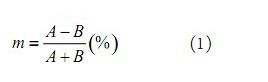

調(diào)幅信號調(diào)幅度的計算公式如下:

計算公式

其中m為調(diào)幅度,A為包絡(luò)上、下兩正峰間的幅度,B為包絡(luò)上、下兩負(fù)峰間的幅度。

本系統(tǒng)中先用頻域移相法求得A/D采樣后信號的Hilbert變換,然后取絕對值即可得到AM信號的上包絡(luò)。因為單音調(diào)幅信號的上、下包絡(luò)關(guān)于零軸對稱,所以只要得到上、下包絡(luò)其中之一就能根據(jù)式(1)求得調(diào)幅度。

設(shè)輸入信號為f(t),則由采樣定理可知采樣前信號的頻譜F(w)和采樣后信號的頻譜FS(w)有如下關(guān)系:

計算公式

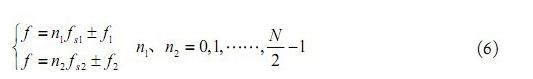

輸入信號最高頻率為30MHz,系統(tǒng)選取最小公倍數(shù)為60MHz的兩個采樣頻率分別為fs1、fs2(fs1=60/264MHz=0.228MHz、fs2=60/261MHz=0.230MHz)對信號進(jìn)行采樣,對采樣后的信號作FFT變換,與fs1和fs2相對應(yīng)的頻率分別為f1=fs1×n1/N和f2=fs2×n2/N。由此可粗略的得到信號的載波頻率為:

計算公式

進(jìn)而為了達(dá)到1Hz的測量精度,必須進(jìn)行頻譜細(xì)化。若要達(dá)到0.5Hz分辨率,則分析200Hz譜寬需要計算400點(diǎn)。在粗估計頻率的前后100Hz內(nèi)進(jìn)行頻率細(xì)化分析,分別對f1和f2作n1和n2周圍400點(diǎn)的DFT變換。變換后得到頻譜F1和F2,分別求出其幅度最大值對應(yīng)的位置nF1和nF2,從而得到精估計的信號頻率值和:

計算公式

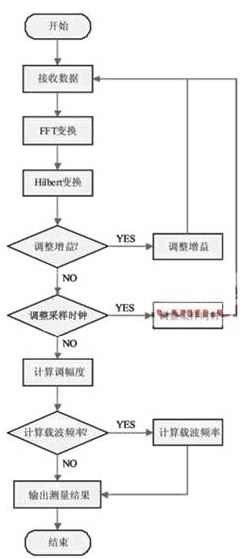

根據(jù)上述算法可得到DSP中數(shù)據(jù)處理軟件的流程圖(圖2)。

DSP中數(shù)據(jù)處理軟件的流程圖

FPGA邏輯設(shè)計

本系統(tǒng)中FPGA主要用來協(xié)調(diào)各個模塊間的數(shù)據(jù)傳輸,分別為A/D采樣數(shù)據(jù)到DSP的傳輸、DSP計算結(jié)果到PCI接口的傳輸以及數(shù)控增益放大器的增益控制。同時FPGA還為系統(tǒng)工作提供了必要的時鐘、復(fù)位信號、控制信號(圖3)。

FPGA邏輯圖

器件選擇

A/D轉(zhuǎn)換器是整個監(jiān)測系統(tǒng)的關(guān)鍵部件,它的性能往往直接影響整個監(jiān)測系統(tǒng)的技術(shù)指標(biāo)。當(dāng)A/D有效位數(shù)大于12位時量化損失為0.0055dB,其對測量精度的影響可忽略不計。系統(tǒng)選用的A/D轉(zhuǎn)換器為ADI公司的AD9433。輸入AD9433的信號幅度要控制在一定的范圍內(nèi),否則會造成失真,甚至燒毀芯片,所以要在AD9433之前用運(yùn)放對信號幅度進(jìn)行調(diào)控。同時根據(jù)調(diào)幅廣播信號幅度實時變化的特點(diǎn),要求所選擇的運(yùn)放增益可變。基于上述要求系統(tǒng)選用ADI公司的線性數(shù)控增益放大器AD8320。

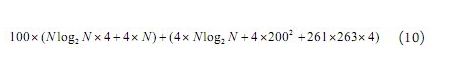

系統(tǒng)對信號采樣點(diǎn)數(shù)為N=4096,算法采用Hilbert變換解調(diào)求調(diào)幅度和欠采樣求載波頻率,所以每計算100次調(diào)幅度和1次載波頻率所需要的運(yùn)算量大概為:

計算公式

本系統(tǒng)選用ADI公司SHARC系列的ADSP-21262作為數(shù)據(jù)處理芯片。

根據(jù)ADSP-21262性能可估算出系統(tǒng)完成一次調(diào)幅度測量所需要的時間大概為800μs,完成一次載波頻率測量所需要的時間大概為10ms,可以滿足系統(tǒng)實時性要求。

在總線控制模塊中,系統(tǒng)選用Altera公司Cyclone II系列中的EP2C8Q208C8 FPGA芯片。

PCI接口模塊選用PLX公司的PCI總線控制芯片PC19054。

結(jié)語

本文介紹了一種基于DSP的調(diào)幅廣播信號監(jiān)測系統(tǒng),采用了數(shù)字信號處理的方法,與模擬監(jiān)測技術(shù)相比處理更加靈活、測量精度更高、并且大大提高了系統(tǒng)的可靠性。本系統(tǒng)已成功應(yīng)用于實踐,經(jīng)過實踐檢查,載波頻率測量精度達(dá)到1Hz,調(diào)幅度測量精度達(dá)到3%,測量效果滿足實際需要。