摘要:為了實現(xiàn)基于DSP的H.264視頻編碼器的實時性能,提出了一系列優(yōu)化實現(xiàn)方法。首先結(jié)合TMS320DM6437硬件特點,描述了X264代碼向TMS320DM6437平臺的移植過程和優(yōu)化方法,重點介紹了整數(shù)DCT變換和量化的線性匯編編寫及匯編級優(yōu)化。實驗結(jié)果表明,本編碼器實現(xiàn)了cif'格式視頻的實時編碼,Dl格式視頻的編碼速率也達(dá)到了18 fps,基本滿足視頻監(jiān)控系統(tǒng)中編碼器的需求。

H.264作為新一代多媒體視頻編碼標(biāo)準(zhǔn),采用了許多先進(jìn)的技術(shù),在編碼效率和性能大幅度提高的同時,增加了抗誤碼及網(wǎng)絡(luò)白適應(yīng)等功能,廣泛地應(yīng)用于視頻電話、移動視頻和流媒體等場合。傳統(tǒng)上進(jìn)行音視頻開發(fā)一般使用視頻編解碼ASIC芯片的方法,但是這種方法開發(fā)周期長、適應(yīng)性差,而近年出現(xiàn)的高性能DSP(數(shù)字信號處理器)就很好的解決了這些問題且產(chǎn)品性能更穩(wěn)定,所以筆者采用TI公司專門推出的高性能DSP平臺TMS320DM6437(簡稱DM6437)數(shù)字媒體處理器來實現(xiàn)H.264視頻編碼器[21。X264是一款支持H.264標(biāo)準(zhǔn)的開源編碼器代碼,是南網(wǎng)上自由組織聯(lián)合開發(fā),注重實用,與另外兩種開源代碼JM和T264相比,在不明顯降低圖像質(zhì)量的基礎(chǔ)上,大大降低了計算復(fù)雜度,廣泛應(yīng)用于視頻壓縮和格式轉(zhuǎn)換領(lǐng)域,兇此本文選擇開發(fā)源代碼X264(20081113版)進(jìn)行研究。

基于DM6437平臺實現(xiàn)H.264編碼器,需要通過改進(jìn)算法或者重新進(jìn)行資源配置,以滿足應(yīng)用環(huán)境的要求。筆者重點研究了H.264編碼器在以TMS320DM6437為日標(biāo)的CCS平臺上的移植和優(yōu)化工作,包括C語言級的優(yōu)化、算法優(yōu)化、整數(shù)DCT變換和量化的線性匯編編寫以及匯編級優(yōu)化等。

1 H.264視頻編碼器的構(gòu)建

1.1 X264編碼器到DM6437的移植

X264編碼器支持H.264的基本檔次以及主要檔次的某些功能選項和功能模塊,代碼尺寸非常龐大,視頻編碼速度相當(dāng)慢。在對X264源碼研究過程中,發(fā)現(xiàn)在視頻編碼質(zhì)量下降不是很明顯的情況下,可以將一些功能模塊刪除,以減小代碼尺寸,加快編碼速度。此項工作在文獻(xiàn)[3-4]中均有詳細(xì)講解,讀者可根據(jù)實際情況進(jìn)行調(diào)整應(yīng)用。筆者利用TI公司提供的CCS3.3 (Code Composer Studio)平臺,將裁剪后的X264模型移植到DM6437平臺上。

1.2 視頻采集

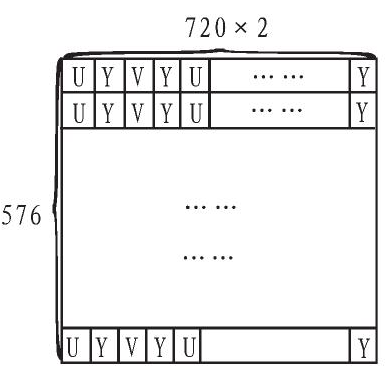

DM6437數(shù)字媒體處理器中的視頻處理前端(VPFE)具有視頻采集功能,可以將CCD攝像頭采集的RGB圖像轉(zhuǎn)換為符合BT.656規(guī)范的YUV4:2:2圖像。采集完的視頻數(shù)據(jù)在內(nèi)存中的數(shù)據(jù)結(jié)構(gòu)如圖l所示。

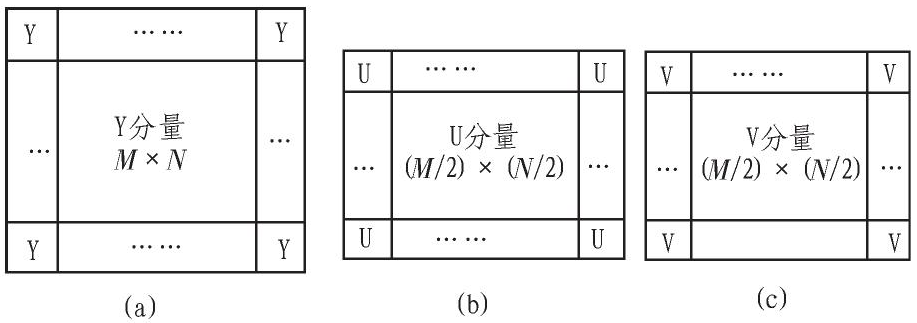

在進(jìn)行H.264視頻編碼時,必須調(diào)整原始視頻的數(shù)據(jù)結(jié)構(gòu)。如果對Dl格式的視頻進(jìn)行編碼,Y分量數(shù)據(jù)不變,U分量和V分量數(shù)據(jù)做垂直方向的2:1亞采樣,轉(zhuǎn)換成360x288的分辨率;如果對cif'格式的視頻進(jìn)行編碼,需要對Y分量進(jìn)行水平和垂直方向的2:1亞采樣,轉(zhuǎn)換成352x288分辨率,同時對U分量和V分量進(jìn)行水平方向的2:1亞采樣和垂直方向上的4:1亞采樣,轉(zhuǎn)換成176x144的分辨率。圖2為經(jīng)過調(diào)整后的Y、U、V各分量的數(shù)據(jù)結(jié)構(gòu)。

圖l DM6437的VPFE所采集視頻數(shù)據(jù)的數(shù)據(jù)結(jié)構(gòu)

圖2調(diào)整后視頻數(shù)據(jù)的數(shù)據(jù)結(jié)構(gòu)

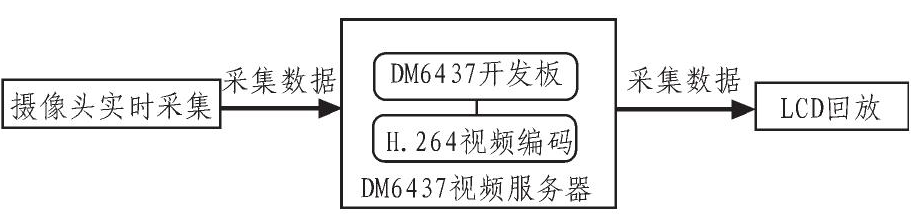

(注:圖中MxN是Y分量的分辨率,U、V分量的分辨率為( M/2)×( N/2),若為Dl格式,M=720,N=576;若為cif格式,M=352,N=288)1.3 LCD回放DM6437視頻處理子系統(tǒng)中的視頻處理后端(VPBE)負(fù)責(zé)將符合BT.656規(guī)范的YUV4:2:2數(shù)據(jù)轉(zhuǎn)換成RGB數(shù)據(jù),兇此可以與LCD顯示器進(jìn)行無縫連接。在攝像頭采集和|L264編碼工作完成以后,本文提出LCD回放模塊,進(jìn)行重建圖像回放,便于觀察效果。基于DM6437實時視頻采集的H264視頻編碼器系統(tǒng)框圖如圖3所示。

圖3系統(tǒng)框架示意圖

H.264編碼器在DM6437上的優(yōu)化剛構(gòu)建好的基于DM6437的H.264編碼器很慢,難以滿足視頻監(jiān)控需求,必須對其進(jìn)行優(yōu)化,提高處理性能。對H264編碼程序主要從系統(tǒng)優(yōu)化、算法優(yōu)化和匯編優(yōu)化3個方面進(jìn)行。

2.1系統(tǒng)優(yōu)化系統(tǒng)優(yōu)化主要是對ccs提供的各種編譯參數(shù)進(jìn)行選擇、搭配、調(diào)整。主要從以下幾個方面進(jìn)行優(yōu)化:l)編譯器的優(yōu)化。首先設(shè)定合適的編譯選項,控制編譯器生成更高效、代碼尺寸更小的匯編代碼。文中設(shè)計的H.264編碼器所用到的編譯選項包括:-pm,-op2,-03,-mt,-mh,-k等。2)DSP/BIOS的配置.、在DM6437的開發(fā)中,CaChe和EDMA等功能的應(yīng)用已不能單純通過在程序中調(diào)用相關(guān)API來實現(xiàn),必須在有DSP/BIOS進(jìn)行管理的條件下才能正常T作,此時就涉及到存儲空間的合理配置,為了最大化DM6437的存儲性能,本文通過進(jìn)行多次配置后編碼器T作性能的比較,將LIP配置為32 kB的LIP-Cache.將LID配置為32 kB的LIDCaehe和48kB的LIDSRAM,將L2配置為64 kB的L2Cache和64 kB的L2SRAM。在DM6437中配置Cache過程包括:Ll和L2Cache大小的設(shè)置,模式的設(shè)置,以及外部存儲器DDR可被高速緩存的設(shè)置。3)任務(wù)調(diào)度。文中設(shè)計的H.264視頻編碼器中采集和回放過程的主要操作是數(shù)據(jù)搬移,可以用EDMA3來實現(xiàn),進(jìn)而解放CPU來專心進(jìn)行編碼T作。兇此設(shè)置一個任務(wù)即可。

2.2算法優(yōu)化H.264數(shù)字視頻編碼標(biāo)準(zhǔn),具有很高的壓縮性能,但其運算復(fù)雜度是H.263標(biāo)準(zhǔn)的3倍以上,所以需要采用算法來降低運算復(fù)雜度。其中比較常用的方法是在幀內(nèi)/幀間預(yù)測過程中采用快速算法,降低模式選擇的次數(shù):或者是對H.264中采用的Lagrangian率失真優(yōu)化模型進(jìn)行化簡,提高運算的速度。除上述方法之外,全零塊預(yù)判算法也是有效手段之一。

在低碼率視頻應(yīng)用中,常見的是運動緩慢的具有靜止背景的圖像,靜止背景經(jīng)過DCT和量化后往往所有系數(shù)都為零。被判斷為全零塊的圖像塊可以省去DCT和量化兩個環(huán)節(jié)而降低運算量、節(jié)約運算時間。因此基于H.264編碼器的預(yù)判零方案如圖4所示。

圖4 H.264編碼器預(yù)判零方案

由于H.264中的幀間模式有16x16、16x8、8x16、8x8、8x4、4x8、4x4 7種模式,所以在運動搜索過程中,零塊的判決閥值也要隨幀間模式的變化而發(fā)生變化,不同塊模式(MxN塊)的零塊判決閥值可以定義為:

(1)

(1)

其中,M、N=4、8或16, 是MxN塊中4x4塊的個數(shù),即為MxN/16。

是MxN塊中4x4塊的個數(shù),即為MxN/16。

根據(jù)以上的分析,基于最佳零塊判決的運動搜索算法,在進(jìn)行運動搜索時,加入停止搜索條件,對根據(jù)運動矢量計算出來的每個子塊的SAD值進(jìn)行全零塊判決,這個判決門限由(1)決定,若當(dāng)前MxN塊的SAD小于門限值,則提前結(jié)束對該子塊的運動搜索,并跳過其后的變換和量化操作:否則與常規(guī)的運動搜索過程相同。

新的AZBs檢測方法可歸納如下:

1)檢查當(dāng)前M×N塊的SAD值是否小 ·THl的值。

·THl的值。

如果是真的,判定該M×N塊不是全零塊,否則轉(zhuǎn)到步驟2);

2)檢查當(dāng)前M×N塊的SAD值是否小于 ·THO的值。

·THO的值。

如果是真的,判定該M×N塊是全零塊,否則轉(zhuǎn)到步驟3):

3)執(zhí)行DCT/Q模塊。

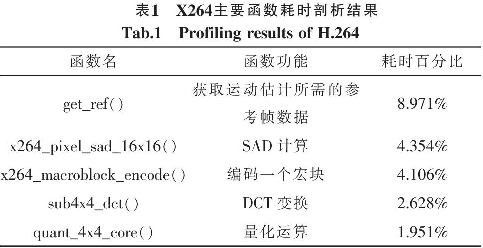

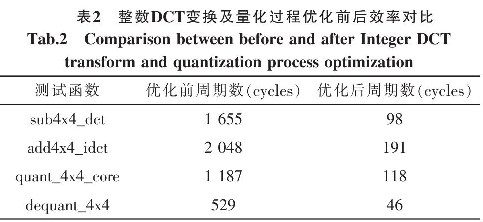

2.3匯編優(yōu)化文中在CCS3.3中用profile T具對H.264程序進(jìn)行剖析,結(jié)果如表1所示,可發(fā)現(xiàn)H.264標(biāo)準(zhǔn)中運動估計、DCT變換、量化等是最耗時的部分。

對這些耗時部分主要采用以下2種方式進(jìn)行優(yōu)化:

1)內(nèi)聯(lián)函數(shù)(intrinsics)優(yōu)化 內(nèi)聯(lián)函數(shù)是C6000編譯器提供的可以直接映射成為內(nèi)聯(lián)(inline)匯編指令的特殊函數(shù),這樣就可以提高應(yīng)用程序的性能。由于上述函數(shù)都很適合運用數(shù)據(jù)打包和SIMD(單指令多數(shù)據(jù))操作,而6000編譯器提供的內(nèi)聯(lián)函數(shù)中有很多相關(guān)的函數(shù)接口,因此將這些費時函數(shù)全部用內(nèi)聯(lián)函數(shù)進(jìn)行改寫,例如要進(jìn)行4x4塊的量化操作,需要16次循環(huán),要進(jìn)行16次取數(shù)據(jù),16次乘法,16次加法,16次移位操作。dct數(shù)組元素寬度為16位,可以利用_memd8()函數(shù)一次讀取4個數(shù)組元素,這樣可將讀取數(shù)據(jù)次數(shù)減為4次,并在外層循環(huán)體內(nèi)使用其他intrinsics函數(shù)一次對兩個DCT數(shù)組元素進(jìn)行處理,從而拆解了內(nèi)層循環(huán)。

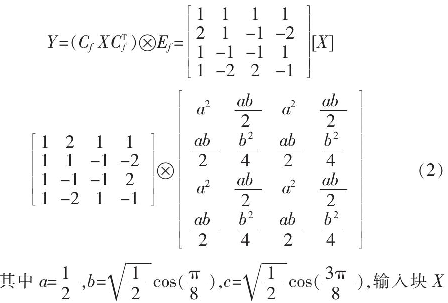

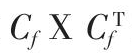

2)線性匯編優(yōu)化 整數(shù)DCT變換及量化過程在H.264編碼器代碼中占用了大概20%~25%的時間,對該部分進(jìn)行匯編級優(yōu)化,可提高編碼器的性能。整數(shù)DCT變換的關(guān)鍵函數(shù)sub4x4_dct用于計算殘差塊并對殘差塊進(jìn)行整數(shù)DCT變換;add4x4_idct函數(shù)是其逆過程,作用是對反量化后的系數(shù)進(jìn)行反DCT變換,并將反變換后的系數(shù)矩陣與預(yù)測塊矩陣疊加。以sub4x4_dct函數(shù)為例,對整數(shù)變換的線性匯編級優(yōu)化過程進(jìn)行說明。整數(shù)變換的公式見(2)式。

為4x4殘差矩陣,即待編碼塊src與pred預(yù)測塊的差值,見(3)式。

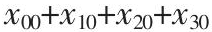

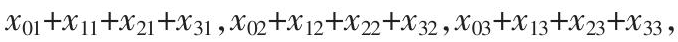

首先使用兩次LDNW指令從指定存儲器中讀出src和pred中的第一行數(shù)據(jù),使src00和src01,src02和src03,pred00和pred01,pred02和pred03分別存放在同一個寄存器中。然后使用兩條SUB2指令進(jìn)行對應(yīng)像素的減運算,得到X矩陣的第1行元素。重復(fù)以上操作3次就得到整個殘差矩陣。接著使用6次ADD2指令計算 ,可得

,可得 ,

, ,依次類推,可以計算出剩余的3行。最后在

,依次類推,可以計算出剩余的3行。最后在 這個運算中,使用PACK2和PACKH2指令來對數(shù)據(jù)進(jìn)行重新打包,完成數(shù)據(jù)的交換。

這個運算中,使用PACK2和PACKH2指令來對數(shù)據(jù)進(jìn)行重新打包,完成數(shù)據(jù)的交換。

整數(shù)DCT4x4蝶形變換過程中,將二維整數(shù)變換轉(zhuǎn)換為兩次一維的變換,先進(jìn)行水平變換,水平變換后的系數(shù)按列存放,垂直變換就轉(zhuǎn)換成系數(shù)矩陣的水平變換。兇此,水平變換和垂直變換可以調(diào)用相同的程序來完成。

對量化函數(shù)采取匯編優(yōu)化后,把 和MF值用表的形式存儲,要使用這兩個參數(shù)時,從表中讀取i_qscale的對應(yīng)值。整數(shù)DCT變換及量化過程優(yōu)化前后的效率如表2所示。

和MF值用表的形式存儲,要使用這兩個參數(shù)時,從表中讀取i_qscale的對應(yīng)值。整數(shù)DCT變換及量化過程優(yōu)化前后的效率如表2所示。

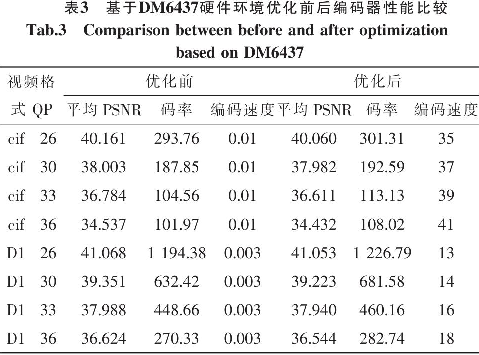

3 實驗結(jié)果文中對經(jīng)過移植和優(yōu)化后的H.264編碼器進(jìn)行實驗驗證,選取具有代表性的視頻序列akiyo(背景簡單,景物運動緩慢)進(jìn)行編碼,視頻為YUV 4:2:0格式,采用IPPP ……編碼模式,DM6437的時鐘頻率為600 MHz,對于cif'和Dl視頻格式的圖像在不同QP值下測試的結(jié)果如表3所示。

(注:平均PSNR的單位為dB.碼率單位為kbit/s,編碼速度單位為fps)對表3進(jìn)行分析可以看出,在PSNR和碼率沒有引起明顯變化的情況下,H.264編碼器的編碼速度獲得了極大的提高,其中cif格式視頻編碼已經(jīng)滿足實時性要求,同時Dl格式在QP=36時編碼速度達(dá)到了18 fps,這樣的編碼性能基本可以滿足視頻監(jiān)控系統(tǒng)中的應(yīng)用。

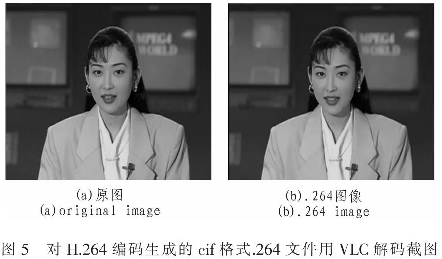

編碼結(jié)束后生成的.264文件存到PC機,可以用VLCplayer進(jìn)行解碼播放。解碼播放出來的圖像如網(wǎng)5所示。

圖5為用VLC播放cif格式的akiyo視頻文件的截圖,圖(a)表示akiyo視頻原文件截圖,圖(b)表示經(jīng)過H.264編碼器編碼的akiyo視頻文件截圖,由截圖的畫面質(zhì)量可以看出,圖像質(zhì)量沒有明顯下降,整個畫面有不明顯的噪點(臉部).顏色偏暗,證明此H.264編碼器對于cif格式的視頻文件編碼效果較好。

4 結(jié) 論

文中首先在DM6437上構(gòu)建了H.264視頻編碼器,編碼器主要分為攝像頭實時采集、H.264編碼、LCD回放3個部分,組成一個完整的可觀看編碼效率和效果的系統(tǒng)。將X264編碼器移植到DM6437平臺之后,對DM6437硬件資源及性能進(jìn)行深入研究,分別從C語言級、系統(tǒng)級、算法級、整數(shù)DCT變換和量化的線性匯編編寫以及匯編級等方面進(jìn)行優(yōu)化,最終實現(xiàn)了cif'格式視頻的實時編碼,基本滿足視頻監(jiān)控系統(tǒng)中編碼器的需求。本文介紹的針對DM6437平臺的H264編碼器移植、優(yōu)化的思路和方法,對構(gòu)建高效的視頻應(yīng)用平臺具有一定的參考價值。