0 引 言

增量式碼盤是一種原理簡單,抗干擾能力強(qiáng),可靠性高,適合于長距離傳輸?shù)奈恢门c速度測量裝置,已成功應(yīng)用于大量的控制系統(tǒng)中,極大地提高了其位置控 制精度。理論上,只要測得碼盤輸出信號的頻率,即可得到被測軸的轉(zhuǎn)速,并且可以得到比模擬方法更高的測量精度。本文以增量式碼盤為基礎(chǔ),設(shè)計(jì)實(shí)現(xiàn)一種在較 寬速度范圍都有較高精度并且有良好反應(yīng)速度的速度、位置測量裝置。

利用增量式碼盤的反饋脈沖信號測量速度的典型方法有3 種: M 法、T 法和M/ T 法。其中,M 法是直接計(jì)取給定采樣周期內(nèi)的反饋脈沖數(shù)來測量速度的,低速時(shí)會(huì)因?yàn)槊}沖數(shù)少而影響測速精度; T 法是通過測量兩個(gè)相鄰反饋脈沖的間隔時(shí)間來測量速度的,高速時(shí)則因?yàn)槊}沖間隔短而導(dǎo)致精度不高; M/ T 法結(jié)合了前兩種方法的優(yōu)點(diǎn),在大致相等的采樣間隔內(nèi),計(jì)取Cm 個(gè)反饋脈沖,并同時(shí)計(jì)取這Cm 個(gè)反饋脈沖間隔內(nèi)插入的高頻時(shí)標(biāo)信號數(shù)Cf ,經(jīng)計(jì)算得到速度測量值。M/ T 法雖然克服了前兩種方法的缺點(diǎn),但仍存在低速時(shí)采樣時(shí)機(jī)不確定,精度不高等問題,這給定周期采樣的數(shù)字伺服控制系統(tǒng)帶來很大的不便,所以又出現(xiàn)了變M/ T 法等方法,以進(jìn)一步改善M/ T 法的性能和實(shí)用性[ 12] 。

本文利用FPGA 實(shí)現(xiàn)了一種改進(jìn)的M/ T 法,克服經(jīng)典M/ T 法的不足,其測速電路與控制器間的數(shù)據(jù)接口形式有PCI 總線和雙端口RAM,便于在高性能控制系統(tǒng)中使用。

1 總體方案

根據(jù)控制系統(tǒng)的實(shí)際情況,所設(shè)計(jì)的測速板具有位置測量和速度測量功能,如圖1 所示,由倍頻辨向模塊、改進(jìn)M/ T 法測速模塊、PCI 從設(shè)備控制器三個(gè)部分組成。

圖1 總體設(shè)計(jì)方案。

1. 1 倍頻辨向

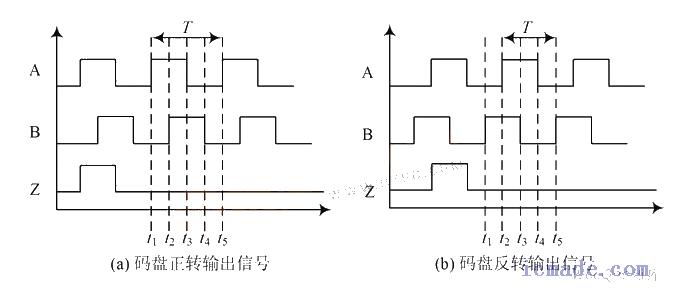

增量式碼盤的典型輸出是兩個(gè)相位差為90°的方波信號A,B 以及零位脈沖信號Z( 見圖2) 。

圖2 增量式碼盤輸出。

A,B 之間的相位關(guān)系標(biāo)志被測軸的轉(zhuǎn)向,即當(dāng)正轉(zhuǎn)時(shí)A 相超前B 相90°,反轉(zhuǎn)時(shí)B 相超前A 相90°。對于每個(gè)確定的碼盤,其脈沖周期T 對應(yīng)的碼盤角位移固定為,故其量化誤差為/ 2 。如果能將A,B 信號四倍頻,則計(jì)數(shù)脈沖的周期將減小到T / 4,量化誤差下降為θ/ 8,從而使增量式碼盤的角位移測量精度提高4 倍。從圖2 可知,根據(jù)A,B 兩方波信號之間相位關(guān)系的4 次變化,即可產(chǎn)生四倍頻信號和辨向信號,這樣就可以實(shí)現(xiàn)增量式碼盤測量精度的提高 。

1. 2 改進(jìn)的M/ T 測速算法

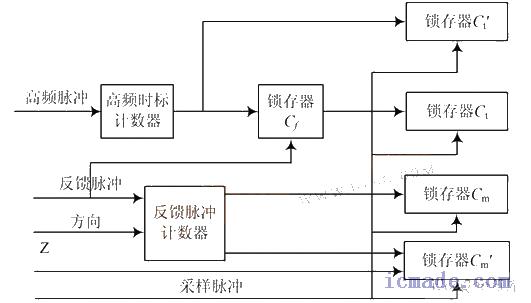

圖3 展示了改進(jìn)M/ T 法的電路原理,這是實(shí)現(xiàn)高精度的硬件基礎(chǔ)。圖4 為改進(jìn)M/ T 法的時(shí)序圖。

圖3 改進(jìn)M/ T 法電路原理圖。

圖4 改進(jìn)M/ T 法時(shí)序圖。

對圖3 及其時(shí)序圖4 的分析可以看出: 本測速電路在每個(gè)反饋脈沖時(shí)鎖存高頻時(shí)鐘的計(jì)數(shù)值,兩個(gè)采樣周期間的高頻時(shí)標(biāo)增量值Ct 實(shí)際表示為T 2 前一個(gè)反饋脈沖上升沿到T4 前一個(gè)反饋脈沖上升沿的高頻時(shí)標(biāo)增量,而在采樣周期內(nèi)每個(gè)反饋脈沖到來都對反饋脈沖計(jì)數(shù)器計(jì)數(shù),兩個(gè)采樣脈沖采得反饋脈沖增量值Cm 實(shí)際表示為T 1 ~ T 3 之間的反饋脈沖增量值,位置的反饋脈沖增量值Cm‘ 則是在C m 的基礎(chǔ)上考慮方向得到的,那么結(jié)合32 位浮點(diǎn)運(yùn)算,這種測速方法就解決了采樣時(shí)機(jī)不確定的缺點(diǎn)。

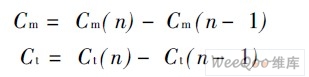

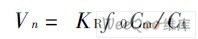

根據(jù)上述分析,通過差分處理就可得到當(dāng)前實(shí)際采樣間隔內(nèi)的反饋脈沖增量值Cm 和高頻時(shí)標(biāo)增量值Ct :

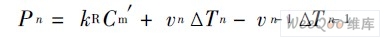

這樣得到的速度是當(dāng)前實(shí)際采樣間隔內(nèi)的平均速度:

式中: K R 為反饋信號脈沖當(dāng)量; f 0 為高頻時(shí)標(biāo)頻率。

在實(shí)際采樣點(diǎn)T 2 處,高頻時(shí)標(biāo)信號f 0 的邊沿不能總與反饋脈沖信號plus 的邊沿保持一致,因而會(huì)產(chǎn)生? 1 個(gè)高頻時(shí)標(biāo)當(dāng)量的計(jì)數(shù)誤差,從而影響這種測速算法的測速精度。因此高精度數(shù)字測速算法的測速相對誤差為:

動(dòng)態(tài)位置算法不僅關(guān)注已經(jīng)發(fā)生的反饋脈沖數(shù)量,也關(guān)注反饋脈沖的發(fā)生時(shí)刻,其硬件基礎(chǔ)是依據(jù)圖3 所示邏輯電路的。根據(jù)當(dāng)前有效采樣周期的定周期采樣點(diǎn)和實(shí)際采樣點(diǎn)之間的時(shí)間差:

并根據(jù)改進(jìn)的M/ T 法得到被測對象的平均速度v n ,由vn 和 T n 相乘就可以計(jì)算出時(shí)間差 T ( n) 中所包含的動(dòng)態(tài)位置信息,因此由當(dāng)前有效采樣周期內(nèi)的增量式高精度動(dòng)態(tài)位置信息可以得出位置量:

可根據(jù)這種方法完成測位置的功能。

2 各個(gè)模塊VHDL 實(shí)現(xiàn)

根據(jù)圖1 的總體設(shè)計(jì)方案,使用VHDL 語言設(shè)計(jì)實(shí)現(xiàn)如下幾個(gè)模塊。

2. 1 倍頻辨向模塊

為便于使用VHDL 語言描述,對圖2 的碼盤信號作如下分析:

( 1) 當(dāng)碼盤正轉(zhuǎn)時(shí),在一個(gè)周期T 內(nèi),A,B 兩相信號共有4 次相對變化: 00 → 10 → 11 → 01。這樣,根據(jù)前一次和當(dāng)前的信號,就可以判斷方向,并產(chǎn)生四倍頻脈沖。

( 2) 同理當(dāng)碼盤反轉(zhuǎn)時(shí),也根據(jù)A,B 兩相信號的4 次相對變化: 00 →01 →11 →10,可以判斷方向,并產(chǎn)生四倍頻脈沖信號。

( 3) 當(dāng)線路受到干擾或出現(xiàn)故障時(shí),則可能出現(xiàn)其他狀態(tài)轉(zhuǎn)換過程,此時(shí)不產(chǎn)生脈沖。

根據(jù)上述分析就可以設(shè)計(jì)出測速辨向模塊,當(dāng)判斷正轉(zhuǎn)時(shí),把方向輸出置“1” ,反向時(shí)置“0”。

2. 2 改進(jìn)M/ T 法測速模塊

如圖3 所示可以看出,本部分的VHDL 設(shè)計(jì)分成兩個(gè)模塊: 計(jì)數(shù)器模塊與鎖存器模塊。

其中,計(jì)數(shù)器模塊分為兩種: 高頻時(shí)標(biāo)計(jì)數(shù)器和反饋脈沖計(jì)數(shù)器。高頻時(shí)標(biāo)計(jì)數(shù)器在每個(gè)高頻時(shí)標(biāo)的上升沿都做+ 1 計(jì)數(shù),在每個(gè)反饋脈沖的上升沿對計(jì)數(shù)值鎖存。反饋脈沖計(jì)數(shù)器,需要兩個(gè)輸出: 反饋脈沖計(jì)數(shù)值Cm 、位置反饋脈沖計(jì)數(shù)值Cm’。其中,Cm 的增量值用于速度的計(jì)算,所以在每一個(gè)反饋脈沖到來時(shí),計(jì)數(shù)器都+ 1; Cm‘的計(jì)數(shù)值用于位置的計(jì)算,所以它是在Cm的基礎(chǔ)上考慮了碼盤方向得到的計(jì)數(shù)值,在正轉(zhuǎn)時(shí)反饋脈沖計(jì)數(shù)器+ 1,反轉(zhuǎn)時(shí)- 1,當(dāng)零位脈沖Z有效時(shí),對其置0。然后分別輸出Cm ,Cm’,由此就可以得到反饋脈沖計(jì)數(shù)器模塊。

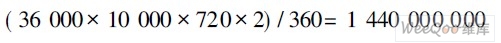

在每個(gè)采樣周期的上升沿還要鎖存Cm,Ct 的增量值和Ct‘ 與Ct 的差值,由于都做了差分處理,所以這三個(gè)鎖存器使用雙字就能滿足設(shè)計(jì)要求,而Cm’鎖存器在零位信號Z 后不進(jìn)行差分處理,若采用36 000 刻增量式碼盤,并進(jìn)行10 000 倍頻,位置范圍為±720°,那么需要的最大計(jì)數(shù)值為:

可見,雙字鎖存器也能滿足設(shè)計(jì)要求。

綜上所述,本設(shè)計(jì)設(shè)置了4 個(gè)雙字信號鎖存器Cm ,Cm’,Ct ,Ct‘,同時(shí)還需要對其控制輸出,所以在PCI 從設(shè)備控制器中為I/ O 分配4 個(gè)雙字的地址空間。然后根據(jù)PCI 總線給出的地址信號PCI_AD[ 3: 2] 和數(shù)據(jù)輸出使能信號DATA _ EN 對這4 個(gè)雙字寄存器尋址輸出。

2. 3 PCI 接口控制器

PCI 的時(shí)序規(guī)則和PCI 的總線協(xié)議由PCI 接口控制器實(shí)現(xiàn),同時(shí)它還負(fù)責(zé)傳遞地址和數(shù)據(jù)輸出使能信號給測速模塊,實(shí)現(xiàn)I/ O 口的基本讀與猝發(fā)讀數(shù)據(jù)功能。

從設(shè)備控制器包括2 個(gè)部分: 奇偶校驗(yàn)?zāi)K和PCI從設(shè)備狀態(tài)機(jī)。

2. 3. 1 奇偶校驗(yàn)?zāi)K

PCI 的奇偶校驗(yàn)提供了一種機(jī)制來決定一件作業(yè)。

該作業(yè)判斷主設(shè)備是否成功地尋址相應(yīng)的從設(shè)備,且數(shù)據(jù)是否正確地在它們之間傳輸。通過該模塊完成數(shù)據(jù)傳輸過程中PCI _AD 和PCI _CBE 的偶校驗(yàn)。偶校驗(yàn)的輸出信號在地址和數(shù)據(jù)周期有效,其產(chǎn)生的規(guī)則是使偶校驗(yàn)輸出、PCI_CBE、PCI_AD 各位的“1”的個(gè)數(shù)為偶數(shù)。那么采用把PCI_AD 與PCI_CBE 各位異或的方法,就可以實(shí)現(xiàn)偶校驗(yàn)的功能。

2. 3. 2 PCI 從設(shè)備狀態(tài)機(jī)

PCI 從設(shè)備控制器是PCI 接口設(shè)計(jì)的核心模塊,按功能來說,它要產(chǎn)生奇偶校驗(yàn)和數(shù)據(jù)的使能信號,并根據(jù)PCI_AD 和PCI_CBE 產(chǎn)生讀地址,完成主從設(shè)備的握手信號,并且實(shí)現(xiàn)從設(shè)備狀態(tài)機(jī)在各個(gè)狀態(tài)之間的轉(zhuǎn)換。

由于本設(shè)計(jì)只需要完成I/ O 讀操作,本狀態(tài)機(jī)設(shè)計(jì)配置空間的功能放在了從設(shè)備控制器來完成,同時(shí)刪去了PCI 操作中對存儲器空間、配置空間的操作,結(jié)合PCI 總線的傳輸時(shí)序,如圖5 給出了其基本結(jié)構(gòu)。

( 1) 空閑狀態(tài)為PCI 從設(shè)備的初始狀態(tài),在沒有任何操作的時(shí)候,PCI 從設(shè)備將始終保持這個(gè)狀態(tài);( 2) 每次數(shù)據(jù)傳輸時(shí)首先傳出地址和命令字,根據(jù)地址和命令字確定是不是對本設(shè)備的訪問,并確定訪問的首地址; 從設(shè)備則從命令字中識別該訪問是讀操作還是寫操作;( 3) 讀訪問只有在信號IRDY,TRDY,DEVSEL都為低狀態(tài)時(shí)才能進(jìn)行;( 4) 猝發(fā)傳輸需要通過地址遞增邏輯來實(shí)現(xiàn)地址的自動(dòng)遞加,其地址遞增的周期為數(shù)據(jù)周期和最后傳輸周期總和,在等待周期暫停遞增;( 5) 主從設(shè)備中任一方?jīng)]有準(zhǔn)備好,操作中都需要能夠引起等待狀態(tài)插入的活動(dòng);( 6) 讀操作還有一個(gè)中間準(zhǔn)備過程。

圖5 讀狀態(tài)機(jī)結(jié)構(gòu)。

那么完成本狀態(tài)機(jī)需要6 個(gè)狀態(tài): idle 表示空閑狀態(tài); addr 表示地址周期; tur nad 表示讀轉(zhuǎn)換周期; data表示數(shù)據(jù)傳輸周期; laST t ra 表示最后傳輸周期; wait 表示等待周期; 在各個(gè)狀態(tài)到來時(shí)還要對中間信號、輸出信號和本地信號執(zhí)行相應(yīng)的操作:

( 1) idle,addr,turnad 周期對PCI_TRDYn 和PCI_DEVSELn 置高電平; addr 周期依據(jù)地址信號確定是否選中本機(jī),識別是否為讀操作; addr 周期輸出PCI _AD[ 3: 2] 對寄存器進(jìn)行尋址,實(shí)現(xiàn)讀操作。

( 2) data,lastt ra 周期對PCI _ T RDYn 和PCI _DEVSELn 置低電平; data,last t ra 周期置DAT A _EN有效并輸出。

( 3) addr ,data,last t ra 周期置奇偶校驗(yàn)有效。

( 4) 等待周期置PCI _TRDYn 和PCI_ DEVSELn低電平。

根據(jù)對PCI 總線傳輸時(shí)序的分析,影響各個(gè)狀態(tài)相互轉(zhuǎn)化的因素是: 幀同步信號PCI _FRAMEn、主設(shè)備準(zhǔn)備好信號PCI _IRDYn、讀識別信號READn。其中,READn 用來標(biāo)識狀態(tài)addr 產(chǎn)生的中間識別信號。

3 測試平臺與仿真測試

這種改進(jìn)M/ T 數(shù)字測速及位置檢測算法的硬件采用Xilinx 公司的FPGA XC3S400。使用36 000 刻的增量式碼盤,速度環(huán)采樣周期T 設(shè)定為1 ms,高頻時(shí)標(biāo)信號的頻率為40 MHz,結(jié)合PC 運(yùn)算的數(shù)字測速算法可以在速度0. 001~ 150(?) / s 的范圍內(nèi)獲得? 2. 5 (10- 5 s 的測速精度。與此同時(shí),高精度動(dòng)態(tài)位置檢測算法可以使位置反饋的動(dòng)態(tài)測量分辨率提高到10- 2 ~10- 5個(gè)脈沖當(dāng)量。

對編寫好的VHDL 程序采用ISE 進(jìn)行綜合,并編寫測試平臺,用ModelSim 對其進(jìn)行仿真測試。圖6 為PCI 控制器的仿真圖,圖中state 表示狀態(tài)機(jī)在內(nèi)部轉(zhuǎn)換的過程,狀態(tài)1 表示空閑狀態(tài),狀態(tài)2 表示地址周期,狀態(tài)4 表示讀轉(zhuǎn)換周期,狀態(tài)8 表示最后傳輸周期,狀態(tài)9 表示猝發(fā)讀寫周期。

圖6 I/ O 讀操作。

該I/ O 讀操作,將地址為1 的寄存器讀出。這里設(shè)定I/ O 地址為0X200~ 0X20F 這4 個(gè)雙字空間,那么在地址周期中地址0X204 的2~ 3 位尋址于寄存器的第一個(gè)雙字,其后緊跟的是讀的轉(zhuǎn)換周期,猝發(fā)讀寫周期和最后一位讀寫周期。可以看出,這兩個(gè)周期都對這個(gè)寄存器進(jìn)行了讀操作。

4 結(jié) 語

本文介紹了使用FPGA 設(shè)計(jì)和實(shí)現(xiàn)基于PCI 總線傳輸?shù)母倪M(jìn)型M/ T 法測速電路,它克服了經(jīng)典測速方法的幾個(gè)缺點(diǎn),在較大速度范圍內(nèi)都具有良好的精度。

同時(shí)使用FPGA 設(shè)計(jì)和實(shí)現(xiàn)了PCI 從設(shè)備控制器,使得測速電路的設(shè)計(jì)與PCI 總線的設(shè)計(jì)成為一個(gè)整體,節(jié)省了板上器件,也使得整個(gè)設(shè)計(jì)信號在FPGA 內(nèi)部流動(dòng),具有更加良好的抗干擾能力和穩(wěn)定性。