目前,圖像監(jiān)控系統(tǒng)大多采用PC和視頻采集卡作為系統(tǒng)主要部分,基于嵌入式技術(shù)的圖像監(jiān)控系統(tǒng)設(shè)備在我國(guó)還只是起步階 段,沒有成熟的產(chǎn)品應(yīng)用。這一現(xiàn)狀的根本原因就是我國(guó)在開發(fā)這類產(chǎn)品時(shí),沒有統(tǒng)一的開發(fā)標(biāo)準(zhǔn)和共用的開發(fā)平臺(tái),而且沒有可靠的功能和性能測(cè)試標(biāo)準(zhǔn),各個(gè)企 業(yè)的開發(fā)技術(shù)力量分散,極大的影響了該類產(chǎn)品開發(fā)的效率和可靠性。而制造出來的產(chǎn)品同國(guó)外同類產(chǎn)品相比,功能相差太大,沒有競(jìng)爭(zhēng)力,市場(chǎng)基本上被國(guó)外公司 所占領(lǐng)。因此,開發(fā)一個(gè)該類嵌入式系統(tǒng)勢(shì)在必行。

系統(tǒng)總體方案

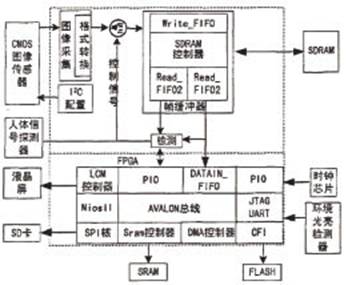

為了實(shí)現(xiàn)自動(dòng)圖像報(bào)警和圖像采集,本文設(shè)計(jì)了動(dòng)體檢測(cè)算法,這是因?yàn)榻^大多數(shù)情況下我們只對(duì)監(jiān)控區(qū)域中運(yùn)動(dòng)的物體感興 趣,這樣可以過濾掉只包含靜態(tài)背景的圖像,從而降低了對(duì)有限的嵌入式硬件資源的消耗。由于活動(dòng)物體大多是人,而且這也是圖像監(jiān)控的目標(biāo),為此加入了人體信 號(hào)探測(cè)器,用以輔助動(dòng)體檢測(cè),以達(dá)到降低圖像報(bào)警誤報(bào)率的目的。本系統(tǒng)主要集成了圖像采集、控制和存儲(chǔ)等器件或芯片,組成了以FPGA為控制核心的實(shí)時(shí)圖 像監(jiān)控系統(tǒng)。系統(tǒng)的總體方案如圖1所示。

圖1 圖像監(jiān)控系統(tǒng)結(jié)構(gòu)圖

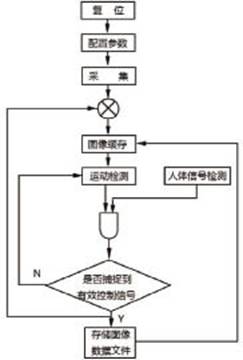

系統(tǒng)工作流程為:系統(tǒng)上電后,F(xiàn)PGA從外部EEPROM自動(dòng)加載程序,I2C模塊對(duì)CIS進(jìn)行初始化工作參數(shù)配置。 CIS向FPGA輸入圖像數(shù)據(jù)信號(hào),F(xiàn)PGA將采集的原始數(shù)據(jù)(RAW)轉(zhuǎn)換成RGB格式,幀緩沖模塊(Frame Buffer)每次將相鄰兩幀圖像數(shù)據(jù)寫入SDRAM,然后比較這兩幀圖像的差值,如果差值大于設(shè)定的閾值,并且人體探測(cè)器輸出高電平,就認(rèn)為檢測(cè)到了外 界場(chǎng)景的運(yùn)動(dòng),系統(tǒng)會(huì)自動(dòng)將捕獲的圖像輸出到SD卡進(jìn)行存儲(chǔ)。圖2給出了系統(tǒng)的工作流程。

圖2 系統(tǒng)工作流程圖

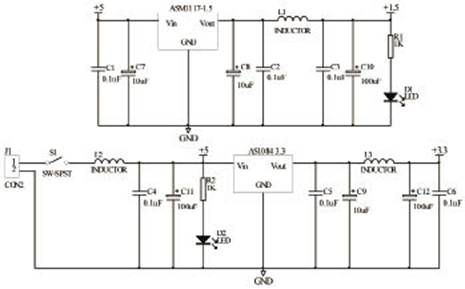

圖3 電源電路原理圖

系統(tǒng)硬件設(shè)計(jì)與實(shí)現(xiàn)

圖像監(jiān)控系統(tǒng)處理的數(shù)據(jù)量較大,同時(shí)還要滿足實(shí)時(shí)性要求,因此板載電路需要選用容量較大,速度較快的器件。本系統(tǒng)采集的 一幀圖像分辨率大小為640×480,色深是24位,檢測(cè)時(shí)需要在SDRAM緩存兩幀,因此SDRAM的容量必須大于1.8M字節(jié) (640×480×3×2=1843200字節(jié)),由于每個(gè)像素位寬為24位,同時(shí)NIOS是32位的處理器,所以SDRAM的位寬最好是32位。外部提 供給FPGA的晶振頻率必須大于CIS的像素時(shí)鐘25MHz。考慮到檢測(cè)算法需要較多的邏輯資源,因此FPGA的片內(nèi)LE要很豐富,另外FPGA的管腳必 須要滿足外部器件連接的要求,在本系統(tǒng)中要實(shí)現(xiàn)所有器件的I/O口相連,F(xiàn)PGA的I/O管腳必須大于150個(gè)。由于電路原理圖較多,這里只給出其中的一 部分。

主控制芯片電路

本系統(tǒng)選用的Cyclone系列FPGA器件的具體型號(hào)是EPlCl2Q240C8。邏輯資源達(dá)12060個(gè)邏輯單元 (LE,Logic Elements),片內(nèi)RAM的容量為239616bits。完全可以滿足圖像采集的設(shè)計(jì)要求。其內(nèi)核供電采用1.5V、0.13um工藝,功耗較低。 Cyclone器件支持各種單端I/O接口標(biāo)準(zhǔn),如3.3V、2.5V、1.8V、LVTTL、LVCMOS、SSTL。Cyclone器件具有兩個(gè)可編 程鎖相環(huán)(PLL)和八個(gè)全局時(shí)鐘線,提供健全的時(shí)鐘管理和頻率合成功能,實(shí)現(xiàn)最大的系統(tǒng)性能。Cyclone器件具有高級(jí)外部存儲(chǔ)器接口,允許設(shè)計(jì)者將 外部單數(shù)據(jù)率(SDR)SDRAM,雙數(shù)據(jù)率(DDR)、SDRAM和DDR FCRAM器件集成到復(fù)雜系統(tǒng)設(shè)計(jì)中,而不會(huì)降低數(shù)據(jù)訪問的性能。Cyclone系列FPGA器件基于一種全新的低成本架構(gòu),從設(shè)計(jì)之初就充分考慮了成本 的節(jié)省,因此可以為價(jià)格敏感的應(yīng)用提供全新的可編程的解決方案。