隨著手機(jī)及其他便攜手持裝置的功能不斷增加,設(shè)計(jì)的取舍平衡亦日趨精細(xì)。文本信息與網(wǎng)絡(luò)瀏覽等流行功能都要求更多的數(shù)據(jù)輸入,而這對(duì)于傳統(tǒng)的雙音多頻 (DTMF) (0-9, #, *) 鍵盤會(huì)比較困難。使用這種鍵盤要求多端數(shù)據(jù)輸入,輸入效率低而且容易出錯(cuò)。

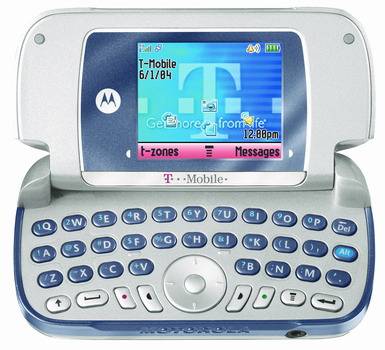

圖 1 – QWERTY 鍵盤(摩托羅拉 A630)

使文本輸入更為方便的一個(gè)方法是使用 QWERTY 鍵盤(見(jiàn)圖 1)。這種鍵盤采用 40 個(gè)或更多按鍵,而 DTMF 手機(jī)通常采用 12 個(gè)。當(dāng)然,多出的按鍵會(huì)使手機(jī)體積變大,用到的電子組件也更多。

然而,文本信息用戶可能樂(lè)意以體積換取 QWERTY 鍵盤,因?yàn)槲谋据斎氪鬄楹?jiǎn)便了,而且兩個(gè)大拇指都可以用來(lái)輸入文本信息或數(shù)據(jù)。最近,有些手機(jī)生產(chǎn)商已經(jīng)推出了面向文本用戶的帶 QWERTY 鍵盤的手機(jī)。

數(shù)據(jù)輸入鍵盤可以用多種方法來(lái)設(shè)計(jì),并無(wú)一定之規(guī)。為傳統(tǒng) DTMF 鍵盤添加更多按鍵對(duì)設(shè)計(jì)人員提出了挑戰(zhàn),本文即討論應(yīng)對(duì)這挑戰(zhàn)的一種可能解決方案。

QWERTY 構(gòu)建模塊

我們的解決方案使用 Xilinx® CoolRunner™-II CPLD" target="_blank">CPLD;低功耗、小包裝及低成本的特點(diǎn)使其成為此應(yīng)用的理想選擇。

將 DTMF 轉(zhuǎn)化為 QWERTY 鍵盤需要更多按鍵,從而需要更多通用 I/O (GPIO" target="_blank">GPIO)。例如,DTMF 鍵盤可能只有四行三列,而 QWERTY 鍵盤可能有多至八行八列。不過(guò),鍵盤的大小可根據(jù)終端系統(tǒng)的需求而定。

通常,將處理器或 DSP 用作連接鍵盤行和列的界面(見(jiàn)圖 2)。處理器對(duì)行進(jìn)行掃描,對(duì)列進(jìn)行監(jiān)控,以檢測(cè)邏輯變化。當(dāng)變化發(fā)生,即表示用戶按下了一個(gè)按鍵。知道被掃描的是哪一行,以及哪一列的狀態(tài)發(fā)生了變化,處理器即可推斷出按下的是哪個(gè)按鍵。

擴(kuò)展 I/O

設(shè)計(jì)需要更多 I/O 的鍵盤時(shí)(QWERTY 鍵盤即為一例),可能會(huì)發(fā)現(xiàn)現(xiàn)有處理器沒(méi)有足夠的 GPIO。一種可能的解決方法是,把一個(gè) CPLD 用作 I/O 擴(kuò)展器,從而減少對(duì)處理器 I/O 數(shù)量的要求。

圖 3 在處理器與鍵盤之間使用了一個(gè) CPLD,其一側(cè)連接鍵盤的行/列,另一側(cè)連接處理器的可用 GPIO。此例中,使用一個(gè) CPLD 后,一個(gè) 8 x 8 的鍵盤所需要的處理器 GPIO 端口的數(shù)目與 4 x 4 的鍵盤相同(實(shí)際上還少一個(gè))。如果不使用 CPLD,處理器會(huì)需要 16 個(gè) GPIO 端口,而不是 7 個(gè)。

掃描與編碼

除了減少處理器對(duì) GPIO 的數(shù)量要求外,CPLD 還可以承擔(dān)處理器的某些功能,如:對(duì)行進(jìn)行掃描并對(duì)列進(jìn)行監(jiān)控以檢測(cè)狀態(tài)變化。當(dāng)用戶按鍵時(shí),CPLD 會(huì)停止掃描,并立即生成一個(gè)編碼字,然后發(fā)送給處理器,告訴處理器哪個(gè)鍵按下了。因?yàn)槭褂昧司幋a字來(lái)告知處理器按下了哪個(gè)按鍵,對(duì)處理器的 I/O 需求得以減輕。

圖 3 – 使用 CoolRunner-II CPLD 擴(kuò)展 GPIO

在圖 3 所示例子中,用 6 個(gè)位來(lái)代表編碼字。6 個(gè)位提供 26(即 64)個(gè)不同的值,每個(gè)值代表一個(gè)按鍵。然而,還必須有一個(gè)值代表無(wú)按鍵被按時(shí)的狀態(tài)。因此,在此例中,在不添加又一個(gè) GPIO 的情況下,實(shí)際上只有 63 個(gè)按鍵可被代表。

處理器無(wú)需掃描鍵盤,因?yàn)檫@一操作現(xiàn)由 CPLD 執(zhí)行;不過(guò),處理器仍需監(jiān)控其 GPIO 上的變化 – 它只是不再需要推斷哪個(gè)按鍵被按,因?yàn)樵撔畔⒕幋a到一個(gè)六位字中了。

還需要用到的是開(kāi)關(guān)抖動(dòng),這可以安排在 CPLD 中或處理器中,取決于哪個(gè)裝置有可用資源。在處理器中進(jìn)行這一操作,可將 CPLD 的大小和成本降到最小。

簡(jiǎn)要總結(jié)此設(shè)計(jì)示例:CPLD 對(duì)鍵盤進(jìn)行掃描,檢測(cè)被按下的按鍵,然后提供一個(gè)編碼字供處理器讀取并解析。這一功能不僅使處理器不必再承擔(dān)掃描任務(wù),還擴(kuò)展了 GPIO 的功能。

此設(shè)計(jì)非常適合于 CoolRunner-II 32 宏單元裝置(利用率大約為 75%),留下 25% 空間作他用。此外,此設(shè)計(jì)還采用了其他一些方法來(lái)減少功耗并利用 CoolRunner-II 的節(jié)能功能。

CPLD 設(shè)計(jì)詳述

要掃描鍵盤的行,桶式移位寄存器除一位預(yù)置為零外,其他所有位均預(yù)置為 1。移位寄存器的每一位驅(qū)動(dòng) CPLD 上的一個(gè)輸出引腳,后者與鍵盤的行相連。當(dāng)移位寄存器開(kāi)始計(jì)時(shí)時(shí),零位通過(guò)桶式移位器移位,將行逐行置低,以對(duì)其進(jìn)行掃描。鍵盤的列輸入到 CPLD,每個(gè)輸入都通過(guò)一個(gè)內(nèi)部上拉電阻上拉。

當(dāng)沒(méi)有按鍵被按時(shí),CPLD 的所有列輸入都被動(dòng)上拉至邏輯高位。對(duì)所有的列輸入一起進(jìn)行“與”操作,這時(shí)輸出端的邏輯 1 表示沒(méi)有按鍵被按。

“與”操作的輸出用于啟動(dòng)移位寄存器。當(dāng)按鍵被按下時(shí),列與行取得連接,按下的鍵所在的列被與該按鍵相關(guān)的行置低。“與”操作的輸出將變?yōu)榱悖瑥亩诎存I被按下時(shí)中止移位寄存器。

|

圖 4 – 模塊圖 |

此時(shí),移位寄存器將按下的鍵所在的行置低,而該鍵所在的列亦處于低位。為了使這些信息相關(guān)聯(lián),使用了兩個(gè)編碼器:一個(gè)用于行位(移位寄存器的輸出),另一個(gè)用于列輸入。兩個(gè)編碼器的輸出組合起來(lái),就構(gòu)成發(fā)送給處理器的編碼字。圖 4 為這一操作的模塊圖。

結(jié)束語(yǔ)

使用 Xilinx CoolRunner-II CPLD,獲得的是靈動(dòng)的設(shè)計(jì)與低功耗。除了 I/O 擴(kuò)展之外,CPLD 還可以加入其他“粘合”功能,如:電壓轉(zhuǎn)換、I/O 標(biāo)準(zhǔn)轉(zhuǎn)換與輸入滯后。

由于 CPLD 為可編程,您可以將同一裝置用于不同的鍵盤和產(chǎn)品,而收高產(chǎn)量低成本之效。可再編程的特點(diǎn)輔之以簡(jiǎn)便易用的設(shè)計(jì)工具,使您可以對(duì)設(shè)計(jì)進(jìn)行晚期更改,降低風(fēng)險(xiǎn)。

要了解此應(yīng)用的詳情,請(qǐng)參閱 Xilinx 應(yīng)用說(shuō)明,“使用 CoolRunner-II 實(shí)現(xiàn)鍵盤掃描器”,網(wǎng)址為 www.xilinx.com/bvdocs/appnotes/xapp512.pdf。有關(guān) Xilinx CPLD 的詳情,請(qǐng)?jiān)L問(wèn) www.xilinx.com/cn/cpld/。

作者:Mike Gulotta Xilinx FAE Xilinx, Inc. [email protected]